Спеціальність: Системне програмування

Тема магістерської роботи:

"Розробка та дослідження методів тестування FPGA-пристрої з використанням технології Boundary-Scan"

Науковий керівник: Зінченко Юрій Євгенович

Реферат за темою

"Розробка та дослідження методів тестування FPGA-пристрої з використанням технології Boundary-Scan"

Вступ

З часів появи інтегральних схем (ІС) у США 1959р. виникла проблема їх діагностики не тільки в процесі експлуатації, але і на етапі безпосередньо розробки. При тому, як ІС постійно вдосконалювалися й ускладнювалися, вони вимагали до себе большевніманія з боку пошуку в них несправностей. З появою ВІС і НВІС схеми з тисячами логічних елементів стали розміщуватися на одному кристалі, тому доступу до схем для контактного діагностики ставало менше.

Практична новизна

Розглянуто механізм Boundary - Scan, який відповідає цифровому стандарту IEEE 1149.1 для тестування БІС і НВІС. Представлений короткий огляд програмно-апарати комплексів деяких фірм, призначених для тестування інтегральних схем, що підтримують технологію Boundary - Scan.

Загальна постановка задачі

Функціональне тестування з'явилося найпершим. На зорі електронної промисловості більшість систем просто збиралося, а потім підключався харчування. Тест здійснювався шляхом перевірки працездатності виробу. Постійне збільшення складності виробів роблять процес підготовки функціонального тесту нескінченно довгим. Діагностування несправностей, виявлених у процесі функціонального тестування, може бути досить складним, що вимагає залучення кваліфікованих фахівців. Тому перед тестом системи в цілому часто здійснюється тестування на рівні окремих плат. Тест плат може бути здійснений і на функціональному рівні, але поділ робить діагностування несправностей і підготовку тестів більш гнучкими. Швидко зростаюча складність інтегральних мікросхем викликає схожі проблеми з функціональним тестуванням на рівні плат, так само як і в системному тестуванні - довгий час підготовки тестів, неточне тестове покриття, слабка діагностика.

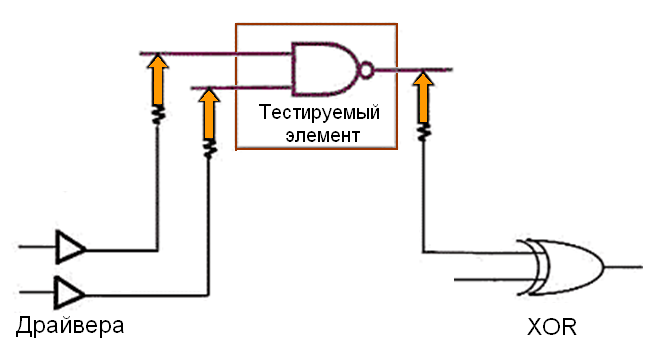

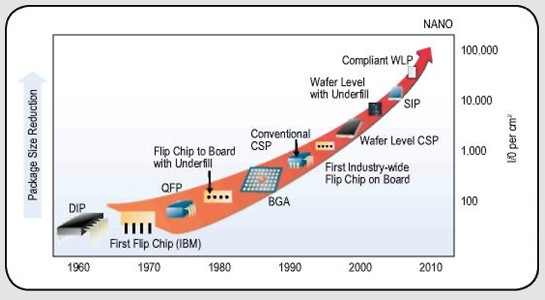

Наступний широко поширений метод тестування - це внутрішньосхемного тестування (In-Circuit Test, ICT). Цей метод дозволяє знаходити дефекти і помилки монтажу шляхом забезпечення прямого електричного доступу до компонентів на платі через адаптер голчастого типу (рисунок 1). Внутрішньосхемного тестування ідеально підходило для DIP-компонентів і технології штирьовий монтажу. Але у зв'язку з появою багатошарових друкованих плат і більш складних корпусів мікросхем, таких як QFP, BGA, CSP і т.д., тестовий доступ став сильно обмежений. Технологія внутрішньосхемного тестування не може розвиватися так само швидко, як мініатюризація розмірів компонентів і виробів.

Рисунок 1 - приклад внутрішньосхемного тестування

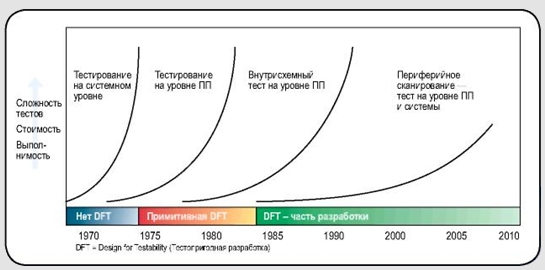

Електронна індустрія передбачила ці проблеми заздалегідь, тому був розроблений метод периферійного сканування, закріплений стандартом IEEE 1149.1, який описує порт тестового доступу (TAP - Test Access Port) і архітектуру периферійного сканування. Метою створення даного стандарту було подолання недоліків інших методів тестування (рисунок 2).

Рисунок 2 - Зростання важливості стратегії тестопрігодной розробки виробів

Дивлячись на еволюцію тестових методів (рисунок 3) можна зробити наступні спостереження:

-

Розробка тестопрігодних виробів (Design-For-Test, DFT) стає все більш і більш необхідним доповненням функціонального тестування, дозволяючи зробити контроль більш повним і інформативним. Для того щоб виробляти і тестувати сучасні передові розробки, тестопрігодность необхідна.

-

Спочатку, тестування було похідної процесу налагодження нової розробки і пошуку дефектів монтажу. Через зростання складності схем пристроїв керованість цими процесами могла бути підвищена тільки при роздільному їх проведенні. Виявлення і виправлення виробничих дефектів на стадії налагодження дослідних зразків стало необхідністю.

-

Зі зростанням складності продукції багато виробників почали застосовувати багатоступеневу стратегію тестування, метою застосування якої є як можна більш раннє виявлення і виправлення помилок виробничого процесу.

Рисунок 3 - Еволюція ІС

Перша версія стандарту тестування пристроїв з обмеженим доступом до висновків інтегральної схеми (надалі ІС) - Boundary-Scan, з'явилася спочатку 1990 року, і отримала ім'я, яке збереглося і сьогодні - IEEE 1149.1. Стандарт цієї технологія також називається Test Access Port and Boundary-Scan Architecture (порт тестового доступу та архітектура граничного сканування). Проект був розроблений міжнародною групою експертів, яка носила назву JTAG (Joint Test Action Group - об'єднана група розробки методів тестування), тому стандарт технології граничного сканування більш відомий під назвою цієї абревіатури [4].

Сама архітектура цифрового стандарт Boundary-Scan не відрізняється особливою складністю, на відміну від своїх можливостей. Відповідно до стандарту IEEE 1149.1, так звана Boundary-Scan-ІС, повинна бути оснащена чотирма обов'язковими елементами:

- TAP-портом, який складають чотири обов'язкових сигналів, і п'ятий за розсуд розробників безпосередньо самої плати (TCK - контакт синхронізації роботи механізму Boundary-Scan; TMS - контакт вибору тестового режиму; TDI - контакт введення тестових даних; TDO - контакт виведення тестових даних ( знаходиться в постійно в третьому стані, окрім режиму зсуву); / TRST - контакт асинхронного скидання стану TAP-контролера (може зовсім не пресутствовать)).

- TAP-контролер виступає одним з важливих елементів управління всією роботи технології Boundary-Scan;

- IR (Instruktion Register від анг. - Регістр Команд) - перша група регістрів, в якій обов'язковим за стандартом повинен бути присутнім хоча б один Регістр Команд (РК);

- DR (Data Registers від анг. - Регістри Даних) - друга група регістрів, відповідно до стандарту зобов'язана в себе включати як мінімум два регістра: Регістр обходу (РВ, також його іноді називають Шунт-Регістр), Регістр Boundary-Scan.

Такий мінімальний комплект елементів вимагає стандарт IEEE 1149.1. Решта регістри, які можуть доповнити групу, як IR, так DR на розсуд розробників плат, також допускаються створеним стандартом [2] [3].

Для того, щоб отримати гарну тестове покриття, немає необхідності в тому, щоб всі компоненти на платі мали JTAG-інтерфейс. Наприклад, багато блоків, що складаються з не сканованих компонентів (кластеру), можуть тестуватися, незважаючи на відсутність прямого доступу для периферійного сканування. Насправді, існують практичні приклади, коли здійснюється контроль і детальне тестування абсолютно всієї плати (включаючи пам'ять) за допомогою одного або двох компонентів, що підтримують периферійне сканування.

На малюнку 4 зображена архітектура Boundary-Scan. На TAP-контролер подаються 2 (3) сигналу, за допомогою яких контролер встановлює відповідний режим роботи схеми. Сам TAP-контролер представляє собою автомат з кінцевим кількістю вершин. У цій статті його робота не буде детально розглядатися.

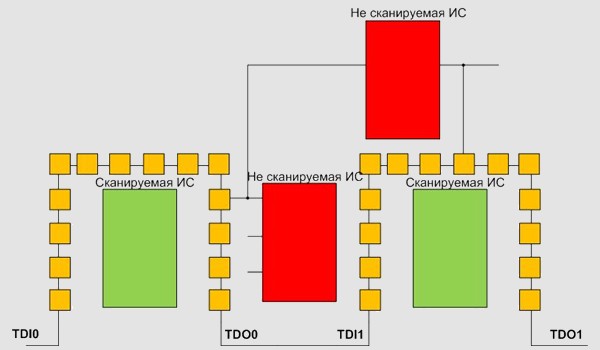

Основний принцип роботи Boundary-Scan полягає в тому, що навколо ІС на етапі розробки розташовуються комірки Boundary-Scan, з яких складається один з обов'язкових регістрів даних - Регістр Boundary-Scan. Осередки Boundary-Scan розташовані безпосередньо між зовнішніми висновками і функціональним ядром ІВ. ІС, оточені такою конструкцією називають відповідними стандарту IEEE 1149.1 і підлягають тестуванню за допомогою технології Boundary-Scan. Також необхідно, щоб кожен попередній тестовий вихід TDO з'єднувався з наступним тестовим входом TDI, т.ч. ланцюжок Регістрів Boundary-Scan всіх сканованих ІВ буде безперервної. Ідеальним варіантом є те, коли всі ІС, розташовані на платі, підтримують цей стандарт. Але якщо це так, то доводиться вдаватися до внутрішньосхемного тестування для тестування, так званих, не скануються ІВ.

Рисунок 4 - Анімація (15 кадрів, 7 циклів, 309 Кб). Архітектура технології Boundary-Scan

Одним з поширених підходів тестування подібних розглянутим платам (малюнок 5) є принцип «Розділяй і володарюй». [1] Тобто всі компоненти, розташовані на платі, розділяються на окремі острівці, які будуть окремо один від одного тестуватися. Чи не скануються ІС, зовнішні висновки яких з'єднані зі скануються, умовно відокремлюються і називаються кластерами. Сам же процес сканування починається перевірки цілісності самого шляху сканування, далі одним з етапів тестування може бути тестування з'єднань між ІВ і з'єднань з пам'яттю, потім тестуються кластеру, на які подаються тести, а з їх виходів фіксується реакція.

Рисунок 5 – Плата з не скануються ІС

Для максимального використання всіх привілеїв Boundary-Scan потрібно надійна розробка програмного забезпечення, а також допоміжне апаратне забезпечення.

Сьогодні на світовому ринку в цій області лідирують чотири представники США та Європи, які постачають програмно-апаратні комплекси (ASSET InterTech Inc. Та CORELIS Inc - США; GOEPEL Electronic - Німеччина; JTAG Technologies - Нідерланди). Такі розробки називаються BS-тестери. [1]

Ось низка програмно-апаратних комплексів, які заслуговують довіру своїх користувачів:

- ScanWorks фірми Asset InterTech

- ScanExpress фірми Corelis

- ProVision фірми JTAG Technologies

- onTAP фірми Flynn Systems

- XJTAG фірми XJTAG

- SourceWizard и ScanMaster фірми Acculogic

Відмінності між системами відносяться в засобах розробки тестів та їх налагодження, зручності та ефективності пошуку дефектів за результатами одержуваної діагностики несправностей, засобами аналізу рівня тестопрігодності та повноти покриття несправностей:

- автоматизація розробки тестів;

- способи інтегрованості графічного інтерфейсу користувача;

- сумісність інтерфейсу прикладного програмування з різними мовами програмування (С / С + +, Tcl / Tk, Perl, Visual Basic, J #);

- підтримка розташованих в інтернеті бібліотек тестових модулів.

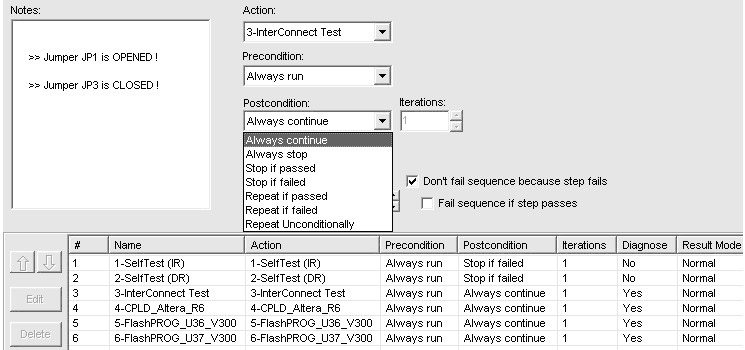

Програмно-апаратна система ScanWorks техаської фірми Asset InterTech завоювала собі величезну популярність, найбільшою мірою - у США і на Далекому Сході. Ця система має єдиний, інтегрований GUI, за допомогою якого здійснюється конфігурування її характеристик, вибір обмежень і параметрів тестів, вибір BS-команд контролера ТАР, пошук і адаптація застосовуваних моделей кластерів, ЗУ, флеш-пам'яті. Все, що потрібно тест-інженеру в процесі розробки тесту, його налагодження, прогону, отримання діагностичної інформації і пошуку дефектів досяжно за допомогою пов'язаних між собою вікон GUI.

Рисунок 6 – секвенсер ScanWorks

Програмно-апаратний комплекс підтримки BoundaryScan ScanExpress каліфорнійської фірми Corelis широко відома і застосовується при тестуванні електронних плат у США, Європі, Ізраїлі, Індії та на Далекому Сході. Конфігурування основних характеристик системи, вибір обмежень і параметрів тестів, вибір BS-команд контролерів ТАР, пошук і адаптація застосовуваних моделей кластерів, ЗУ здійснюється як з використанням GUI, так і редагуванням відповідних текстових файлів. GUI системи інтегрований частково.

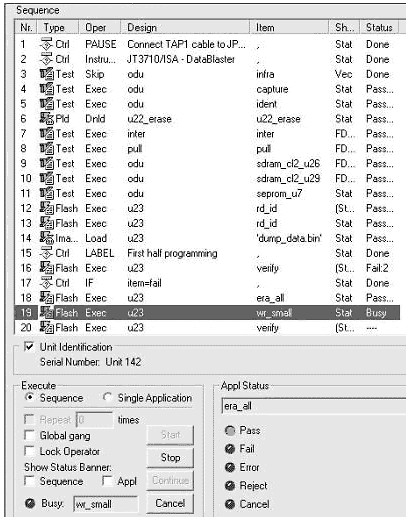

Програмно-апаратна система ProVision голландської фірми JTAGTechnologies являє собою інтегрований GUI, що супроводжує проект від завантаження списку ліній тестованої плати і файлів BSDL до генерації завантажуються в AEX Manager файлів APL для запуску результуючої тестової послідовності. Стандартний тест інфраструктури BS-ланцюжки генерується автоматично при генерації аплікацій для тестів межелементних зв'язків, а також тестів підтягуючою резисторів і резисторів, підключених «на масу». На додаток до цього, ProVision забезпечує генерацію аплікацій для тестування бібліотечних кластерів ЗУ і кластерів, визначених користувачем, а також генерацію програм пропалювання ІС флеш-пам'яті і процедур внутрішньосхемного програмування на основі файлів внутрішньосхемного програмування, імпортованих з інших систем.

Рисунок 7 – секвенсер AEX Manager

Система onTAP фірми Flynn Systems за короткий проміжок вирвалася на ринок гігантів і зайняла своє місце нарівні з ними. Ця система має відмінну сумісністю з іншими засобами для тестування, завдяки тому, що вихідний формат будь-якого тесту, що виходить з неї, має повсюдно використовується формат SVF.

Система onTAP має зручний графічний інтерфейс користувача. Навігація відбувається за допомогою п'яти кнопок управління (рисунок 8).

Рисунок 8 – П'ять основних кнопок управління

BS-тестер onTAP включає в себе всі необхідні кошти для граничного сканування, починаючи від розробки тестів до прогону тестів на виробничій лінії:

- система генерації тестів (Developer);

- секвенсер тестових етапів (Тest);

- браузер ліній схеми і контактів елементів (Nets);

- вікно налагодження тесту (Waveforms);

- вікно прогону тестів на виробничій лінії (Mfg Test).

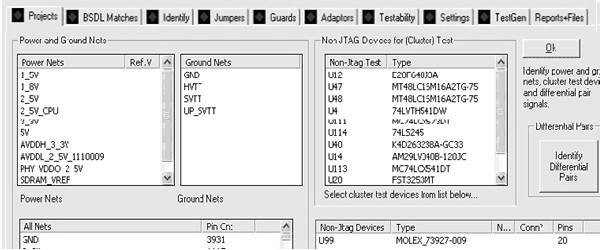

При натисканні на кнопку D (Developer) користувачеві відкривається вікно розробки тесту (рисунок 9). Система onTAP для розробки тесту пропонує створити проект, до якого буде потрібно тільки додати деякі файли з інформацією про тестованої платі, і саме основне, що потрібно від розробника тесту - це добре знання в області логіки роботи самого тестованого пристрою.

Рисунок 9 – Діалогове вікно розробки тесту

Перегортаючи по черзі вкладки, відбувається поетапна розробка тесту, якщо черговий етап правильно завершений, то крана іконка вгорі поруч з назвою подокна підсвічується зеленим кольором. Т.ч. система допомагає уникнути безліч помилок. Серед цих вкладок присутній браузер внутрішніх зв'язків, який дозволяє оголошувати лінії схеми живлення і землі. Це призводить до автоматичної сортування резисторів на підтягує резистори і резистори, підключені «на масу», а також на BS-прозорі резистори. Крім того, цей браузер дозволяє відібрати компоненти не пов'язані з граничного сканування, призначені для кластерного. У цьому ж вікні вибираються ІС ЗУ, призначені для тестування, а також ІС флеш-пам'яті і ЕСППЗУ.

У браузері Jumpers виконується зшивання вказують кілька ліній схеми в одну для випадків, не відображені в списку ліній тестованої плати. [2]

Браузер обмежень Guards - це дуже дружній інтерфейс вибору внутрішньосхемного обмежень і умов при розробці тестів. [2]

Компоненти, призначені для кластерного тестування, а також ІС ЗУ, флеш-пам'яті і ЕСППЗУ ставляться у відповідність своїм моделям на останній сторінці генерації тесту граничного сканування.

Відмінною особливістю системи onTAP є наявність у ній детально структурованого мови тестового програмування DTS (Digital Test Syntax). Цей С-образну мову програмування дозволяє маніпулювати змінними, функціями і конструкціями з груп контактів з метою розробки бібліотечних моделей для кластерного BS-тестування компонент, а також тестування ІС ЗУ і запису ІС флеш-пам'яті і ЕСППЗУ. Бібліотечні DTS-моделі найбільш застосовних компонент доступні через інтернет і можуть бути модифіковані відповідно до специфіки тестованої плати. [3]

Висновки

Boundary-Scan було винайдено для того, щоб подолати проблеми з обмеженим доступом, що виникають при використанні внутрішньосхемного тестування плат, виготовлених із застосуванням технології поверхневого монтажу.

Технологія Boundary-Scan цифрового стандарту IEEE 1149.1 легко завоювала своє місце в світі, продовжуючи при цьому активно розвинутися. Для сучасних великих інтегральних схем поки не знайдено способу діагностування з більш високим тестовим покриттям. Представлений у статті аналіз і порівняння програмно-апаратних комплексів для створення тестів, їх налагодження і безпосередньо тестування плат через інтерфейс JTAG, дає можливість цінувати основні переваги та недоліки наведеного програмного забезпечення.

Огляд набору інструментів у цій статті знайомить з поняттями, термінами і можливостями роботи механізму безконтактного тестування плат відповідних цифрового стандарту IEEE 1149.1.

Промислове тестування не є єдиним застосуванням послідовної шини сканування і TAP-порту. З-за простоти доступу з метою тестування і легкості розробки тестів Boundary-Scan часто і цілком успішно використовується для тестування дослідних зразків і виявлення виробничих дефектів.

На додаток до тестування, JTAG-інфраструктура може використовуватися також для програмування флеш-пам'яті і ПЛІС вже після збирання плати. Успішне програмування флеш вимагає доступ до шин адреси і даних, а також контрольним висновків мікросхеми пам'яті через осередки периферійного сканування.

Оскільки Boundary-Scan не потребує складному підході до себе і при наявності плати, відповідної JTAG-стандарту, застосування цієї технології не викликає ускладнень, то її не складе труднощів впровадити, як для вивчення студентами на кафедрі університету, так і для налагодження і тестування проектів , що розроблюються університетом.