|

Автореферат

Вступ та актуальність

В даний час практично не існує систем, що забезпечують подібно до цифрового тестування автоматичну побудову тестів для аналогових і аналого-цифрових (АЦ) пристроїв по їх структурному або функціональному опису. Існуючі системи покликані лише допомагати діагностові високої кваліфікації, так що тести будуються практично уручну виходячи з глибоких знань діагноста про схемотехніку і функції об'єкту діагностики (ОД). Проблема посилюється також тим, що тести, побудовані уручну, неефективні для промислового тестування АЦ-прістроїв на доступному тестовому обладненні і для адаптації до цього обладнення їх доводиться будувати заново, знову ж таки уручну. [2]

Традиційний підхід побудови тестів для АЦ-прістроїв базується на функціональному тестуванні на основі специфікацій ОД. При цьому зазвичай діагност передбачає, що в процесі діагностики буде доступна всіляка контрольно-діагностична апаратура (КДА). Велике число специфікацій, висока вартість КДА і вимоги високої кваліфікації, що пред'являються до персоналу, а також процес діагностування, зв'язаний з великим числом ручних операцій, приводять до низької міри автоматизації і кінець кінцем до високої дорожнечі традиційного підходу. Підвищення складності сучасних АЦ-прістроїв, викликане підвищенням міри інтеграції АЦ-ІС і складністю взаємодії їх аналогових і цифрових вузлів поряд із зменшенням співвідношення цієї складності до загального числа виводів АЦ-ІС, істотно посилює цю проблему і змушує учених і практиків-діагностів шукати нові підходи тестування АЦ-прістроїв.

Таким чином, бачимо, що завдання пошуку і усунення несправностей, аналогових і АЦ-пристроїв з кожним днем стає усе більш жаданою. Тому тема даної магістерської роботи, направлена на розробку і дослідження методів і структур апаратного аналізу аналогових тестових реакцій на базі FPGA, як одному із завдань аналогового тестування, є актуальною.[2]

Мета та завдання магистерскої роботи

Метою роботи є автоматизація процесу аналізу тестових реакцій аналогових пристроїв. Для досягнення поставленої мети в роботі ставляться наступні завдання:

• дослідження існуючих методів і систем діагностування АЦ-прістроїв і аналізу їх тестових реакцій зокрема;

• розробка методів і FPGA-структур аналізу аналогових тестових реакцій;

• розробка і дослідження експериментальної підсистеми аналізу аналогових тестових реакцій на базі FPGA.

Передбачувана наукова новизна

Передбачувана наукова новизна полягає в розробці методу і архітектури аналізатора аналогових тестових послідовностей на базі FPGA з метою забезпечення можливості тестування швидкодіючих АЦ-прістроїв. Очікується що розроблена підсистема забезпечуватиме високу швидкодію, компактність, гнучкість і універсальність, а також низьку вартість.[9]

Види аналогового тестування

Розглянемо основні види тестування аналогових схем.[1]

Кожен клас аналогової схеми (АЦП, ЦАП, фільтр, ланцюг фазової синхронізації і т. д.) має свій власний набір специфікацій. Для кожного з них вже існують прийнятні функціональні тести для випробування дослідного зразка і мінімізовані по довжині тестові набори для випробувань серійної продукції. Але не існує універсальних тестів для перевірки характеристик схем.

Основна різниця між ними полягає в походженні несправностей і процедурі моделювання.

Функціональний тест часто передбачає, що компоненти є несправними і генерує список несправностей, використовуючи катастрофічні і параметричні несправності. При структурному тестуванні використовується статистика виробничих несправностей.[1]

Тестування аналогових схем за призначенням можна розділити на наступні три категорії:

• зняття характеристик схеми для визначення чи задовольняє вона специфікації;

• діагностика для визначення причини несправності, коли схема не проходіт тест;

• заводські випробування, що проводяться для перевірки великих об'ємів лінійних і аналогово-цифрових схем.

У свою чергу тести підрозділяються на наступні види:[1]

• тести, засновані на специфікації - генеруються безпосередньо із специфікації схеми, без використання моделей аналогових несправностей. Цей підхід легко адаптується до широкого спектру схем. Проте при використанні великої кількості специфікацій тестування стає досить дорогим. Тестова послідовність може бути скорочена шляхом виявлення залежностей між специфікаціями і відкиданням непотрібних тестів.

• структурні тести, побудовані з використанням моделей несправностей - застосовуються для виявлення певного вигляду модельованих несправностей. Це дозволяє розбити набір аналогових тестів на групи по мірі покриття несправностей, і таким чином тестовий набір може бути ранжируваний. Це дає можливість скоротити довжину тестової послідовності завдяки тому, що тест, який покриває несправності вже виявлені попередніми тестами, може бути відкинутий.

Складнощі при тестуванні аналогових сигналів

При тестуванні і виявленні несправностей схем виникають деякі складнощі, пов'язані з технологічним процесом, помилками виміру і так далі. Нижче приведені основні з них:

1. Складність моделювання несправностей

Аналогові схеми мають складні зв’язки між вхідними і вихідними сигналами. Багато аналогових схем є нелінійними системами, наприклад, МОП-транзистор, використовуваний як підсилювач. Значення параметрів схеми відрізняються один від одного навіть в хороших схемах. Використання детермінованих моделей неефективне для аналогових схем.[6] Таким чином, сигнал приймає номінальне значення і виділяється діапазон допустимих відхилень від номінального значення. Моделювання і вимір неточності і погрішності при проектуванні інтегральних схем визначається допустимим відхиленням значення сигналу. Використання детермінованих моделей неефективне для аналогових схем. Таким чином, сигнал приймає номінальне значення і виділяється діапазон допустимих відхилень від номінального значення. Моделювання і вимір неточності і погрішності при проектуванні інтегральних схем визначається допустимим відхиленням значення сигналу.[1]

2. Помилки моделювання

Очікувані значення сигналу аналогової схеми розраховуються на основі моделювання, точність якого обмежена точністю чисельних значень, використовуваних в алгоритмі моделювання, також моделювання передбачає допущення, що стосуються точності зовнішніх аналогових пристроїв. Крім того, процес моделювання приводить до здобуття кращих результатів по встановленню діапазону різних значень.[1]

3. Погрішності вимірів при тестуванні

Помилки вимірів при тестуванні аналогових схем виникає із-за зсуву аналогового сигналу, впливу навантаження вимірювального зонда на поведінку аналогових схем, а також навантаження зонда. Крім того, випадковий шум є проблемою, тому аналогові випробувальні пристрої обмежені в пропускній спроможності і точності вимірів.[1] Для аналогово-цифрових мікросхем пересилка значень внутрішніх аналогових сигналів до вихідних портів може змінити сигнал і роботу схеми в цілому. Ємкісні зв'язки між високочастотними цифровими сигналами і аналоговими сигналами викликають додаткові погрішності аналогової схеми. Аналогове тестування повинне створювати різницю на аналоговому виході між справними і несправними пристроями, яка лежить за межами погрішності тестового приладу і автоматичного випробувального обладнення.[6]

4. Проблеми доступу при моделюванні

Модельована схема є набором складних і недоступних внутрішніх компонент, що обмежує використання звичайного аналогового автоматичного випробувального устаткування.

5. Погрішності виробничого процесу

Різні параметри пристроїв у великих обсягах виробництва інтегральних схем підкоряються статистичним законам розподілу. Цей різновид процесу може в значній мірі впливати на значення параметрів компонент.[1] Існують способи аналогового моделювання і конфігурації схем, щоб звести до мінімуму вплив температури і градієнта дифузії на компоновку схем. Наявність параметричних несправностей впливає на зміну вартості компонент. Проте література по аналоговому тестуванню також описує зміну вихідних параметрів, наприклад зміна коефіцієнта посилення підсилювача. Обидва види правильні, а сенс буде зрозумілий з контексту. Для аналогових пристроїв множинні параметричні несправності (за участю декількох незначних змін компонент) тим більше, чим більше величина однієї несправності або критичної несправності.

6. Інформаційний потік

Складно тестувати схему шляхом індивідуального тестування її підсхем. Розглянемо випадок аналогової схеми з двома каскадами С1 і С2, кожен з яких має один вхід і один вихід, і передавальні функції по напрузі Н1 і Н2. С1 і С2 можуть працювати неправильно коли тестуються індивідуально із-за недосконалості виробничого процесу, який спотворює їх передавальні функції.Проте, коли каскади з'єднуються разом може статися так, що спотворення в Н1 компенсується спотворенням в Н2, яке в деякому розумінні може бути інверсією спотворення Н1. Отже комбінація каскадів С1 і С2 фактично працює правильно. І навпаки, окремо правильні аналогові підсхеми при з'єднанні формують неправильну схему. [1]

Зміст

Функціональне тестування з використанням DSP

В даний час практично всі аналогові схеми тестуються з використанням автоматизованих систем контролю (АСК) побудованих на базі DSP. Дані АСК замість використання реальних аналогових вимірювальних інструментів, виконують їх емуляцію на основі швидкого перетворення Фур'є (ШПФ) і дискретного перетворення Фур'є (ДПФ), для того, щоб зменшити помилку виміру і усунути небажаний час встановлення сигналу при тестуванні.[1]

На рисунку 1 представлена традиційна аналогова АСК. Варто звернути увагу, що вона не має засобів синхронізації між блоками генерації дій і аналізу реакцій. На рисунку 2 представлена АСК на базі DSP, яка має відповідну синхронізацію і складається з АЦП, ЦАП, пам'яті для зберігання дій і реакцій, DSP, який керується програмно. DSP може емулювати широкий набір вимірювальних інструментів. Інструментами тепер є підпрограми, які обробляють вектора чисельних значень. Вектор може бути набором вибірок сигналу, частотним спектром і так далі. Фахівець з тестування створює набір векторів у вигляді тестових сигналів. Синтезатор сигналів подає ці вектора на ЦАП, вихід якого сполучений з поновлюючим фільтром для здобуття безперервного сигналу з обмеженою смугою пропускання. Отриманий сигнал подається на випробовуваний пристрій, з якого знімаються реакції. Діскретизатор аналогових сигналів виконує оцифрування знятих реакцій з використанням високошвидкісного АЦП і зберігає вибірки в ОЗП. Коли як випробовуваний пристрій виступає аналогово-цифрова схема, сигнали з виходів цифрової частини записуються у вхідну пам'ять, а тести для цифрової частини подаються на об'єкт діагностики (ОД) з вихідної пам'яті.[1]

На рисунку 3 зображений процес синтезу аналогового сигналу, а на рисунку 4 - процес оцифрування.

Рисунок 1 - Традиційна аналогова АСК [1]

Рисунок 2 - Аналогова АСК на базі DSP [1]

Рисунок 3 - Синтез аналогового сигналу [1]

Рисунок 4 - Оцифровка аналогового сигналу [1]

Переваги АСК на базі DSP

• Точність. АСК на базі DSP практично завжди володіють більшою точністю, ніж аналогові інструменти, оскільки помилка в наборі вибірок сигналу значно менше після цифрової обробки, чим помилка індивідуальної вибірки. Наведення, шум і відхилення сигналів значно скорочуються в DSP-тестерах, оскільки аналоговий сигнал оцифровується на найранішій стадії. Старіння компонентів тестера і температурні ефекти викликають значно менше проблем, оскільки цифрові компоненти краще зберігають свої характеристики, ніж аналогові.[1]

• Швидкість.DSP-тестер може отримати набір вибірок від ОД за один період вибірки, а далі використовуючи ДПФ і ШПФ виконати над ним різні виміри шляхом емуляції інструментів. Для виконання множинних вимірів dsp-тестер значно ефективніший, ніж аналоговий, в якому треба виконувати множинні виміри. Також в DSP -тестері відсутні тимчасові витрати на встановлення сигналу у фільтрі, які присутні в аналоговому тестері.[1]

• Простота використання. Оскільки тестер цифровий, то легко повторювати тестування, виконувати налаштування і зберігати виконані налаштування.

• Більше вимірювальної інформації. DSP-тестер надає додаткову інформацію разом з вимірюваним параметром, наприклад, піковий детектор повідомляє не лише про значення піку, але і про розташування піку в часі.

• Розмір і потужність.АСК загального призначення на базі DSP менше, дешевше і вимагає меншої потужності, чим відповідна аналогова АСК.

Недоліки АСК на базі DSP

• Вони дороги, хоча ціна знижується завдяки використанню СБІС, і зокрема ПЛІС. Розрядність, необхідна для досягнення прийнятної точності, і вимоги по смузі пропускання роблять DSP дорогими;

• коли необхідно виконувати лише один вимір, чисто аналогові тестери дешевші. DSP володіють перевагою лише при множинних вимірах;

• гнучкість інструментарію є проблемою для недосвідченого оператора, оскільки необхідно володіти практичними навиками їх використання;

• фахівець з тестування повинен знати фізичні і математичні принципи, які лежать за кожним тестом і джерелом помилок.[1]

Реалізація алгоритмів DSP з допомогою ПЛІС

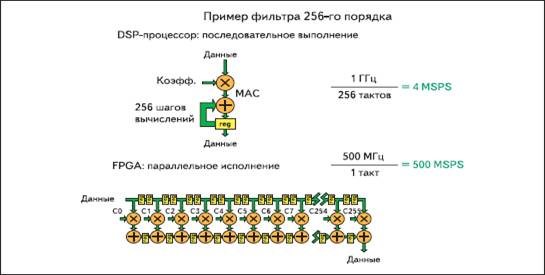

Практично з моменту своєї появи FPGA позиціювали як пристрої, що перевершують сигнальні процесори по співвідношенню продуктивність/ціна. В той же час відомо, що програмовані мікросхеми не можуть конкурувати з ASIC (спеціалізована для вирішення конкретного завдання інтегральна схема (ІС)) за ціною і тактовою частотою.[3] На рисунку 3 проілюстровані відмінності між сигнальним процесором і FPGA при виконанні операції цифрової фільтрації.

Рисунок 3 – Процес цифрової фільтрації у сигнальному процесорі та FPGA [3]

На цьому рисунку видно, що, хоча сигнальний процесор, створений за порівнянною технологією, в середньому володіє вищою тактовою частотою, єдиний потік виконання команд обуславліваєт різке зменшення загального числа операцій (якщо під «операцією» розуміти всю послідовність множень і складань, потрібну для реалізації всього фільтру або іншого алгоритму). В той же час FPGA сповна можуть забезпечити однотактне виконання всіх операцій, використовуючи паралельний розрахунок. Цьому сприяє, очевидно, наявність великого числа блоків DSP, що виконують множення з накопиченням. Неважко відмітити, що для ефективного використання цієї переваги слід орієнтуватися на алгоритми і методи, що мають на увазі розпаралелювання операцій, — фільтри високих порядків, швидке перетворення Фур'є, вейвлет-аналіз і тому подібне.[3]

Крім того, важливою перевагою FPGA є їх здатність забезпечувати не просто високу швидкість обробки, але ще і безперервну обробку на стабільній швидкості.

Процесорне ядро може виконувати організацію інтерфейсу, налаштування, моніторинг, завантаження коефіцієнтів і інші операції, реалізовувати які апаратний занадто складно. При цьому єдине процесорне ядро може забезпечувати управління декількома сотнями DSP-блоків ПЛІС, які постійно виконують обробку вхідного потоку навіть без участі процесора.[3]

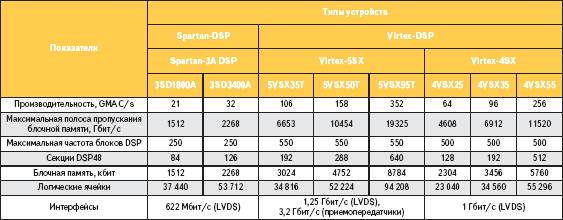

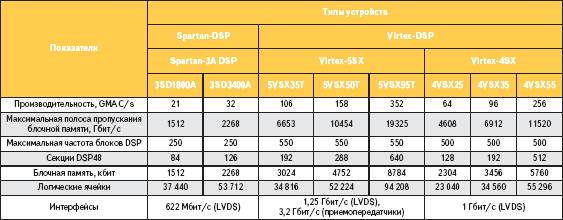

Таблиця 1. Технічні характеристики пристроїв FPGA Xilinx, орієнтованих на цифрову обробку сигналів [3]

Результати роботи (на момент написання автореферата)

На момент написання автореферата були отримані наступні результати:

• Виконаний огляд існуючих методів тестування;

• на основі технічних характеристик і по співвідношенню ціна\якість була вибрана елементна база для реалізації аналізатора аналогових тестових реакцій;

• проведені дослідження і розроблений експериментальний пристрій вибірки аналогових тестових реакцій за допомогою налагоджувального комплексу FPGA. В даний час проводяться дослідження по підвищенню швидкодії пристрою вибірки.

Висновки

На основі вищевикладеного матеріалу можна зробити висновок:

• розробка і дослідження методів і структур апаратного аналізу аналогових тестових реакцій є украй актуальною;

• сформульовані завдання дозволять досягти поставленої мети;

• на основі виконаного огляду існуючих різновидів тестування аналогових і АЦ-прістроїв для дослідження було обрано тестування з використанням DSP;

• для побудови тестів і аналізу отриманих тестових реакцій в даній роботі був обраний оптимальний клас катастрофічних і параметричних несправностей;

• у якості апаратної реалізації був обраний налагоджувальний FPGA комплекс Spartan-3E.

Список використаної літератури

1. Agrawal V.D. Essentials of electronic testing for digital, memory and mixed-signal VLSI circuits / V.D. Agrawal, M. L. Bushnell // Boston: Kluwer Academic Publishers, — 2000, 650p.

2. Bapiraju Vinnakota. Analog and mixed-signal test / Bapiraju Vinnakota // Prentice Hall PTR, 1998. — 261p.

3. Тарасов И. Возможности FPGA фирмы Xilinx в задачах цифровой обработки сигналов [Электронный ресурс] Режим доступа: http://www.kit-e.ru/articles/plis/2007_5_68.php

4. Тарасов И. Сравнительный анализ архитектуры основных семейств ПЛИС FPGA фирмы Xilinx [Электронный ресурс] Режим доступа: http://www.kit-e.ru/articles/plis/2005_6_96.php

5. Давыдов П.С. Техническая диагностика радиоэлектронных устройств и систем / П.С. Давыдов // М.: Радио и связь, 1988. — 256 с.

6. Зинченко Ю.Е. Проблемы зондового поиска неисправностей и пути их решения / Ю.Е. Зинченко, А.М. Козинец, К.Н. Жилин // Сборник трудов Донецкого государственного технического университета. Серия: Информатика, кибернетика и вычислительная техника, выпуск 6. — Донецк: ДонГТУ, 1999.— С. 212—217.

7. Zinchenko Yuri E. Computer-aided design and hardware description languages / Yuri E. Zinchenko // Сборник трудов Донецкого государственного технического университета. Серия: Проблемы моделирования и автоматизации проектирования динамических систем, выпуск 10. — Донецк: ДонГТУ, 1999.— С. 210—216.

8. Суворова Е.А. Проектирование цифровых систем на VHDL / Е.А. Суворова, Ю.Е. Шейнин // СПб.: БХВ-Петербург, 2003. — 576 с.

9. Зинченко Ю.Е. Синтез оптимальных структур асинхронных сигнатурных анализаторов / Ю.Е. Зинченко // Сборник трудов Донецкого государственного технического университета. Серия: Информатика, кибернетика и вычислительная техника, выпуск 6. - Донецк: ДонГТУ, 1999.— С. 186—191.

10. Поляков А.К. Языки VHDL и VERILOG в проектировании цифровой аппаратуры / А.К. Поляков // М.: СОЛОН-Пресс, 2003. — 320с. |