Реферат по теме выпускной работы

Содержание:

- Введение

- Обзор

- Заключение

Актуальность

На сегодняшний день электроника и автоматика является частью нашей жизни, мы, порой не замечая, тесно соприкасаемся с ней практически во всех сферах деятельности. Сейчас для реализации цифровых систем в качестве аппаратного базиса часто используется ПЛИС (программируемые интегральные логические схемы). Применение ПЛИС позволяет ускорить разработку, увеличить надёжность, степень интеграции производимых и разрабатываемых устройств.

Важнейшей частью любой цифровой системы является устройство управления, эффективность которого во многом определяет характеристики системы. Принцип микропрограммного управления был предложен в 1951г. М. Уилксом и предполагает наличие в любой цифровой системе устройства управления (УУ), координирующего работу всех блоков системы. В теме дипломной работы рассматриваются микропрограммные устройства управления (МУУ). Микропрограммные устройства управления разделяются на автоматы с «программируемой» логикой, которые основаны на хранении команд в управляющей памяти и на автоматы с «жесткой» логикой, которые представляют собой схему с четкой последовательностью, синтезированную по описанию заданному абстрактным автоматом. У каждого из этих типов автоматов есть свои минусы, которые с успехом решаются при использовании КМУУ (композиционных микропрограммных устройств управления). Однако более эффективно было бы использовать КМУУ с несколькими источниками кодов.

Одними из наиболее популярных ПЛИС являются CPLD. Высокая стоимость этого базиса ставит актуальную задачу сокращения аппаратурных затрат в схеме.

Цели и задачи

Целью работы является уменьшение аппаратурных затрат в схеме КМУУ, путем минимизации логической схемы за счет применения структуры с несколькими источниками кодов, что приведет к уменьшению стоимости конечного продукта.

Предполагаемая научная новизна и научная ценность:

Научная новизна полученных результатов магистерской работы будет заключаться в разработке структуры КМУУ, ориентированной на минимизацию стоимости. Планируемая научная ценность будет заключаться в разработке структуры КМУУ с улучшенными характеристиками в базисе CPLD.

Локальный обзор темы

В Донецке данной темой занимается ДонНТУ, проходят исследования на тему синтез и оптимизация управляющих устройств, на тему защищено довольно большое количество магистерских работ, писались диссертации.

- Мирошкин Александр Николаевич занимался синтезом и исследованием композиционных микропрограммных устройств управления с базовой структурой.

- Лаврик Александр Сергеевич занимался синтезом и исследованием композиционных микропрограммных устройств управления с модифицированной системой микрокоманд на ПЛИС.

- Цололо Сергей Алексеевич занимался исследованием методов синтеза устройств управления на программируемых пользователем вентильных матрицах.

- Профессор Баркалов Александр Александрович работает на кафедре ЭВМ с 1976 года. Область научных интересов - синтез микропрограммных устройств управления в базисе программируемых логических устройств.

Национальный обзор темы

- http://www.opu.ua/ru/index.html Одесский национальный политехнический университет, кафедра «Компьютерные интеллектуальные системы и сети».

- http://snu.edu.ua/welcome.php Восточноукраинский национальный университет им. В.Даля, кафедра автоматики и систем управления.

- http://www.kture.kharkov.ua Харьковский национальный университет радиоэлектроники.

Мировой обзор темы

- http://iaac.technion.ac.il/home.html Израильская ассоциация автоматического управления (IAAC) , профессор Эзра Зэхэб.

- http://www.iie.uz.zgora.pl/ Институт информатики и электроники Зеленогурского университета (Зелена Гора, Польша)

- http://scwww.math.uni-augsburg.de/~control/indexen.html Группа университета Аугзбурга (Германия) во главе с профессором, доктором Фрицем Колониусом.

Описание полученных результатов

Необходимые для проведения исследований данные были получены с помощью программного комплекса состоящего из следующих частей:

Анимация 4 кадра, размер 13,6 кб, количество циклов: 9

В состав системы входят:

- FSM-Editor – специализированное средство позволяющее создавать граф-схемы алгоритма (ГСА) путём их графического ввода или автоматической пакетной генерации согласно заданным параметрам. Далее, описание алгоритма можно сохранить в формате XML.

- VHDL-Generator – специализированное средство предназначенное для получения VHDL кода необходимого устройства управления согласно выбранной структуре и описанию алгоритма в формате XML.

- Xilinx ISE – средство разработки, бесплатно предоставляемое компанией Xilinx. Позволяет на основе VHDL описания устройства управления получить оценочные характеристики аппаратурных затрат при реализации алгоритма на ПЛИС CPLD.

- GNU Octave – бесплатный аналог MathLab. Используется для анализа данных, полученных от Xilinx ISE и построения графиков

Полученные результаты:

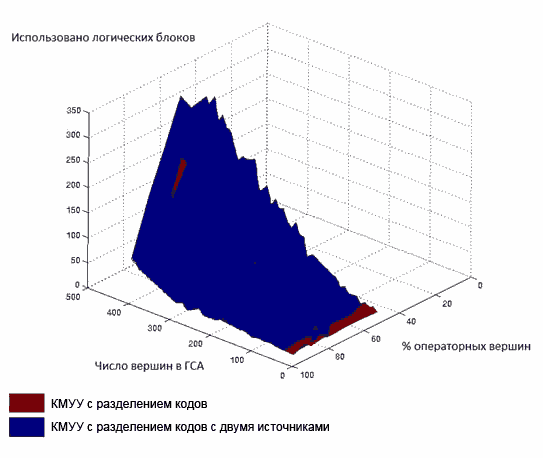

В результате работы программного комплекса были получены некоторые зависимости, отражающие эффективность

некоторых из предложенных структур (отображено на рисунке). На рисунках отражена поверхность, определяющая при каких условиях достигается минимум аппаратурных затрат. Поверхность окрашена цветом той структуры, для которой достигается минимум в каждой её точке.

Выводы

Исследования показали, что в сравнении с базовой КМУУ, применение предложенной структуры позволяет снизить аппаратурные затраты.

По состоянию проекта на сегодняшний день можно сделать вывод о том, что дальнейшие исследования должны быть направлены на адаптацию предложенной структуры к базису ПЛИС CPLD, а также на разработку методов оптимизации представленной схемы.

Источники

- Baranov S. Logic Synthesis for Control Automata. – Kluwer Academic Publishers, 1994. – 312 pp.

- Соловьев В.В. Проектирование цифровых схем на основе программируемых логических интегральных схем. – М.: Горячая линия-ТЕЛЕКОМ, 2001. – 636 с.

- Barkalov A., Titarenko L. Logic Synthesis for Compositional Microprogram Control Units. – Berlin: Springer, 2008. – 272 pp.

- Maxfield C. The Design Warrior’s Guide to FPGAs. – Amsterdam: Elseveir, 2004. – 541 pp.

- Баркалов А.А., Палагин А.В. Синтез микропрограммных устройств управления. - Киев: ИК НАН Украины, 1997. - 156с.

- Саломатин В.А., Баркалов А.А., Стародубов К.Е. Оптимизация логической схемы микропрограммного устройства управления на ПЛМ и ПЗУ // УСиМ. - 1987. - №2. - С. 57-60.

- Баркалов А.А. Оптимизация логической схемы автомата Мура на CPLD / А.А. Баркалов, А.В. Матвиенко, С.А. Цололо // Комп'ютерні засоби, мережі та системи. – 2007. – № 6. – С. 46-51.

- Баркалов А.А. Оптимизация схемы МПА Мура на CPLD / А.А. Баркалов, С.А. Ковалев, С.А. Цололо // Материалы Восьмого международного научно-практического семинара «Практика и перспективы развития партнерства в сфере высшей школы». – Донецк-Таганрог, 2007. – Том 3. – С. 26-36.

- Zeidman B. Designing with FPGAs and CPLDs / B. Zeidman. – Elsevier, 2002. – 224 pp.

- Технология устройств CPLD [Электронный ресурс]: Режим доступа: URL: http://www.parallel.ru/FPGA/cpld.html