Abstract

- Introduction

- 1. Goals and objectives

- 2. Relevation and motivation

- 3. Planned practical results

- 4. Development method of peripherals emulation

- Conclusion

- References

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing – hence field-programmable

. The FPGA configuration is generally specified using a hardware description language (HDL) [1] [14] [15] [16] [17].

FPGA is an important subject for studying in the field of computer engineering. But the cost of the equipment creates a large obstacle for receiving practical experience by students. Financing universities also doesn't allow to get enough debugging board that students could carry out individually the projects on a practical training. The way out of this situation is the creation of a virtual laboratory with access to it via the Internet. This will allow students to debug their designs, regardless of their location and easily get practical experience in the design of FPGA devices.

The overall objective of master's work is to create a virtual FPGA [18] [19] laboratory with remote access via the Internet. Remote access involves downloading firmware design in the FPGA chip, organization of management of the input devices debugging board, visualization output results, organization distributed access to the board [20] [21].

The firmware that is loaded into the board, is a project developed in VHDL or Verilog, generated in to bit file using the development environment (for example, ISE Design Studio). Download the firmware will take place in the following sequence:

- The user loads the bit file into his working directory.

- Initiate start the firmware downloading in the board.

- The file is downloaded to the board through the JTAG interface.

Visualization of the output data is planned with the help of video cameras, broadcast in real-time changes in the state of the debug stand. Also, the output data will be available via the serial port connected to the server.

The main objective of the project and the master's work as a whole is to provide users testing peripheral devices connected to the board. Since physical access to the peripheral equipment via the Internet will not be possible for user, it is necessary to develop a method of emulation equipment so that project for the emulated hardware has minimally difference between project for real device. First of all, it is planned to develop simulators for the computer mouse and keyboard connected on the PS/2 protocol.

Also, if remote access to FPGA [22] [23] board organization needs to take into account the distributed access, which is access rights to debug stand and queuing work with him. This is necessary because you can download in the board only one project. Therefore it is necessary to organize two types of access: global and local. Global access type is set by the administrator, and local access is a queue to the board. This necessary because only one user can has access to the board in one session. Once the user exits the board, he frees it, or the system automatically releases the board on long inactivity, and then the next user can start a new session [24] [25].

Now access to the Internet may be obtained virtually anywhere from the world, therefore the creation of a virtual laboratory is an actual problem. Organization of access to the lab through the website due to the fact that browsers work the same on all operating systems for desktop computers and mobile devices.

Search report on the theme of master's work has shown that quantity projects for the creation of virtual laboratories with access to the FPGA boards is small, and those that include the emulation of peripherals even less. Examples of research papers on the development of virtual laboratories FPGA can be found here [2] [3] [4] [5] and [6].

Remote control board system is structurally divided into three parts: the client part (web-site), server side and debugging the FPGA-complex (Figure 1).

The Web site must consist of a login page, registration page and personal account. Each user can have access rights:

administrator

– users can assign privileges to other users, as well as have access to the board;user

– can access the debug stand;guest

– allowed to monitor the work of the stand, but you can not execute it their projects.

Once registered, a user is assigned to the right of guest

access, the administrator can set in your account it necessary rights. Structurally personal user

account is presented on Figure 2.

On the right side there is a file manager that is the user's personal directory. With it you can upload files, create directories, delete files and folders, and upload the firmware into the board. There is management console in a central part of the picture, it will serve primarily for logging and debugging information output from the stand. From the left side videoplayer with broadcast video of stand debug will be shown. In the lower part there is a control panel with auxiliary settings of control remote laboratory.

The server part is a link between the stand and the user. The server must locate installed Web Server (IIS) for the transmission information to the user, a database (MySQL) and server-side programming language (PHP), HTML-code generating and processing data, communicate with user. Software to work with the debug stand also should be installed (Xilinx ISE Design Studio) and software organizes live video (VLC). To download the firmware, using the JTAG interface, as well as for sending and receiving, it is recommended to use a serial port (COM-port).

The server processes a user registration data, checks permissions, organizes access to the board, reception and transmission of data from the user to the board and vice versa. Also there is video streaming to the client from the server.

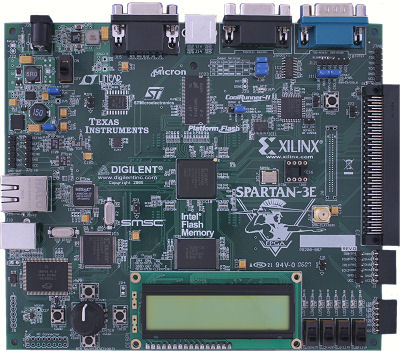

Stand uses FPGA board of the company Xilinx – Spartan 3E Starter Kit for debugging (Figure 3).

Debug stand uses Microblaze microprocessor core for testing peripheral devices. Microblaze – soft-core processor, developed by Xilinx for use in FPGA. Microblaze is implemented using standard logic and FPGA memory blocks [8].

MicroBlaze has a universal links with the periphery, providing the possibility of its widespread use in embedded systems. Basic I/O bus – CoreConnect PLB – bus can operate in master and slave modes. Most of the units are connected directly to the PLB. To access the FPGA internal memory (BRAM), MicroBlaze uses special bus LMB, which reduces the load on other buses [9] [26] [27].

PLB – Processor Local Bus is really usefull for this task. This 128-bit bus for connecting an arbitrary number of peripheral devices. It consists of a bus control module, timer, reading and writing software, modules addressing unit and additional DCL (Device Control Register) slave interface for access to the register of errors [10] [28] [29].

Before emulate peripheral equipment, principles of PS/2 interface should be learned. PS/2 – bidirectional interface, organizing data exchange between two devices. In this interface, the main lines are the Data and CLK. Each packet has a length of 11 bits:

- 1 start bit – is always

0

; - 8 data bits;

- 1 parity bit;

- 1 stop bit – is always

1

.

The keyboard transmits keys scan-codes through the serial-port and the mouse sends 3 or 4-byte data containing the state of the pressed buttons and mouse movement. The fourth byte can be uesd for wheel scrolling, but it is necessary to specially initialize the mouse.

The host device can send commands to the keyboard and mouse controller. Mouse and keyboard respone byte 0xFA after recieving any of this command. The basic commands common to mouse and keyboard are:

- 0xFF – reset;

- 0xFE – resend, of the keyboard and mouse resend last byte.

On device initialization devices transmit 0xAA byte, and then keyboard can immediately send the keys scan-codes, and the mouse should send the next byte 0x00 – this is mouse ID without wheels. To initialize the mouse wheel is necessary to conduct additional initialization details which can be found in the official documents [11] [12] [13].

See mouse data packet structure on Figure 4.

The first byte has the following structure:

- 1st bit – the left mouse button;

- 2nd bit – right mouse button;

- 3rd bit – reserved for the middle mouse button;

- 4th bit – always

1

; - 5th bit – sign of the shift in the X axis;

- 6th bit – a sign of the displacement along the Y axis;

- 7th bit – overflow displacement axis X;

- 8th bit – overflow offset axis Y.

The second byte – is the offset along the X axis, and the third byte – displacement axis Y. The offset is calculated from left to right along the X axis and Y upwards. Moreover, if the mouse moves to the right and down, the offset is negative, in case of left and up movement offset is positive. Offset values are in the range -255 – 255. The sign offset stored in the first byte, and if this value is exceeded, the overflow bit is set [11].

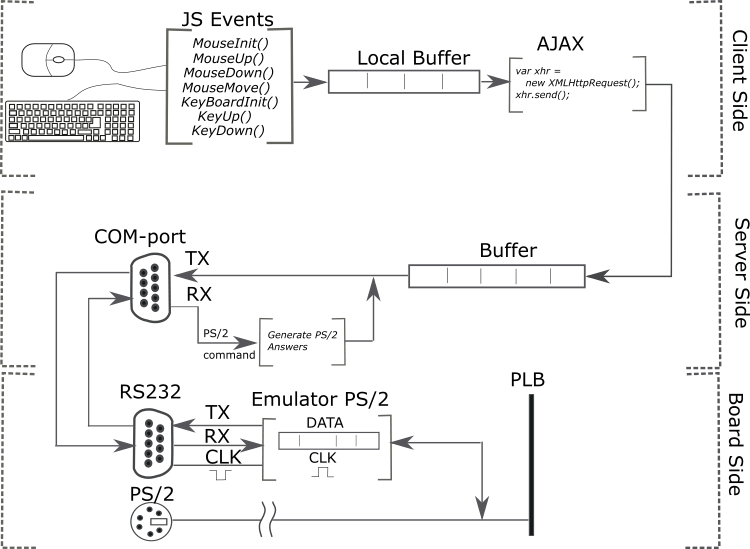

Keyboard and mouse emulator will use all parts of the project: the client side, server side and board side. Figure 5 shows the mechanism of the emulator PS/2 interface. On the client side JavaScript handles keyboard and mouse events that will generate the necessary code packets and send them to the server. Before sending the data it is necessary to run the device initialization. After that event handlers from the keyboard will check the code of the pressed keys, select the desired code from the scan-code table, add additional code in the case of extended keys, as well as complement releasing key by a special break-code (0xF0). Encapsulation keyboard code algorithm is shown on Figure 6. The generated data will be sent to the server using ajax-requests. To avoid exceeding the number of requests, and that the client is not stuck, you need to send a fixed amount of data, wait for a response from the server, and then send the next set of data. In order to know the state of the board, an additional asynchronous request that will be repeated with a certain time interval.

Mouse on the client side works in a similar way. Also initializer of mouse generates necessary codes. Handlers of mouse motion events, press and release button form data packets and as well as a keyboard and sends data to the server. Forming data packets from the mouse is shown on Figure 7.

The server receives the data from the client, buffers them and sequentially transmits via COM-port to the board. If the board sends a command to the device, then this command is intercepted by server application and server sends the appropriate response.

Data transmitted via COM-port, received by board and transmitted to the emulator PS/2 protocol, developed in the VHDL language. The purpose of the emulator is to receive data from RS232 serial interface, to convert these data into the PS/2 form and to pass PLB bus packet bypassing physical interface. The data received from the PLB bus must also be converted into RS232 interface form and passed to server.

At the time of creation of this page, the Master's work is not complete. Nowadays, it can be highlighted that current vector of master's work and methods of project developing are correct. Developing of described modules peripheral equipment emulation is planned in the future [30] [31] [32].

- Wikipedia: Field-programmable gate array. Internet resource. Access mode: wikipedia.org (Last update: May 2016)

- Personal site Masters portal DonNTU. Author: Beseda Dmitriy 2014. Internet resource. Access mode: masters.donntu.ru (Last update: May 2016)

- Laboratory of e-learning (LoEL) SibSUTI. Internet resource. Access mode: www.labfor.ru (Last update: May 2016)

Open Education

Scientific practical journal. Article: Universal Laboratory for interdisciplinary teaching computer-aided design of digital equipment, 2009, Authors: NA Dmitriev, LD Zabrodin, MN Ehin, BN Kovrigin, MY Pavlov. Access mode: www.e-joe.rusub[PDF] (Last update: May 2016)- A Remote FPGA Laboratory for Digital Design Students. Authors: Joao Soares, Jorge Lobo. Access mode: ap.isr.uc.pt[PDF] (Last update: May 2016)

- International Journal of Research in Engineering and Technology. Article: REMOTE FIELD-PROGRAMMABLE GATE ARRAY (FPGA) LAB, 2014, page 842. Authors: Karthik.S , P.Shreya , Srihari P. , N.M.Viswanath. Access mode: esatjournals.net[PDF] (Last update: May 2016)

- Spartan-3E FPGA Starter Kit Board User Guide, 2011 г. Access mode: www.xilinx.com[PDF] page 11 (Last update: May 2016)

- Wikipedia: Microblaze. Access mode: wikipedia.org (Last update: May 2016)

- Rod Jesman, Fernando Martinez Vallina, Jafar Saniie Microblaze Turtorial page 36. Access mode: ecasp.ece.iit.edu[PDF] (Last update: May 2016)

- LogiCORE IP Processor Local Bus (PLB) v4.6 (v1.05a) Internet resource. Access mode: www.xilinx.com[PDF] (Last update: May 2016)

- The PS/2 Mouse Interface, 2001, Author: Adam Chapweske. Internet resource. Access mode: www.computer-engineering.org (Last update: May 2016)

- 12. The study protocol PS / 2 mouse. Author: Evgeny Amosov. Internet resource. Access mode: www.programmersclub.ru (Last update: May 2016)

- 13. Practical Programming Arduino / CraftDuino - connect the mouse PS / 2, 2009. Internet resource. Access mode: robocraft.ru (Last update: May 2016)

- Gritsenko AA Zinchenko YE, Seroshtan SY. Increased hardware priority queues in FPGA performance FPGA with low-cost basis // Materials III Intl. nauk. and practical. Conf. stud., PhD student. and youth. scientists. Information and control systems in the industry, economy and ecology, September 2011. Severodonetsk: techn. Inst Shidnoukr. nat. Univ them. Dal, 2011. P. 15 - 23.

- KV Medvedev, Zinchenko YE "The navigation system based on FPGA-technology with the ability to self-test" / Proceedings of the seventh international science. Sc. Conf. Students and young researchers

Computers and computer technology - 2011

. - Donetsk: Donetsk National Technical University - 2011. - Zinchenko YE, Sherekin AA, Kovalenko IA Kovalev AM Development of real-time systems based on complex VIRTEX-5 FPGA ML501 // Proceedings of the VII International scientific-technical conference of students, graduate students and young scientists

Computers and computer technology

, 22-23 November 2011, Donetsk: Donetsk National Technical University. - 2011. 2 volumes, Volume 2. - P. 44-48 - Zinchenko UE, Sherekin AA Development of hardware sorting device with constant input and output time //

Computers and computer technology

, Proceedings of the VII International scientific-technical conference of students, graduate students and young scientists - November 22-23, 2011, Donetsk, Donetsk National Technical University . - 2011. 2 volumes, T. 1. - P. 72-76 - DN Voloshin, Zinchenko YE Development of real-time systems based on Xilinx XC3S500E Spartan-3E FPG // Proceedings of the VII International scientific-technical conference of students, graduate students and young scientists

Computers and computer technology

, 22-23 November 2011, Donetsk: Donetsk National Technical University. - 2011. 2 volumes, T. 1. - P. 44-47 - Seroshtan SY, Gorokhov IV, Demenko AG, EV Lobanov Construction of real-time systems based on FPGA platform company ALTERA // Proceedings of the VII International scientific-technical conference of students, graduate students and young scientists

Computers and computer technology

, 22-23 November 2011, Donetsk: Donetsk National Technical University. - 2011. 2 volumes, T. 1. - P. 61-63 - Gorokhov IV, Demenko AG, EV Lobanov, Seroshtan SY Search Results for means to build a system on a chip for platform FPGA ALTERA company: SOPC Builder and Qsys // Proceedings of the VII International scientific-technical conference of students, graduate students and young scientists

Computers and computer technology

, 22-23 November 2011 g ., Donetsk, Donetsk National Technical University. - In 2011, T. 2. 2 volumes - S. 19-21. 2012 - Sherekin AA Zinchenko YE, Zinchenko TA, AA Korchenko Developing a system for verifying the structure of the FPGA-projects // Proceedings of the III All-Ukrainian scientific-technical conference of students, graduate students and young scientists

Information control systems and computer monitoring

, 16-18 April 2012, Donetsk, Donetsk National Technical University. - 2012. pp 667-669 - Gorokhov IV, Zinchenko YE Verification Problems

system-on-chip

on FPGA based on the different stages of design // Proceedings of the III All-Ukrainian scientific-technical conference of students, graduate students and young scientistsInformation control systems and computer monitoring

, April 16-18, 2012, Donetsk: Donetsk National Technical University. - 2012. pp 591-594 - Gorokhov IV, Sherekin OO OO Korchenko, Zinchenko YE Features verification systems-on-chip based on FPGA // Materials of II All-Ukrainian school-seminar of young scientists and students ASIT'2012

Modern computer information technology

. - Ternopil: TNEU, 2012. - P. 89-90. - DN Voloshin, Zinchenko YE Log GV Conveyor implementation on FPGA adders and multipliers // Materials of II All-Ukrainian school-seminar of young scientists and students ASIT'2012

Modern computer information technology

. - Ternopil: TNEU, 2012. - P. 97-98. - Gontarenko BV Belovolova MA, Zinchenko YE The implementation of artificial neuron in the FPGA // Materials of III International scientific-technical conference of students, graduate students and young scientists Information control systems and computer monitors (ICS and CM-2012) - Donetsk: Donetsk National Technical University - 2012. - P. 586-590.

- Zinchenko YU.Є., Zinchenko TA, Aslanov i.G .. Virtualna the FPGA-laboratoriya s distantsiynim access //Ukrainian Materials III of seminar of young scientists and students ASIT'2013

Modern computer information technology

. - Ternopil: TNEU 2013. - DG Chatting, Zinchenko YE Development of a method of emulation work the FPGA-board keyboard port PS / 2 // Proceedings of the Ukrainian scientific-technical conference of students and young scientists,

Information control systems and computer monitors (ICS CM-2014)

, 22-23 April 2014, c. Donetsk: - Donetsk: DonNTU 2014 - t .1 - P. 157-162 -

YE Zinchenko, VI Kalashnikov, ON Dyachenko, TA Zinchenko. Modern FPGA-lab projects DonNTU / Collection between labor. Scientific-practical conference

Innovative prospects of Donbass

as part of the I-st Int. Scientific ForumDonbass-2015

, 20-22 May 2015. - Donetsk: Donetsk National Technical University. - 2015 - C 4. - VS. Lunch, VA Gen, JE Zinchenko, AV Koval. Study the organization of remote access to the FPGA-lab / / Collection of between labor. Scientific and Technical. Conf. students, graduate students and young scientists

Computer and Software Engineering - 2015

. - Donetsk: Donetsk National Technical University. - 2015 - C 5. - VV. Mohnachev, JE Zinchenko, AV Koval. An analysis of the feasibility of developing quadrocopters based FPGA / Collection vezhd works. Scientific and Technical. Conf. students, graduate students and young scientists

Computer and Software Engineering - 2015

. - Donetsk: Donetsk National Technical University. - 2015 - C 4. - VA. Gen DA Nesterenko, Yuri Zinchenko, PhD., T. Zinchenko. The emulator of microprocessors based on FPGA // / Collection vezhd works. Scientific and Technical. Conf. students, graduate students and young scientists

Computer and Software Engineering - 2015

. - Donetsk: Donetsk National Technical University. - 2015 - C 5. - Zinchenko Yu, V. Kalashnikov, Hajduk S. Dyachenko O. login G. Korchenko A. Zinchenko, T., et al .. Design FPGA-technology and diagnostics of computer systems / Collection of scientific works of VI Intern. nauchn.-Pract. Conf.

Modern information technology and IT education

. - Moscow: Moscow State University, 2011. - T. 1. S. 787 422-429