Реферат на тему випускної роботи

Розробка та дослідження пристроїв циклічного кодування

- Вступ

- 1. Актуальність і мотивація

- 2. Мета і завдання

- 3. Огляд досліджень і розробок по темі

- 4. Методи досліджень

- 5. Наукова новизна

- 6. Плановані практичні результати

- 7. Апробація роботи

- 8. Зміст роботи

- Висновок

- Перелік посилань

Вступ

В останні десятиліття динамічні зміни, що відбуваються в різних сферах діяльності суспільства, характеризуються обвальним зростанням обсягів найрізноманітнішої інформації: соціально - політичної, виробничої, наукової, культурної та ін. Міжнародна практика показує, що інформаційний потенціал в суспільстві починає дедалі більше визначати його економічний потенціал нарівні з матеріальним виробництвом. Економічний розвиток такого суспільства буде цілком визначатися результатами інтелектуальної діяльності. Це пов’язано зі зростаючою роллю інформації, яка стає визначальною в розвитку різних сфер діяльності суспільства.

1. Актуальність і мотивація

Визнаний класик теорії постіндустріалізму Д. Белл виділяє три технологічних революції: винахід парової машини в XVIII столітті; науково-технологічні досягнення в області електрики і хімії в XIX столітті; створення комп’ютерів в XX столітті [1].

Сучасна цивілізація XXI століття переживає чергову революцію - інформаційну. Стрімкі темпи розростання всесвітньої павутини призводять до формування цифрової цивілізації: якщо у 2000 році було 359 млн користувачів мережі Інтернет, то в березні 2017 року кількість користувачів вже 3732 млн - це половина населення земної кулі. У засобах масової інформації все частіше оголошують майбутню зеттабайтову епоху розвитку людства. За оптимістичними прогнозами - в період з 2012 по 2020 роки щорічно буде відбуватися подвоєння обсягу даних і на кінець цього періоду він складе приблизно 37 ЗБ [2].

Переваги інформізаціі і роботизації важко переоцінити. В останні десятиліття досягнення в галузі впровадження інформаційних технологій є одним з визначальних чинників економічного потенціалу суспільства. В результаті з’являється і розвивається інформаційна інфраструктура, яка надає нові послуги, такі як дистанційна освіта, телеработа, телемедицина, електронна торгівля, замовлення квитків для транспорту, інтернет-банкінг, оплата рахунків та ін. Разом з тим, збільшення кількості інформації, що передається, зберігається і обробляється, призводить до вимог забезпечення її достовірності та надійності використовуваних апаратних і програмних засобів. Від успішного вирішення цих завдань, з одного боку, залежить процвітання нинішньої цивілізації, або, з іншого боку - її саморуйнування, наприклад, через випадковий або навмисний збій в військових додатках. Крім того, необхідно враховувати такі явища, як сонячна активність і жорстке космічне випромінювання.

Зменшення топологічних норм проектування НВІС пам’яті збільшує чутливість ІС до локальних радіаційним ефектів. При цьому може не просто збільшуватися кількість помилок, але і змінюватися їх характер. При цьому завдання підвищення відмовостійкості пам’яті за допомогою завадостійких кодів стає особливо актуальним [3].

Тому для усунення можливих помилок через природних явищ, штучних причин, або дефектів апаратних інформаційних засобів, для захисту від пошкоджень, що виникають під дією жорсткого космічного випромінювання, використовуються сучасні технології завадостійкого кодування при проектуванні мікросхем пам’яті, весь спектр методів і засобів вбудованого самотестування цифрових систем [1 -22].

2. Мета і завдання

Метою роботи є розробка методів циклічного кодування, нових методів компактного тестування, дослідження їх достовірності, а також розробка схем, що реалізують ці методи.

Дослідження велися в наступних напрямках.

- Розробка альтернативних методів циклічного кодування, а також апаратної реалізації кодера і декодера.

- Розробка альтернативних методів компактного тестування на основі методів циклічного кодування.

- Експериментальна верифікація отриманих теоретичних результатів за допомогою засобів САПР Active-HDL.

3. Огляд досліджень і розробок по темі

Застосування принципів псевдовипадкового тестування дозволило ефективно діагностувати типові елементи заміни (ТЕЗ) і модулі ЕОМ серії ЄС (що серійно випускалися в СРСР), таких як: ЄС-1036, ЄС-1061, ЄС-1130, ЄС-1842 і ін. Висока ефективність компактного тестування з використанням псевдовипадкових тестових послідовностей і синтезованих генераторів псевдовипадкових вичерпних тестів дозволила застосувати його для реалізації тестування всіх типових елементів заміни ЕОМ ЄС-1130. [4]

Аналіз діагностичного забезпечення мікропроцесорних НВІС провідних зарубіжних фірм: IBM (S /390, метод LSSD); Hewlett Packard (сигнатурний аналіз); альянс компаній Apple, IBM і Motorola (Power PC); Motorola (MC 202-206); Intel Corporation (мікропроцесори 80386, Pentium Pro); Advanced Micro Devices (AMD-K6), показує, що 5-8% площі кристала НВІС займають вбудовані схеми тестування, які дозволяють виявити практично 100% дефектів. Наприклад, діагностичне забезпечення мікропроцесора S / 390 включає: ОЗП, кеш, пам’ять, схеми їх управління з вбудованими схемами самотестування; тригери, реєстрові мережі, що утворюють в режимі тестування сканований шлях по методу LSSD; вбудовані ГТП; вбудований АТР - багатоканальний сигнатурний аналізатор; порт JTAG відповідно до стандарту IEEE 1149.1.

Методи вичерпного тестування КС і сканування дозволяють разом виявляти 95% несправностей. Застосування різних псевдовипадкових послідовностей, забезпечує 99,9% покриття всіх несправностей НВІС.

4. Методи досліджень

При виконанні роботи використовувався математичний апарат булевої алгебри, апарат технічної діагностики, теорії полів Галуа, теорії і практики завадостійкого кодування, теорії сигнатурного аналізу і теорії матриць. Перевірка працездатності пропонованих методів і апаратних засобів проводилася за допомогою комп’ютерного моделювання, зокрема, із застосуванням САПР Active-HDL.

5. Наукова новизна

Наукова новизна роботи полягає в розробці нових методів компактного тестування і їх схемної реалізації, а також вирішенні різних завдань обчислення достовірності контролю з їх допомогою і за допомогою систем на основі відомих методів вбудованого тестування. Зокрема, запропоновані.

I Альтернативні методи циклічного кодування і апаратної реалізації кодера і декодера.

- Варіанти апаратної реалізації кодів БЧХ та Ріда-Соломона, що виправляють одиночні і подвійні помилки (пакети помилок) і використовують синдромний метод декодування. На відміну від типового декодера не потрібно блоків рішення ключового рівняння на основі одного з алгоритмів, (наприклад, Берлекемпа-Мессі, алгоритму Евкліда або Пітерсона-Горенcтейна-Цірлера), пошуку коренів поліномів локаторів помилок на основі алгоритму Ченя, розрахунку значення помилки (алгоритм Форні ).

- Метод укорочення і апаратна реалізація циклічних кодів на основі подвійних поліномів. На відміну від відомих методів дозволяє вкорочувати коди з великим параметром укорочення.

- Альтернативний метод поділу поліномів. На відміну від відомих методів дозволяє ділення поліномів великої степені.

- Метод укорочення і апаратна реалізація циклічних кодів на основі альтернативного ділення поліномів. На відміну від відомих методів дозволяє вкорочувати коди великої довжини і застосування відомих методів декодування.

II Альтернативні методи компактного тестування на основі методів циклічного кодування

- Метод аналітичного обчислення сигнатур. На відміну про відомих використовує степеневу форму компактних оцінок, що дозволяє спростити визначення сигнатур.

- Визначення параметра тестованості комбінаційних схем. На його основі сформульовано і доведено умова рівності нулю сигнатур для кон’юнкція певного рангу. Розглянуто наступні варіанти.

- Для генераторних поліномів регістрів зсуву з лінійними зворотними зв’язками (РЗЛЗЗ) генератора тестової послідовності (ГТП) і аналізатора тестових реакцій (АТР) степені 5. У цьому випадку поліноми РЗЛЗЗ ГТП і АТР однаковою мірою, причому обидва полінома примітивні (а значить, незвідні).

- Для генераторних поліномів РЗЛЗЗ ГТП степені 10 і АТР степені, кратною десяти. В цьому випадку поліном РЗЛЗЗ ГТП примітивний, а поліном АТР кратної степені, причому поліноми примітивні (а значить, незвідні).

- Для генераторних мінімальних поліномів РЗЛЗЗ ГТП степені 12 і АТР степені, кратною дванадцяти. В цьому випадку поліном РЗЛЗЗ ГТП примітивний, а поліном АТР мінімальний, причому поліноми незвідні, але не завжди примітивні.

- Для генераторних поліномів РЗЛЗЗ ГТП і АТР, побудованих на основі поліномів кодів циклічного кодування, зокрема, кодів Хеммінга, Боуза-Чоудхурі-Хоквінгема, Ріда-Соломона, Файр.

- Для розглянутих варіантів компактного тестування запропоновані рекомендації для найбільш оптимальних поєднань генераторних поліномів.

Достовірність наукових положень, висновків і практичних рекомендацій підтверджена математичними доказами тверджень, сформульованих в роботі, результатами комп’ютерного моделювання.

6. Плановані практичні результати

Практична цінність роботи. На основі результатів, отриманих в роботі, вдається вибрати комбінації генератора і сигнатурного аналізатора в схемі вбудованого тестування ПЛІС, що забезпечують 100% виявлення одиночних несправностей в блоці І; будувати системи вбудованого контролю для конкретних пристроїв, знаходити достовірність контролю додаткового обладнанням, в рамках обраної моделі несправностей.

Теоретичні результати роботи включені в спеціальні курси для студентів, що спеціалізуються в області САПР цифрових схем: "Теорія перешкодостійкого кодування", "Теорія кодів, що коректують помилки", "Системи контролепридатного проектування КС".

7. Апробація роботи

Результати роботи доповідалися на конференціях:

V Міжнародна науково-технічна конференція студентів, аспірантів та молодих вчених, 22-23 квітня 2014 року, м.Донецьк;

VI Міжнародна науково-технічна конференція студентів, аспірантів та молодих вчених, 20-22 травня 2015 року, м.Донецьк;

Комп’ютерна і програмна інженерія. Міжнародна науково-технічна конференція студентів, аспірантів та молодих вчених 15-16 грудня 2015 року. - Донецьк

9. Зміст роботи

Основні результати роботи висвітлені в публікаціях.

Альтернативні методи циклічного кодування і апаратної реалізації кодера і декодера

Коди Ріда-Соломона були запропоновані вже понад півстоліття тому, проте вони продовжують залишатися предметом уваги і дослідження. Це пов’язано, перш за все, з появою все нових областей їх використання, тепер уже не тільки в задачах зв’язку, але і в широкому застосуванні для задач цифрової техніки.

В даний час має місце тенденція реалізації апаратних проектів із застосуванням мов опису апаратури (VHDL, Verilog), які дозволяють здійснити проектування, верифікацію цифрових схем на різних рівнях абстракції і реалізацію (наприклад, у вигляді НВІС) на основі технології FPGA. Такий підхід має ряд переваг. Наприклад, він більш гнучкий при зміні схеми або рівня технології виготовлення ІС, крім того, він дешевший в порівнянні з застосуванням замовних ІС (ASIC). Тому питання побудови та апаратної реалізації кодів Ріда-Соломона є актуальними, враховуючи дедалі більшу їх популярність і затребуваність для різних сфер застосування.

Проведений аналіз літератури [2 -8] віддзеркалює широкий спектр розроблених і вже використовуваних на практиці кодів Ріда-Соломона. Можна навести декілька найбільш відомих прикладів: (255, 223, 33) код Ріда-Соломона для космічного зв’язку NASA, укорочені коди Ріда-Соломона над полем Галуа GF (256) для CD-ROM, DVD і цифрового телебачення високої чіткості (формат HDTV) , розширений (128, 122, 7) код Ріда-Соломона над полем Галуа GF (128) для кабельних модемів. Існує декілька комерційних апаратних реалізацій - ряд інтегральних схем (ІС), призначених для кодування і декодування кодів Ріда-Соломона. При цьому реалізовані коди мають різні коригувальні здібності, і, як наслідок, різний рівень складності і сфери застосування. Наприклад, код Ріда-Соломона (255, k), де k - кількість інформаційних символів коду, для різних ІС може виправляти, як правило, від 1 до 16 помилкових символів.

Крім того, коди Ріда-Соломона можна використовувати не тільки для завадостійкого кодування при передачі даних, а також скрізь, де є необхідність в запобіганні пошкодження інформації, наприклад [6]:

- виявлення і виправлення помилок в пошкоджених або дефектних носіях інформації;

- виявлення і виправлення помилок при навмисному зміні інформаційних повідомлень з метою дезінформації;

- виявлення і виправлення модифікації інформації про автора або виконуваного коду з метою

злому

програмного забезпечення; - захист програмного забезпечення або даних від копіювання з ліцензійного диска;

- відновлення одного або декількох томів багатотомного архіву, перекручених або взагалі втрачених при завантаженні з мережі;

- виявлення і виправлення помилок в ланцюжках ДНК в генній інженерії.

Завдання порівняльного аналізу способів побудови кодів Ріда-Соломона, що виправляють подвійні помилки, з’явилася після публікації роботи [8], в якій розглядаються питання реалізації кодера і декодера (255, 251) коду в FPGA. Разом з тим, в роботах [5 -8] основна увага приділяється іншим принципам побудови подібних кодів, що відрізняються більш простими методами декодування.

Перш за все, слід зазначити, що коди Ріда-Соломона, що виправляють одиночні або подвійні помилки, незалежно від того, по якому полю Галуа вони побудовані, вкорочені, з посимвольним інтерлівінгом чи ні, допускають застосування методу синдромного декодування. Такий метод непридатний для кодів, що виправляють велику кількість помилок. Для них типовий декодер заснований на блоках обчислення синдрому, буферного регістра, рішення ключового рівняння на основі одного з алгоритмів, наприклад, Берлекемпа-Мессі, iBM, riBM, RiBM, алгоритму Евкліда або Пітерсона- Горенcтейна-Цірлера (в [8] - алгоритм iBM), пошуку коренів поліномів локаторів помилок на основі алгоритму Ченя, розрахунку значення помилки (алгоритм Форні), корекції помилок.

Розглянемо деякі варіанти апаратної реалізації циклічних кодів. Всі вони засновані на застосуванні регістрів зсуву з лінійними зворотними зв’язками.

Апаратна реалізація кодів БЧХ

Генераторний поліном коду БЧХ, що виправляє S помилок, повинен містити 2S коренів. Для обчислення цього полінома використовують мінімальні поліноми, отримані для деякого поля Галуа. Розмір поля Галуа вибирається залежно від необхідної довжини і коригувальних можливостей коду. Якщо для побудови коду вибрати поле Галуа GF (16), то довжина нескороченного коду буде дорівнюти 15 для будь-якої (до семи для цього поля) кратності помилок [5 , 7 , 10 -12].

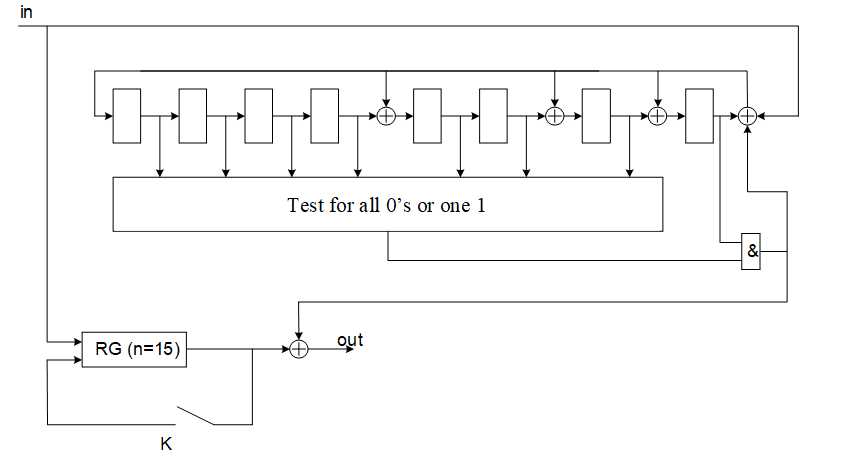

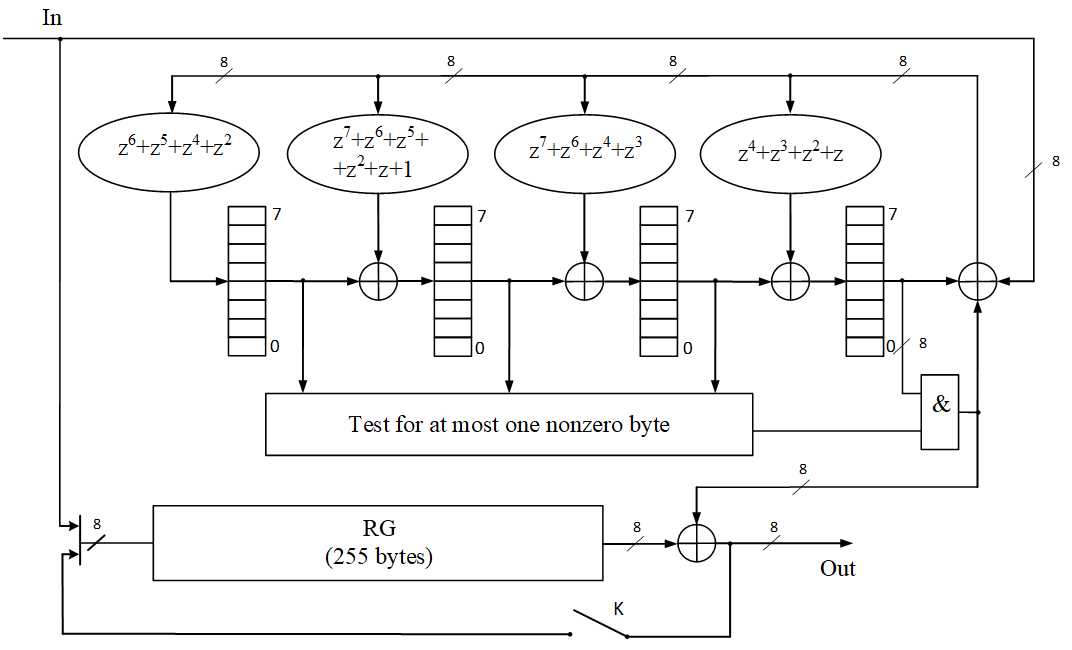

Як приклад на рисунку 1 представлений декодер коду БЧХ (15, 7), що виправляє подвійні помилки.

Рисунок 1 - Декодер (15, 7) коду БЧХ, що виправляє подвійні помилки (Test for all 0’s or one 1 – перевірка на наявність не більше одного ненульового біта)

Апаратна реалізація кодів БЧХ

Для код Ріда - Соломона, що виправляє s помилок є окремим випадком коду БЧХ. На відміну від більшості поширених циклічних кодів, код Ріда-Соломона є недвійковий, тобто символом цього коду є не один двійковий розряд, а декілька.

Декодер коду Ріда - Соломона аналогічний декодеру коду БЧХ (рис. 1).

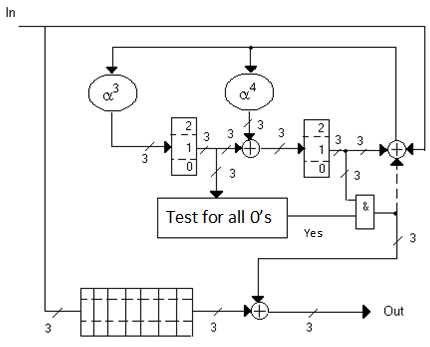

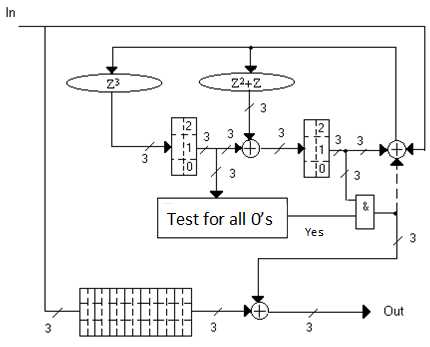

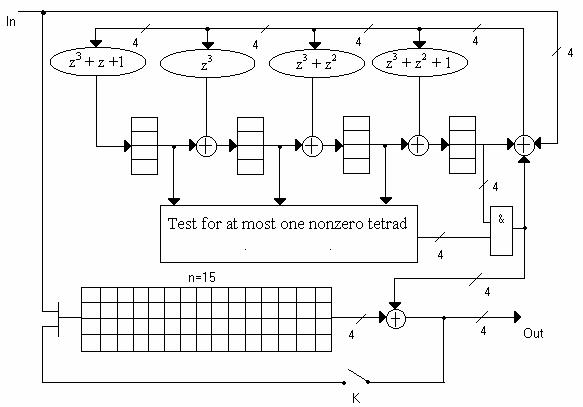

Різниця полягає в інтерпретації елементів: пам’яті - тріади (рис. 2, на рисунку 3 - приклад реалізації декодера з інтерлівінгом коду), тетради (рис. 4), пентади, гексади, гептади, огдоади (рис.5), еннеади, декади; помножувачів на константу і суматорів.

Рисунок 2 - Декодер (7, 5) коду Ріда-Соломона, що виправляє одиночні помилкові тріади (Test for all 0’s – перевірка на всі нулі)

Рисунок 3 - Декодер для посимвольного інтерлівінгу (7,5) коду Ріда-Соломона з параметром інтерлівінгу j=2 (Test for all 0’s – перевірка на всі нулі)

Рисунок 4 - Декодер (15, 11) коду Ріда-Соломона, що виправляє подвійні помилкові тетради (Test for at most one nonzero tetrad – перевірка на наявність не більше однієї ненульовий тетради)

Рисунок 5 - Декодер (255, 251) коду Ріда-Соломона, що виправляє подвійні помилкові байти (Test for at most one nonzero byte – перевірка на наявність не більше одного ненульового байта)

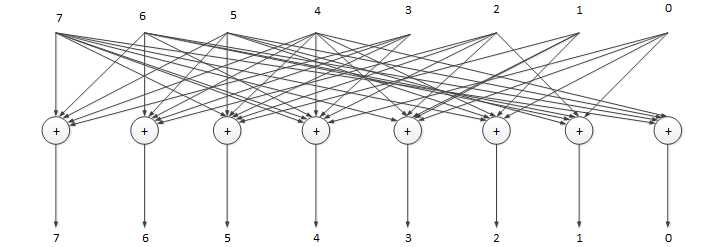

Для побудови декодера на елементах двійковій логіки необхідно помножувачі на константу представити у вигляді суматорів за модулем два. Вони будуються на основі приведення за модулем генераторного полінома відповідного поля Галуа добутку коефіцієнта помножувача на константу і елемента поля в загальному вигляді.

За отриманим залишком від ділення будується схема помножувача на константу. Інші елементи кодера і декодера для апаратної реалізації (255, 251) коду Ріда-Соломона на елементах двійковій логіки не потребують будь-яких спеціальних розрахунків або методів побудови.

Рисунок 6 - Реалізація помножувача на константу для псевдозмінної X3 на елементах двійкової логіки

Основне завдання рисунка 6 - дати загальне уявлення реалізації помножувача на суматорах за модулем два.

Розглянуті способи декодування і перетворення помножувачів можуть бути застосовні не тільки для даного коду, але також для будь-яких кодів Ріда-Соломона, що виправляють одиночні або подвійні помилки, з посимвольним інтерлівінгом і /або укорочених.

Розглянуті варіанти реалізації кодів БЧХ та Ріда-Соломона мають простий спосіб декодування (виловлювання помилок), були проілюстровані загальні риси і відмінності їх декодерів. Тому в даний час вони широко поширені як в апаратній, так і в програмній реалізації. Крім того, розглянуті варіанти можна використовувати для методу посимвольного інтерлівінгу. Багато питань, пов’язані з побудовою кодів Ріда-Соломона і з алгеброю полів Галуа, стають більш зрозумілими при ілюстрації їх конкретними прикладами реалізації.

Альтернативні методи компактного тестування на основі методів циклічного кодування

Одним із способів підвищення тестопридатності НВІС мікропроцесорів, пристроїв на ПЛІС є застосування вбудованих засобів контролю, що реалізують методи компактного тестування. Метод наскрізного зсувного регістру (LSSD - level sensitive scan design) - інший широко відомий спосіб зниження трудомісткості тестування дискретних пристроїв. Метод LSSD зводить задачу тестування до перевірки декількох регістрів зсуву і комбінаційних схем. Найбільш сумісним з методом LSSD з широкого ряду методів компактного тестування є сигнатурний аналіз, оскільки основою аналізатора тестових реакцій (АТР) в цьому випадку є регістр зсуву з лінійними зворотними зв’язками (РЗЛЗЗ). За допомогою незначних апаратних витрат зсувні регістри перетворюються в РЗЛЗЗ, які виконують роль генераторів тестових послідовностей (ГТП) і АТР для тестування комбінаційних схем (КС). Реалізація методів компактного тестування ставить задачу визначення достовірності результатів контролю. В роботі [3] розглядаються питання комплексної оцінки достовірності тестування КС при застосуванні ГТП і АТР у вигляді РЗЛЗЗ, яка враховує не тільки здібності АТР виявляти помилки, але також структуру ГТП і характер тестових реакцій об’єкта діагностики. Зокрема, отримано висновок про значну залежність ефективності сигнатурного аналізу від вибору того чи іншого поєднання генераторних поліномів РЗЛЗЗ ГТП і АТР. Дана робота є продовженням досліджень в цьому напрямку.

Отримані результати можуть бути реалізовані на основі РЗЛЗЗ як в конфігурації Галуа (наприклад, рис. 1-5), так і в конфігурації Фібоначчі [10]. Приклад РЗЛЗЗ ГТП в конфігурації Фібоначчі представлений на рисунку 7.

Рисунок 7 - РЗЛЗЗ ГТП в конфігурації Фібоначчі

Більш детально з результатами роботи можна ознайомитися в наступних публікаціях [11 -22].

Висновок

В роботі запропоновані такі альтернативні методи циклічного кодування і апаратної реалізації кодера і декодера: варіанти апаратної реалізації кодів БЧХ та Ріда-Соломона, що виправляють одиночні і подвійні помилки (пакети помилок) і використовують синдромний метод декодування; метод укорочення і апаратна реалізація циклічних кодів на основі подвійних поліномів; альтернативний метод поділу поліномів; метод укорочення і апаратна реалізація циклічних кодів на основі альтернативного ділення поліномів.

Виконано аналіз ефективності компактного тестування на основі циклічного кодування з локалізацією помилок у вихідний тестової реакції перевіряєтьсякомбінаційної схеми. Запропоновано метод аналітичного розрахунку сигнатур для вичерпного тестування комбінаційних схем при реалізації генератора тестових послідовностей і аналізатора тестових реакцій на основі регістрів зсуву з лінійними зворотними зв’язками. Розглядаються аналізатори тестових реакцій, побудовані на основі циклічних кодів Хеммінга, Боуза-Чоудхурі-Хоквінгема, Бартона, Ріда-Соломона, що дозволяють локалізувати помилки в тестовій реакції. Отримано оцінку міри ефективності компактного тестування комбінаційних схем, на основі якої запропоновано рекомендації щодо вибору генераторних поліномів регістрів зсуву з лінійними зворотними зв’язками для різних варіантів компактного тестування з локалізацією помилок. Отримані результати можуть знайти застосування для вбудованого самотестування або зовнішнього тестового обладнання засобів обчислювальної техніки.

При написанні даного реферату магістерська робота ще не завершена. Остаточне завершення: червень 2018 року. Повний текст роботи та матеріали по темі можуть бути отримані у автора або його керівника після зазначеної дати.

Перелік посилань

- Белл Д. Грядущее постиндустриальное общество. Опыт социального прогнозирования: Пер. с англ. 2-е изд., испр. и доп. – М.: Academia, 2004. – 788 с.

- Гладких А. А. Методы эффективного декодирования избыточных кодов и их современные приложения / А. А. Гладких, Р. В. Климов, Н. Ю. Чилихин. – Ульяновск : УлГТУ, 2016. – 258 с.

- Улучшение радиационной стойкости памяти с помощью помехоустойчивых кодов / А.Н. Ершов [и др.] // Ракетно-космическое приборостроение и информационные системы. 2014, том 1, выпуск 4, c. 42–49.

- Ярмолик В.Н. Тестовое диагностирование аппаратного и программного обеспечения вычислительных систем / В.Н. Ярмолик, А.А. Иванюк // Доклады БГУИР, № 2 (80), 2014. – С.127–142.

- Richard E.Blahut. Algebraic Codes for Data Transmission/ Cambridge University Press, 2012. – 498 p.

- Рахман П.А. Основы защиты данных от разрушения. Коды Рида-Соломона/ Интернет-ресурс. – Режим доступа: https://bugtraq.ru...

- Питерсон У. Коды, исправляющие ошибки / У. Питерсон, Э. Уэлдон. – М.: Мир, 1976. – 595 с.: ил.

- Design of RS (255, 251) Encoder and Decoder in FPGA / Anindya Sundar Das, Satyajit Das and Jaydeb Bhaumik // International Journal of Soft Computing and Engineering (IJSCE) ISSN: 2231-2307, Volume-2, Issue-6, January 2013, pp. 391–394.

- Ярмолик В.Н. Эффективность сигнатурного анализа в самотестирующихся СБИС / В.Н. Ярмолик, Е.П. Калоша // Электрон. моделирование. 1992. 14, №3. С.51–56.

- Frohwerk R.A. Signature analysis, Hewlett-Packard J. 28, Nr. 9, 1977. – pp. 2–8.

- Дяченко В.О. Исследование способов проектирования кодов Рида-Соломона / В.О. Дяченко., Ю.Е. Зинченко, О.Н. Дяченко // Інформаційні управляючі системи та комп’ютерний моніторинг (ІУС КМ-2014) : V Всеукраїнська науково-технічна конференція студентів, аспірантів та молодих вчених, 22-23 квітня 2014 р., м. Донецьк : зб. доп. / Донец. націонал. техн. ун-т; редкол. В.А.Світлична. – Донецьк: ДонНТУ, 2014. – в 2 тт. – т.2. – С. 72–78. – Режим доступа: http://ea.donntu.ru...

- Дяченко В.О. Анализ способов реализации кодов Рида-Соломона, исправляющих двойные ошибки / В.О. Дяченко, О.Н. Дяченко // Современные тенденции развития и перспективы внедрения инновационных технологий в машиностроении, образовании и экономике: материалы Международной научно-практической конференции (Азов, 19 мая 2014 г.). – Ростов н/Д, ДГТУ, 2014. – С. 18–22. – Режим доступа: http://ea.donntu.ru...

- Дяченко О.Н. Аппаратная реализация кодов БЧХ и кодов Рида-Соломона / О.Н. Дяченко, В.О. Дяченко // Современные тенденции развития и перспективы внедрения инновационных технологий в машиностроении, образовании и экономике: материалы IV Международной научно-практической конференции (Азов, 25 мая 2017 г.). – Ростов н/Д, ДГТУ, 2017. – С. 30–34. – Режим доступа: https://elibrary.ru...

- Дяченко В.О. Циклическое кодирование цифровой информации на основе двойственных полиномов / В.О. Дяченко, О.Н. Дяченко // Современные тенденции развития и перспективы внедрения инновационных технологий в машиностроении, образовании и экономике: материалы II Международной научно-практической конференции (Азов, 19 мая 2015 г.) [Электронный ресурс]. – Ростов н/Д, ДГТУ, 2015. – С. 71–76. – Режим доступа: http://ea.donntu.ru...

- Дяченко В.О. Особенности применения двойственных полиномов для аппаратной реализации циклических кодов / В.О. Дяченко, О.Н. Дяченко // Информационные управляющие системы и компьютерный мониторинг в рамках форума “Инновационные перспективы Донбасса” (ИУС КМ-2015): VI Международная научно-техническая конференция студентов, аспирантов и молодых ученых, 20-22 мая 2015, г.Донецк: / Донец. национал. техн. ун-т; сост.: К.Н.Маренич (председатель) и др. – Донецк: ДонНТУ, 2015. – С. 130–136. – Режим доступа: http://ea.donntu.ru...

- Дяченко О.Н. Альтернативный метод укорачивания циклических кодов / О.Н. Дяченко, В.О. Дяченко // Информатика, управляющие системы, математическое и компьютерное моделирование - 2016 в рамках в рамках II Международного Научного форума Донецкой Народной Республики (ИУСМКМ-2016): VII Международная научно-техническая конференция студентов, аспирантов и молодых ученых, 26-27 мая 2016, г.Донецк: / Донец. национал. техн. ун-т; сост.: К.Н.Маренич (председатель) и др. – Донецк: ДонНТУ, 2016. – С. 328–334. – Режим доступа: http://ea.donntu.ru...

- Дяченко О.Н. Альтернативный метод укорачивания циклических кодов / О.Н. Дяченко, В.О. Дяченко // Электронные информационные системы. 2017. № 1 (12). С. 94–100. – Режим доступа: https://elibrary.ru/item.asp?id=28883888, http://ea.donntu.ru...

- Дяченко В.О. Альтернативный способ построения укороченных кодов Файра / В.О. Дяченко, О.Н. Дяченко // Компьютерная и программная инженерия. Сборник материалов международной научно-технической конференции студентов, аспирантов и молодых учёных 15-16 декабря 2015 года . - Донецк, ДонНТУ - 2015. – С. 86–89. – Режим доступа: http://ea.donntu.ru...

- Дяченко О.Н. Исследование эффективности компактного тестирования на основе методов циклического кодирования / О.Н. Дяченко, Ю.Е. Зинченко, В.О. Дяченко // Информатика, управляющие системы, математическое и компьютерное моделирование в рамках III форума

Инновационные перспективы Донбасса

(ИУСМКМ - 2017): VIII Международная научно-техническая конференция, 26 мая 2017, г. Донецк: / Донец. национал. техн. ун-т; редкол. Ю.К. Орлов и др. – Донецк: ДонНТУ, 2017. – С. 313–319. – Режим доступа: http://iuskm.donntu.ru... - Дяченко О.Н. Применение методов помехоустойчивого кодирования для компактного тестирования цифровых схем / О.Н. Дяченко, Ю.Е. Зинченко, В.О. Дяченко // Информатика и кибернетика. Донецк: ДонНТУ, 2017. № 3(9). – С. 55–59. – Режим доступа: http://infcyb.donntu.ru...

- Дяченко В.О. Компактное тестирование на основе минимальных полиномов в цифровых схемах с самотестированием / В.О. Дяченко, О.Н. Дяченко // V Международная научно-техническая конференция “Современные информационные технологии в образовании и научных исследованиях” СИТОНИ – 2017, 20 ноября 2017 – Донецк: ДонНТУ, 2017. – Режим доступа: http://pm.conf.donntu.ru...