Реферат

Содержание

- Введение

- 1. Актуальность темы

- 2. Цель и задачи исследования, планируемые результаты

- 3. Анализ существующих систем распознавания звуков

- 4. Использование нейронных сетей на базе ПЛИС

- 5. Обзор средств разработки

- Выводы

- Список источников

Введение

На сегодняшний день нейросети достигли немалого успеха в области распознавания изображений и видео. Это стало возможным благодаря массивным базам данных изображений с размеченными объектами. Проведя анализ на фотографии или видеоролики, компьютер может практически безошибочно определить место, либо обьект находящийся в кадре. Возможность определения места действия по звукам — такая же важная задача, как и определение места по видеоматериалу. В случаях плохой видимости в связи загрязнения камеры, либо тумана камера не даст достаточное количество данных для анализа ситуации. Однако, если микрофон работает, будет большее количество данных система сможет лучше проанализировать ситуацию.

В последние годы стало активно развиваться направление Компьютерный слух

(Machine hearing). В рамках этого направления разрабатываются модели машинного восприятия и обработки звука и, в частности, речи. Эти модели могут использоваться в актуальной сфере социальной и общей робототехники. Представьте себе симпатичного робота в супермаркете, больнице или зале вокзала, который узнает ваши шаги, подъезжает к вам и начинает с вами общаться, давать советы, отвечать на ваши вопросы.

Технологии машинного слуха могут быть задействованы также в таких задачах, как автоматическая идентификация рекламных брендов и слоганов; анализ стенограмм заседаний; звуковое дополнение антиплагиатних систем; автоматическая группировка медиа новостей по ключевым словам и рубрикам т.п. Несмотря на значительный прогресс в области распознавания речи, достигнутый благодаря мобильным приложениям Google и Apple, развитие компьютерного слуха имеет свои особенности и требует разработки более глубоких моделей и методов.

1. Актуальность темы

Одно из основных достоинств нейронных сетей — одновременная обработка большого количества сигналов. Большая часть реализуемых в настоящее время сетей — программная эмуляция, работающая на персональных компьютерах и специализированных серверах [4]. Помимо достоинств, таких как простота, достигаемая программной эмуляцией, и повсеместная доступность персональных компьютеров, эти станции имеют и недостатки, например, избыточность и большую потребляемую мощность. Скорость работы нейронной сети, построенной таким образом, будет напрямую зависеть от ее размерности, так как частота работы единого центрального процессора будет делиться на все использующиеся в данной сети нейроны.

На сегодняшний день можно выделить два типа реализации нейронных сетей:

- программные нейронные сети — нейронная сеть разрабатывается при помощи одного из языков программирования, вся логика работы программы описывается программно;

- аппаратно-реализованные нейронные сети — нейронная сеть представляет собой специально разработанную микросхему, в которой все алгоритмы работы реализованы на аппаратном уровне.

Наибольшую распространенность приобрели программно реализованные искусственные нейронные сети. Данную популярность можно объяснить простотой разработки данного типа сетей, в результате чего появилось большое количество библиотек для разработки и обучения нейронных сетей, что сделало программные нейронные сети еще более распространенными. Так же важным аргументом пользу программной реализации нейронной сети является простота их внедрения и применения в компьютерных системах, данный эффект объясняется отсутствием необходимости модернизации аппаратного обеспечения [10].

Также существует метод реализации, позволяющий использование преимуществ обоих типов нейронных сетей. Данный способ заключается в реализации сети при помощи программируемой логической интегральной схемы (ПЛИС) [1,2]. Принцип работы ПЛИС заключается в возможности программировать архитектуру системы, т. е. ее аппаратную составляющую. Иными словами, программно изменять аппаратную структуру системы. В ПЛИС возможно создание программное создание простых модулей и объединение их в большую сеть. С другой стороны ПЛИС поддерживает полностью параллельные вычисления, в отличии от псевдо-параллельных, которые используются в обычных компьютерах. Еще одним достоинством ПЛИС является развитая периферия, включающая широкий набор современных компьютерных интерфейсов (включая высокоскоростные), что позволяет проводить отладку нейронной сети, а также избавляет от проблемы интеграции сети в компьютерную систему.

Общее вид нейрона представляет набор следующих блоков: сумматор, умножитель, логическую функцию активации и блок хранения данных, а также веса связей. Отдельные нейроны объединяются в слои, которые образуют сеть. Данная структура легко реализуется в ПЛИС. А возможность достижения параллельной работы нейронов, основанной на аппаратной структуре ПЛИС, позволяет добиться большего быстродействия, чем у программных реализаций [3].

2. Цель и задачи исследования, планируемые результаты

Основная цель работы — разработка архитектуры нейронной сети на базе FPGA, ориентированной на распознавание и анализ звуковых сигналов.

Для достижения данной цели необходимо выполнение следующих задач:

- Анализ существующих алгоритмов обработки звуковых сигналов.

- Анализ существующих нейросетей для обработки звуковых сигналов.

- Анализ возможностей реализации нейросети на базе FPGA.

- Обработка полученных результатов.

- Непосредственная разработка архитектуры нейронной сети.

Исследование направленно на изучение систем компьютерного распознавания звуковых сигналов, что позволит автоматизировать анализ окружения.

Результатом работы будет нейронная сеть на базе FPGA направленная на решение задачи распознавания звуковых сигналов.

3. Анализ существующих систем распознавания звуков

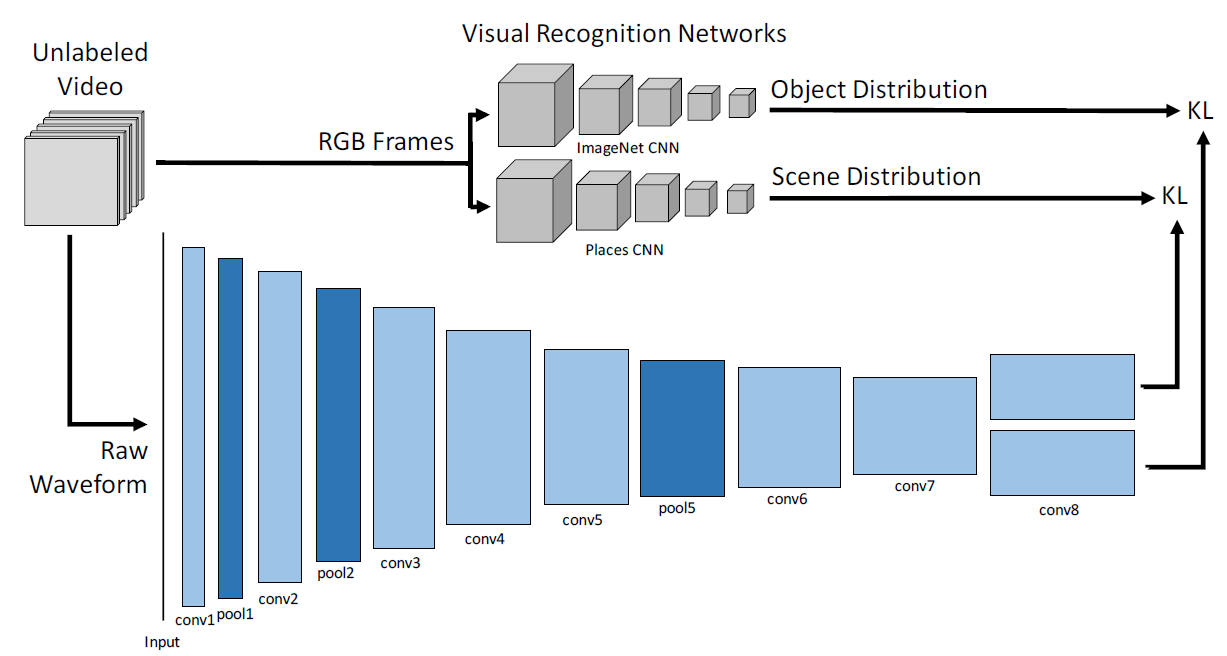

Специалисты из Лаборатории информатики и искусственного интеллекта (CSAIL) Массачусетского технологического института совершили качественный скачек в области анализа и обработки звуковых сигналов, разработав систему машинного обучения SoundNet. На рисунке 1 представлен общий алгоритм распознавания звука.

Рисунок 1 — Общий алгоритм распознавания звука нейросетью

(анимация: 21 кадр, замкнутый цикл повторения, 74 KB)

Сотрудники CSAIL использовали метод естественной синхронизации между машинным зрением и машинным слухом, научив нейросеть автоматически извлекать звуковую репрезентацию объекта с неразмеченного видеоматериала. При обучении нейросети были использованы примерно 2 млн видеороликов Flickr , общим объемом 26 ТБ, а также база аннотированных звуков — 50 категорий и примерно 2000 образцов. На рисунке 2 представлена архитектура нейросети SoundNet.

Рисунок 2 — Архитектура нейросети SoundNet [5]

Система показывает высокий результат при работе в автономном режиме. Система классифицирует минимум три стандартные акустических сцены, на которых ее тестировали разработчики системы. Более детальный анализ нейросети показал, что система самостоятельно распознавать звуки характерные для различных сцен. Данный факт вызвал удивление, так как разработчики не предоставляли её образцов для распознавания конкретно этих объектов. Используя базу неразмеченных видеоматериалов нейросеть самостоятельно определила, какой сцене соответствует звук ликующей толпы (стадион) и птичий щебет (лужайка или парк). Одновременно со сценой нейросеть распознаёт и конкретный объект, который является источником звука.

Для проверки системы SoundNet использовались две стандартные базы данных звуковых записей. Результат проверки нейросети оказался на 13-15% более точным при распознавании объектов, чем лучшая из существующих программ. Точность SoundNet составляет 92% при наборе данных в 10 различными категориях звуков. При увеличении количества категорий до 50 точность работы системы составляет 74%. Для сравнения, на тех же наборах данных люди показывают точность распознавания, в среднем, 96% и 81% [5].

4. Использование нейронных сетей на базе ПЛИС

На сегодняшний день большую часть вычислений связанных с нейронными сетями выполняют графические процессоры. В дополнение к вычислительной мощности, эти GPU-системы также потребляют большое количество энергии.

Microsoft развернула различные крупные глобальные центры обработки данных, которые выполняют огрмное количество вычислений за счет использования сверточных нейронных сетей (СНС или CNN). CNN — это тип машинного обучения, который анализирует изображение таким образом, чтобы изучать функции, которые могут помочь компьютеру идентифицировать шаблоны в изображении.

Глубокое обучение с использованием CNN довольно трудоемкий процесс, в связи с этим, центры обработки данных Microsoft столкнулись с трудностями при использовании GPU в качестве единственного вычислительного средства, т. к. поскольку они имели ограниченную применимость и большое энергопотребление. В 2014 году была протестирована FPGA Altera Stratix 5 для обработки алгоритмов ранжирования поиска. Результаты показали увеличение производительности почти в 2 раза, в связи с этим было принято решение использовать данную архитектуру для тестирования ускорителя CNN.

Ускоритель на основе программируемых логических интегральных схем (ПЛИС) FPGA был разработан для эффективного расчета прямого распространения сверточных слоев. Таким образом, ускоритель CNN должен иметь возможность принимать входное изображение и обрабатывать несколько сверточных слоев подряд. При разработке архитектура должна включать несколько факторов. Поскольку система должна обрабатывать несколько уровней, вычислительный движок системы должен быть настроен для поддержки этих слоев. Управление памятью имеет решающее значение, поэтому проект должен включать эффективную схему буферизации данных и сеть повторного распространения на кристалле. Наконец, архитектура проекта должна иметь возможность содержать пространственно распределенный массив элементов обработки, которые можно легко масштабировать до тысяч единиц. Это позволяет ускорителю CNN принять входное изображение, а затем выполнить анализ многочисленных сверточных слоев подряд. Метод, в котором система обрабатывает сверточные слои, сильно зависит от используемого оборудования. ПЛИС FPGA стали явным выбором для достижения большей эффективности обработки [6].

При рассмотрении частных случаев производительность отдельных FPGA ниже производительности GPU.Для работы с CNN были использованы Altera Arria 10. Данный FPGA крмплекс позволяет обрабатывать 233 изображения в секунду при потребляемой мощности около 25 Вт. Для сравнения, графический процессор NVIDIA Tesla K40 может обрабатывать от 500 до 824 изображений в секунду, при потребляемой мощности 235 Вт для обработки изображений с такой скоростью. Отдельные FPGA показывают меньшую скорость существенно меньшем потреблении энергии. Однако основным преимуществом FPGA является масштабируемость. Как минимум три FPGA могут быть соединены вместе, чтобы обеспечить такую же мощность обработки, что и Tesla K40, при одновременном снижении выходной мощности примерно на 30%.

FPGA Arria 10 обеспечивает до 40 GFLOPS на ватт. Arria 10 использует OpenCL, разнвидность VHDL, для кодирования своих блоков обработки цифрового сигнала с плавающей точкой IEEE754. Arria 10 имеет гибкий путь передачи данных, который обходит внешнюю память и позволяет ядрам OpenCL передавать данные напрямую друг другу. В дополнение к гибкому пути данных, Arria 10 поддерживает аппаратные операции с фиксированной плавающей точкой, как для умножения, так и для сложения. Это позволяет FPGA содержать больше логики и обеспечивать более высокую тактовую частоту. Благодаря этим улучшениям в функциональности аппаратного и программного обеспечения, Arria 10 способна превзойти существующие платформы на основе графических процессоров [7].

В тестах, выполненных Microsoft с использованием массива Arria 10s для вычисления функций CNN, команда наблюдала примерно 30-кратный прирост производительности.

С улучшением производительности ПЛИС FPGA центры обработки данных могут использовать и их для удовлетворения потребностей в вычислительных возможностях и энергопотреблении. Это позволяет эмулировать глубокое обучение путем последовательной обработки нескольких слоев сверточных нейронных сетей.

5. Обзор средств разработки

Xilinx ISE (Integrated Synthesis Environment) — программное обеспечение, созданное фирмой Xilinx для синтеза и анализа конструкций HDL, позволяющий разработчику синтезировать (компилировать

) свои проекты, выполнять анализ работы во времени, анализировать RTL-диаграммы и имитировать реакцию модуле на разные сигналы [8].

Xilinx ISE - это среда проектирования для продуктов FPGA от Xilinx и тесно связана с архитектурой таких чипов и не может использоваться с продуктами FPGA от других поставщиков. Xilinx ISE в основном используется для синтеза и проектирования схем, в то время как ISIM или логический имитатор ModelSim используются для тестирования на уровне системы. Другие компоненты, поставляемые с Xilinx ISE, включают Embedded Development Kit (EDK), комплект разработки программного обеспечения SDK и ChipScope Pro.

Xilinx ISE рядом особенностей, главной из которых является возможность создания файла прошивки для загрузки в FPGA-комплекс. Это и является главной особенностью данной среды, так как она позволяет не только моделировать описанные схемы и программы, но и тестировать их в реальных условиях.

Для создания файла прошивки необходимо пройти ряд шагов:

- проверка синтаксиса;

- синтез;

- имплементацию дизайна;

- создание файла прошивки.

Имплементация также разбивается на несколько этапов, в течении которых, строится модель проекта на логических элементах. В связи с большим количеством этапов создание файла прошивки занимает долгое время, что является большим недостатком данной среды.

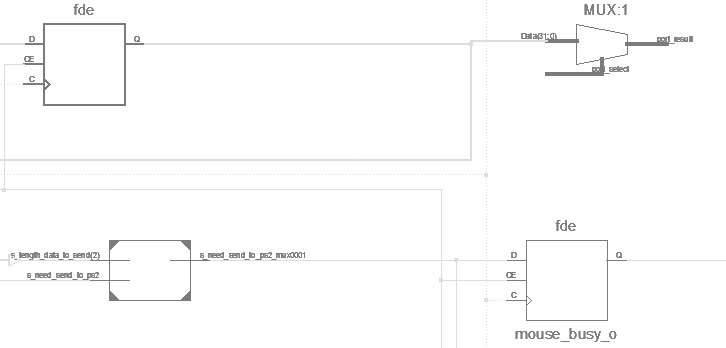

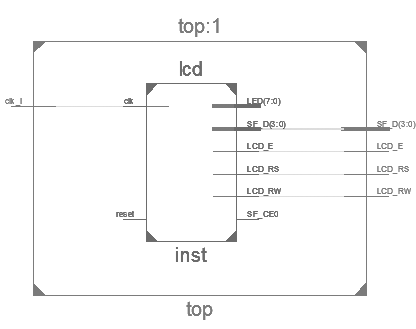

После фазы синтеза HDL процесса синтеза возможно отобразить схематическое представление синтезированного исходного файла (RTL-схема). На этой схеме показано представление предварительно оптимизированной конструкции с использованием общих элементов, таких как сумматоры, умножители, счетчики и логические элементы И ИЛИ. Просмотр этой схемы может помочь выявить проблемы дизайна на ранней стадии процесса проектирования. Пример семы представлен на рисунке 3.

Рисунок 3 — Пример RTL-схемы

Еще до погрузки программы в FPGA-комплекс ISE знает количество логических элементов, а также сложных структур, необходимых для построения схемы, исполняющей написанную программу. Эти данные выдаются пользователю в виде таблицы и позволяют определить, в какой момент пользователь превысит имеющийся объем элементов.

Также, в отличии от Active-HDL, в данной среде более четко прослеживается понятие иерархии и наследования в случаях использования одних модулей другими. Это заметно как в файловом меню, так и при анализе схемы. Пример меню и схемы представлены на рисунках 4 и 5 соответственно.

Рисунок 4 — Файловое меню проекта

Рисунок 5 — Общая схема проекта

На рисунках отчетливо видно, что если один элемент использует другой, то он находится на более высоком уровне в иерархии, что верно для всех языков описания аппаратуры.

Данная среда обладает рядом недостатков, в числе которых низкая скорость работы, а в дополнение к этому данная среда не является целостной, она состоит из пакета программ, взаимодействующих друг с другом. В связи с этим размеры данного программного обеспечения также довольно велики. Еще одним недостатком является тот факт, что ISE не может самостоятельно отслеживать поведение прошивки внутри платы. Для этого используется отдельное программное обеспечение ChipScope Pro [9]. Но, несмотря на ряд недостатков, среда широко используется для работы с FPGA.

Выводы

В результате научно-исследовательской работы были собраны и изучены материалы по вопросам, связанным с темой магистерской работы.

В исследовании были проанализированы аналоги систем распознавания звуков на базе нейронных систем, возможность реализации нейронных сетей FPGA, а также среда разработки, специализированная в области работы с FPGA.

Благодаря изученным материалам можно сделать вывод, что существует малое количество специализированных приложений для распознавания источника звука. Также исследование показало, что реализация нейронных сетей на базе FPGA является оптимальным решением при решении локальных задач.

Замечания

На момент написания данного реферата магистерская работа еще не завершена. Предполагаемая дата завершения: май 2019 г. Полный текст работы, а также материалы по теме могут быть получены у автора или его руководителя после указанной даты.

Список источников

- Введение в архитектуры нейронных сетей [Электронный ресурс]. — Режим доступа: https://habr.com/company/oleg-bunin/blog/340184/. — Заглавие с экрана. — (Дата обращения: 05.12.2018).

- Nurvitadhi E. et al. Accelerating recurrent neural networks in analytics servers: Comparison of FPGA, CPU, GPU, and ASIC // Field Programmable Logic and Applications (FPL), 2016 26th International Conference on. — IEEE, 2016. — P. 1–4.

- Азаров А. Б. Обзор существующей концепции и возможностей реализации нейронных сетей / А. Б. Азаров, В. С. Константинов, Ю. Е. Зинченко, Т. А. Зинченко // Материалы студенческой секции IX Международной научно-технической конференции «Информатика, управляющие системы, математическое и компьютерное моделирование» (ИУСМКМ-2018). — Донецк: ДонНТУ, 2018. — С. 390-394.

- Дедегкаев Альберт Гагеевич, Рыжков Александр Александрович Метод проектирования структуры нейронных сетей на основе клеточных автоматов // Universum: технические науки. 2013. №1. URL: https://cyberleninka.ru/article/n/metod-proektirovaniya-struktury-neyronnyh-setey-na-osnove-kletochnyh-avtomatov (дата обращения: 23.12.2018).

- Машинный слух. Нейросеть SoundNet обучили распознавать объекты по звуку [Электронный ресурс]. — Режим доступа: https://habr.com/post/399659/. — Заглавие с экрана. — (Дата обращения: 05.12.2018).

- Использование ПЛИС FPGA в создании нейронных сетей [Электронный ресурс]. — Режим доступа: http://digitrode.ru/computing-devices/fpga/1045-ispolzovanie-plis-fpga-v-sozdanii-neyronnyh-setey.html. — Заглавие с экрана. — (Дата обращения: 05.12.2018).

- Intel PAC c FPGA Stratix 10 SX — ускоритель для больших задач [Электронный ресурс]. — Режим доступа: https://habr.com/company/intel/blog/425187/. — Заглавие с экрана. — (Дата обращения: 05.12.2018).

- Xilinx ISE [Электронный ресурс]. — Режим доступа: http://we.easyelectronics.ru/plis/osvaivaem-xilinx-ise.html. — Заглавие с экрана. — (Дата обращения: 05.12.2018).

- ChipScope Pro and the Serial I/O Toolkit [Электронный ресурс]. — Режим доступа: https://www.xilinx.com/products/design-tools/chipscopepro.html. — Заглавие с экрана. — (Дата обращения: 05.12.2018).

- Нейронные сети,

вредные

советы [Электронный ресурс]. — Режим доступа: https://habr.com/post/211610/. — Заглавие с экрана. — (Дата обращения: 05.12.2018).