Реферат

Зміст

- Вступ

- 1. Актуальність теми

- 2. Мета і задачі дослідження та заплановані результати

- 3. Аналіз існуючих систем розпізнавання звуків

- 4. Використання нейронних мереж на базі ПЛІС

- 5. Огляд засобів розробки

- Висновки

- Перелік посилань

Вступ

На сьогоднішній день нейромережі досягли чималого успіху в області розпізнавання зображень і відео. Це стало можливим завдяки масивним баз даних зображень з розміченими об'єктами. Провівши аналіз фотографії або відеоролику, комп'ютер може практично безпомилково визначити місце, або об'єкт який знаходиться в кадрі. Можливість визначення місця дії за звуком - така ж важлива задача, як і визначення місця по відеоматеріалу. У випадках поганої видимості в зв'язку забруднення камери, або туману камера не дасть достатню кількість даних для аналізу ситуації. Однак, якщо мікрофон працює, буде більша кількість даних система зможе краще проаналізувати ситуацію.

В останні роки активно розвивається напрямок Комп'ютерний слух

(Machine hearing). В рамках цього напрямку розробляються моделі машинного сприйняття і обробки звуку і, зокрема, мови. Ці моделі можуть використовуватися в актуальній сфері соціальної та загальної робототехніки. Уявіть собі симпатичного робота в супермаркеті, лікарні або залі вокзалу, який дізнається ваші кроки, під'їжджає до вас і починає з вами спілкуватися, давати поради, відповідати на ваші запитання.

Технології машинного слуху можуть бути задіяні також у таких завданнях, як автоматична ідентифікація рекламних брендів і слоганів; аналіз стенограм засідань; звукове доповнення антіплагіатніх систем; автоматичне групування медіа новин за ключовими словами і рубриками т.п. Незважаючи на значний прогрес в області розпізнавання мови, досягнутий завдяки мобільним додаткам Google і Apple, розвиток комп'ютерного слуху має свої особливості і вимагає розробки більш глибоких моделей і методів.

1. Актуальність теми

Одна з основних переваг нейронних мереж — одночасна обробка великої кількості сигналів. Велика частина реалізованих в даний час мереж — програмна емуляція, що працює на персональних комп'ютерах і спеціалізованих серверах [4]. Крім достоїнств, таких як простота, що досягається програмної емуляції, і повсюдна доступність персональних комп'ютерів, ці станції мають і недоліки, наприклад, надмірність і велику споживану потужність. Швидкість роботи нейронної мережі, побудованої таким чином, буде прямо залежати від її розмірності.

На сьогоднішній день можна виділити два типи реалізації нейронних мереж:

- програмні нейронні мережі — нейронна мережа розробляється за допомогою однієї з мов програмування, вся логіка роботи програми описується програмно;

- апаратно-реалізовані нейронні мережі — нейронна мережа являє собою спеціально розроблену мікросхему, в якій всі алгоритми роботи реалізовані на апаратному рівні.

Найбільшу поширеність придбали програмно реалізовані штучні нейронні мережі. Дану популярність можна пояснити простотою розробки даного типу мереж, в результаті чого з'явилася велика кількість бібліотек для розробки і навчання нейронних мереж, що зробило програмні нейронні мережі ще більш поширеними. Так само важливим аргументом є простота їх впровадження і застосування в комп'ютерних системах, даний ефект пояснюється відсутністю необхідності модернізації апаратного забезпечення [10].

Також існує метод реалізації, що дозволяє використання переваг обох типів нейронних мереж. Даний спосіб полягає в реалізації мережі за допомогою програмованої логічної інтегральної схеми (ПЛІС) [1,2]. Принцип роботи ПЛІС полягає в можливості програмувати архітектуру системи, її апаратну складову. Іншими словами, програмно змінювати апаратну структуру системи. У ПЛІС можливе створення програмне створення простих модулів і об'єднання їх у велику мережу. З іншого боку ПЛІС підтримує повністю паралельні обчислення, на відміну від псевдо-паралельних, які використовуються в звичайних комп'ютерах. Ще однією перевагою ПЛІС є розвинена периферія, що включає широкий набір сучасних комп'ютерних інтерфейсів (включаючи високошвидкісні), що дозволяє проводити налагодження нейронної мережі, а також позбавляє від проблеми інтеграції мережі в комп'ютерну систему.

Загальна вид нейрона представляє набір наступних блоків: акумулятор, умножитель, логічну функцію активації і блок зберігання даних, а також ваги зв'язків. Окремі нейрони об'єднуються в шари, які утворюють мережу. Дана структура легко реалізується в ПЛІС. А можливість досягнення паралельної роботи нейронів, заснованої на апаратній структурі ПЛІС, дозволяє домогтися більшої швидкодії, ніж у програмних реалізацій [3].

2. Мета і задачі дослідження та заплановані результати

Основна мета роботи — розробка архітектури нейронної мережі на базі FPGA, орієнтованої на розпізнавання і аналіз звукових сигналів.

Для досягнення даної мети необхідно виконання наступних завдань:

- Аналіз існуючих алгоритмів обробки звукових сигналів.

- Аналіз існуючих нейромереж для обробки звукових сигналів.

- Анализ возможностей реализации нейросети на базе FPGA.

- Обробка отриманих результатів.

- Безпосередня розробка архітектури нейронної мережі.

Дослідження направлено на вивчення систем комп'ютерного розпізнавання звукових сигналів, що дозволить автоматизувати аналіз оточення.

Результатом роботи буде нейронна мережа на базі FPGA спрямована на вирішення завдання розпізнавання звукових сигналів.

3. Аналіз існуючих систем розпізнавання звуків

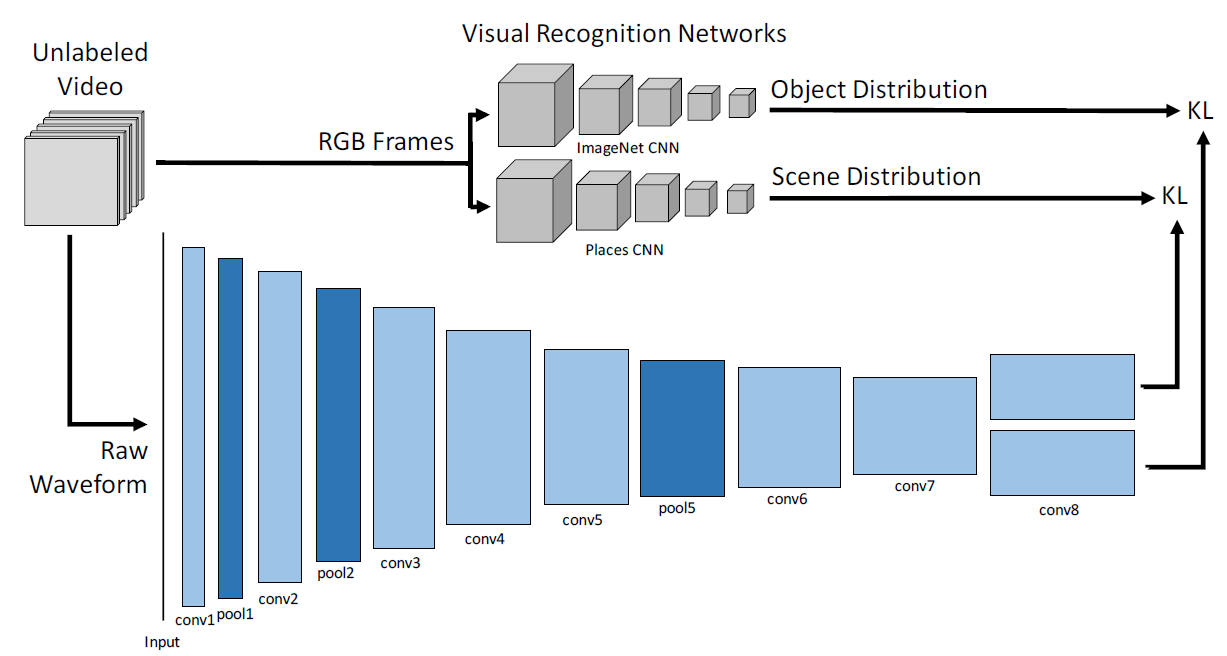

Фахівці з Лабораторії інформатики і штучного інтелекту (CSAIL) Массачусетського технологічного інституту зробили якісний стрибок в області аналізу і обробки звукових сигналів, розробивши систему машинного навчання SoundNet. На рисунку 1 представлено загальний алгоритм розпізнавання звуку.

Рисунок 1 — Загальний алгоритм розпізнавання звуку нейромережею

(анімація: 21 кадр, циклічне повторення, 73 KB)

Співробітники CSAIL використовували метод природної синхронізації між машинним зором і машинним слухом, навчивши нейросеть автоматично отримувати звукову репрезентацію об'єкта з нерозміченого відеоматеріалу. При навчанні нейромережі були використані приблизно 2 млн відеороликів Flickr, загальним обсягом 26 ТБ, а також база анотованих звуків - 50 категорій і приблизно 2000 зразків. На малюнку 2 представлена архітектура нейромережі SoundNet.

Рисунок 2 — Архітектура нейромережі SoundNet [5]

Система показує високий результат при роботі в автономному режимі. Система класифікує мінімум три стандартні акустичних сцени, на яких її тестували розробники системи. Більш детальний аналіз нейромережі показав, що система самостійно розпізнавати звуки характерні для різних сцен. Даний факт викликав подив, так як розробники не надавали її зразків для розпізнавання конкретно цих об'єктів. Використовуючи базу нерозмічену відеоматеріалів нейросеть самостійно визначила, якій сцені відповідає звук радісним натовпом (стадіон) і пташиний щебет (галявина або парк). Одночасно зі сценою нейросеть розпізнає і конкретний об'єкт, який є джерелом звуку.

Для перевірки системи SoundNet використовувалися дві стандартні бази даних звукових записів. Результат перевірки нейромережі виявився на 13-15% більш точним при розпізнаванні об'єктів, ніж найкраща з існуючих програм. Точність SoundNet становить 92% при наборі даних в 10 різними категоріях звуків. При збільшенні кількості категорій до 50 точність роботи системи становить 74%. Для порівняння, на тих же наборах даних люди показують точність розпізнавання, в середньому, 96% і 81% [5].

4. Використання нейронних мереж на базі ПЛІС

На сьогоднішній день більшу частину обчислень пов'язаних з нейронними мережами виконують графічні процесори. На додаток до обчислювальної потужності, ці GPU-системи також споживають велику кількість енергії.

Microsoft розгорнула різні великі глобальні центри обробки даних, які виконують огрмное кількість обчислень за рахунок використання згортальних нейронних мереж (СНС або CNN). CNN - це тип машинного навчання, який аналізує зображення таким чином, щоб вивчати функції, які можуть допомогти комп'ютеру ідентифікувати шаблони в зображенні.

Глибоке навчання з використанням CNN досить трудомісткий процес, в зв'язку з цим, центри обробки даних Microsoft зіткнулися з труднощами при використанні GPU в якості єдиного обчислювального кошти, т. К. Оскільки вони мали обмежену придатність і велике енергоспоживання. У 2014 році була протестована FPGA Altera Stratix 5 для обробки алгоритмів ранжирування пошуку. Результати показали збільшення продуктивності майже в 2 рази, в зв'язку з цим було прийнято рішення використовувати дану архітектуру для тестування прискорювача CNN.

Прискорювач на основі програмованих логічних інтегральних схем (ПЛІС) FPGA був розроблений для ефективного розрахунку прямого поширення згортальних шарів. Таким чином, прискорювач CNN повинен мати можливість приймати вхідне зображення і обробляти кілька згортальних шарів поспіль. При розробці архітектура повинна включати кілька факторів. Оскільки система повинна обробляти кілька рівнів, обчислювальний движок системи повинен бути налаштований для підтримки цих верств. Управління пам'яттю має вирішальне значення, тому проект повинен включати ефективну схему буферизації даних і мережа повторного поширення на кристалі. Нарешті, архітектура проекту повинна мати можливість утримувати просторово розподілений масив елементів обробки, які можна легко масштабувати до тисяч одиниць. Це дозволяє прискорювача CNN прийняти вхідне зображення, а потім виконати аналіз численних згортальних шарів поспіль. Метод, в якому система обробляє згорткові шари, сильно залежить від використовуваного обладнання. ПЛІС FPGA стали явним вибором для досягнення більшої ефективності обробки [6].

При розгляді окремих випадків продуктивність окремих FPGA нижче продуктивності GPU.Для роботи з CNN були використані Altera Arria 10. Даний FPGA крмплекс дозволяє обробляти 233 зображення в секунду при споживаної потужності близько 25 Вт. Для порівняння, графічний процесор NVIDIA Tesla K40 може обробляти від 500 до 824 зображень в секунду, при споживаної потужності 235 Вт для обробки зображень з такою швидкістю. Окремі FPGA показують меншу швидкість істотно меншому споживанні енергії. Однак основною перевагою FPGA є масштабованість. Як мінімум три FPGA можуть бути пов'язані один з одним, щоб забезпечити таку ж потужність обробки, що і Tesla K40, при одночасному зниженні вихідної потужності приблизно на 30%.

FPGA Arria 10 забезпечує до 40 GFLOPS на ват. Arria 10 використовує OpenCL, разнвідность VHDL, для кодування своїх блоків обробки цифрового сигналу з плаваючою точкою IEEE754. Arria 10 має гнучкий шлях передачі даних, який обходить зовнішню пам'ять і дозволяє ядер OpenCL передавати дані безпосередньо один одному. На додаток до гнучкого шляху даних, Arria 10 підтримує апаратні операції з фіксованою плаваючою точкою, як для множення, так і для складання. Це дозволяє FPGA містити більше логіки і забезпечувати більш високу тактову частоту. Завдяки цим поліпшень у функціональності апаратного і програмного забезпечення, Arria 10 здатна перевершити існуючі платформи на основі графічних процесорів [7].

У тестах, виконаних Microsoft з використанням масиву Arria 10s для обчислення функцій CNN, команда спостерігала приблизно 30-кратний приріст продуктивності.

З поліпшенням продуктивності ПЛІС FPGA центри обробки даних можуть використовувати і їх для задоволення потреб в обчислювальних можливостях і енергоспоживанні. Це дозволяє емулювати глибоке навчання шляхом послідовної обробки декількох шарів згортальних нейронних мереж.

5. Огляд засобів розробки

Xilinx ISE (Integrated Synthesis Environment) - програмне забезпечення, створене фірмою Xilinx для синтезу та аналізу конструкцій HDL, що дозволяє розробнику синтезувати (компілювати

) свої проекти, виконувати аналіз роботи в часі, аналізувати RTL-діаграми та імітувати реакцію модулі на різні сигнали [8].

Xilinx ISE - це середовище проектування для продуктів FPGA від Xilinx і тісно пов'язана з архітектурою таких чіпів і не може використовуватися з продуктами FPGA від інших постачальників. Xilinx ISE в основному використовується для синтезу і проектування схем, в той час як ISIM або логічний імітатор ModelSim використовуються для тестування на рівні системи. Інші компоненти, що поставляються з Xilinx ISE, включають Embedded Development Kit (EDK), комплект розробки програмного забезпечення SDK і ChipScope Pro.

Xilinx ISE рядом особливостей, головною з яких є можливість створення файлу прошивки для завантаження в FPGA-комплекс. Це і є головною особливістю даного середовища, так як вона дозволяє не тільки моделювати описані схеми і програми, але і тестувати їх в реальних умовах.

Для створення файлу прошивки необхідно пройти ряд кроків:

- перевірка синтаксису;

- синтез;

- імплементацію дизайну;

- створення файлу прошивки.

Імплементація також розбивається на кілька етапів, протягом яких, будується модель проекту на логічних елементах. У зв'язку з великою кількістю етапів створення файлу прошивки займає тривалий час, що є великим недоліком даного середовища.

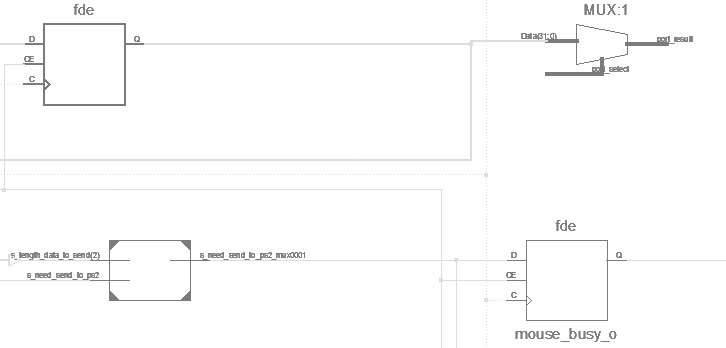

Після фази синтезу HDL процесу синтезу можливо відобразити схематичне уявлення синтезованого вихідного файлу (RTL-схема). На цій схемі показано виставу попередньо оптимізованої конструкції з використанням загальних елементів, таких як суматори, помножувачі, лічильники і логічні елементи І АБО. Перегляд цієї схеми може допомогти виявити проблеми дизайну на ранній стадії процесу проектування. Приклад семи представлений на рисунку 3.

Рисунок 3 — Приклад RTL-схеми

Ще до навантаження програми в FPGA-комплекс ISE знає кількість логічних елементів, а також складних структур, необхідних для побудови схеми, яка виконує написану програму. Ці дані видаються користувачеві у вигляді таблиці і дозволяють визначити, в який момент користувач перевищить наявний обсяг елементів.

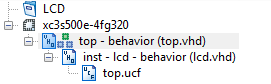

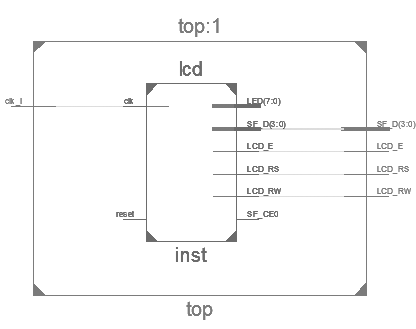

Також, на відміну від Active-HDL, в даному середовищі чіткіше простежується поняття ієрархії і спадкування у випадках використання одних модулів іншими. Це помітно як у файловому меню, так і при аналізі схеми. Приклад меню і схеми представлені на рисунку 4 і 5 відповідно.

Рисунок 4 — Файлове меню проекту

Рисунок 5 — Файлове меню проекту

На рисунках чітко видно, що якщо один елемент використовує інший, то він знаходиться на більш високому рівні в ієрархії, що вірно для всіх мов опису апаратури.

Дане середовище має низку недоліків, серед яких низька швидкість роботи, а на додаток до цього дана середовище не є цілісною, вона складається з пакету програм, що взаємодіють один з одним. У зв'язку з цим розміри даного програмного забезпечення також досить великі. Ще одним недоліком є той факт, що ISE не може самостійно відстежувати поведінку прошивки всередині плати. Для цього використовується окреме програмне забезпечення ChipScope Pro [9]. Але, незважаючи на ряд недоліків, середа широко використовується для роботи з FPGA.

Висновки

В результаті науково-дослідної роботи були зібрані і вивчені матеріали з питань, пов'язаних з темою магістерської роботи.

У дослідженні були проаналізовані аналоги систем розпізнавання звуків на базі нейронних систем, можливість реалізації нейронних мереж FPGA, а також середовище розробки, спеціалізована в області роботи з FPGA.

Завдяки вивченим матеріалами можна зробити висновок, що існує мала кількість фахових програм для розпізнавання джерела звуку. Також дослідження показало, що реалізація нейронних мереж на базі FPGA є оптимальним рішенням при вирішенні локальних задач.

Перелік посилань

- Введение в архитектуры нейронных сетей [Электронный ресурс]. — Режим доступа: https://habr.com/company/oleg-bunin/blog/340184/. — Заглавие с экрана. — (Дата обращения: 05.12.2018).

- Nurvitadhi E. et al. Accelerating recurrent neural networks in analytics servers: Comparison of FPGA, CPU, GPU, and ASIC // Field Programmable Logic and Applications (FPL), 2016 26th International Conference on. — IEEE, 2016. — P. 1–4.

- Азаров А. Б. Обзор существующей концепции и возможностей реализации нейронных сетей / А. Б. Азаров, В. С. Константинов, Ю. Е. Зинченко, Т. А. Зинченко // Материалы студенческой секции IX Международной научно-технической конференции «Информатика, управляющие системы, математическое и компьютерное моделирование» (ИУСМКМ-2018). — Донецк: ДонНТУ, 2018. — С. 390-394.

- Дедегкаев Альберт Гагеевич, Рыжков Александр Александрович Метод проектирования структуры нейронных сетей на основе клеточных автоматов // Universum: технические науки. 2013. №1. URL: https://cyberleninka.ru/article/n/metod-proektirovaniya-struktury-neyronnyh-setey-na-osnove-kletochnyh-avtomatov (дата обращения: 23.12.2018).

- Машинный слух. Нейросеть SoundNet обучили распознавать объекты по звуку [Электронный ресурс]. — Режим доступа: https://habr.com/post/399659/. — Заглавие с экрана. — (Дата обращения: 05.12.2018).

- Использование ПЛИС FPGA в создании нейронных сетей [Электронный ресурс]. — Режим доступа: http://digitrode.ru/computing-devices/fpga/1045-ispolzovanie-plis-fpga-v-sozdanii-neyronnyh-setey.html. — Заглавие с экрана. — (Дата обращения: 05.12.2018).

- Intel PAC c FPGA Stratix 10 SX — ускоритель для больших задач [Электронный ресурс]. — Режим доступа: https://habr.com/company/intel/blog/425187/. — Заглавие с экрана. — (Дата обращения: 05.12.2018).

- Xilinx ISE [Электронный ресурс]. — Режим доступа: http://we.easyelectronics.ru/plis/osvaivaem-xilinx-ise.html. — Заглавие с экрана. — (Дата обращения: 05.12.2018).

- ChipScope Pro and the Serial I/O Toolkit [Электронный ресурс]. — Режим доступа: https://www.xilinx.com/products/design-tools/chipscopepro.html. — Заглавие с экрана. — (Дата обращения: 05.12.2018).

- Нейронные сети,

вредные

советы [Электронный ресурс]. — Режим доступа: https://habr.com/post/211610/. — Заглавие с экрана. — (Дата обращения: 05.12.2018).