Abstract

Content

- Introduction

- 1. Theme urgency

- 2. Goal and tasks of the research

- 3. Review of research and development

- 3.1 Review of international sources

- 3.2 Review of local sources

- 4. CAD Analysis Vilado by Xilinx

- 5. Using TMO for the organization of logical inference

- 6. Task setting and description of the developed add-in

- Conclusion

- References

Introduction

Today, FPGA design is one of the fastest growing subject areas. This is due to the fact that the number of different gadgets, for which chips are needed, only grows, and every year it is only stronger. The need to provide the market with the necessary volume of products forces engineers to reduce the time of manufacture of the final product, and, as a result, automate the design process.

The effectiveness of design processes in any subject areas is largely determined by the availability and degree of development of tools that allow the designer to formalize and reuse expert techniques for designing certain products. Design techniques are designed to significantly simplify designer solution of the design problem, based on the requirements of the technical specifications for the product (TK). Such tools allow you to create design techniques, save them, edit, and - apply as needed. The effect in this case is to reduce the time and complexity of the process of making design decisions.

1. Theme urgency

When designing FPGAs, engineers use the most advanced software systems that take on such cost-consuming operations as circuit tracing, time analysis, checking for inconsistencies and errors, etc. But to work with any of the packages that now exist on the market, the designer must still have a high level of domain knowledge. In addition, for leading companies in the field of computer engineering design (and not only for them) there is a problem: How to preserve the knowledge and experience of employees?

And, moreover: How to extract practical benefits from this?

.

In this regard, the following task arises: the creation of a knowledge base of FPGA design. The knowledge base, at the moment, is the most modern and technological solution in the field of data storage. It will allow not only to preserve the experience gained by years of employees, but also be able to apply it to the synthesis of new products [1].

2. Goal and tasks of the research

The purpose of the study of this work is:

- Analyze existing CAD FPGA and identify their main positive qualities;

- Analyze existing approaches to create logical inference machines;

- Choose the best approach to implement the knowledge base and justify the decision.

- Describe the structure of the software being developed.

The object of study of this work is the practical implementation of the knowledge base in the form of add-on CAD CEA.

3. Review of research and development

3.1 Review of international sources

AT work Automated sports rim design in CAD system

M.S. Abdul Karim и Ahmad Zulhakim Ab Rashid [2]

explore cosiness ways to create automation at the design stage to reduce the design time within the computer-aided design (CAD) package. It became clear that one of the most effective ways to implement automation in design is to automate the repetitive steps that must be performed each time a part is created. This project was aimed at developing a way to automate repetitive steps, and a case study was conducted on the design of the wheel rim.

AT work A Methodology of Knowledge Management Based on Ontology in Collaborative Design

Junming Hou, Chong Su, Yingying Su, Wanshan Wang [3] proposed methodology of knowledge management in the joint design, introduces the concept of collaborative design and knowledge management, as well as introduced the expression of knowledge based on ontology.

3.2 Overview of local sources

Among the masters of DonNTU are the following publications.

In the master's work Oh.B. MalyavkaИсследование способов организации построения

инструментальной интеллектуальной оболочки для проектирования сложных объектов на

базе экспертных методик

[5] promoted analysis of existing tools Build oeniya CAD, improvements to existing algorithms. An assessment of their efficiency was carried out and a toolkit was built with their help for automating the creation of problem-oriented CAD systems.

4. CAD Analysis Vivado by Xilinx

Vivado Design Suite — is a software package developed by Xilinx for the synthesis and analysis of HDL projects , replacing the Xilinx ISE with additional functions for developing systems on chips ( System on Chip , SoC ) and high level synthesis ( High - Level) Synthesis ) . Unlike ISE, which was used for modeling ModelSim , Vivado System Edition includes an integrated logic simulator [7].

Vivado allows developers to synthesize projects, perform time analysis, study RTL diagrams, simulate the project's response to various influences and customize the target device with the help of a programmer. Vivado is an Xilinx FPGA product development environment, closely related to the architecture of such chips, and cannot be used with other manufacturers' FPGA products.

The composition of Vivado The following components are included:

- Vivado compiler High-Level Synthesis allows you to describe C, C ++ and SystemC schemas for Xilinx devices without the need to create an RTL manually. Vivado HLS is widely considered to increase developer productivity, and it is confirmed that it supports C ++ classes , templates, functions, and operator overloading. In Vivado 2014.1 adds support for automatic conversion OpenCL kernels in the IP for Xilinx devices. OpenCL cores are programs that run on different platforms CPU, GPU and FPGA.

- Vivado Simulator — compiled language simulator that supports mixed languages, TCL scripts, encrypted IP, and advanced validation.

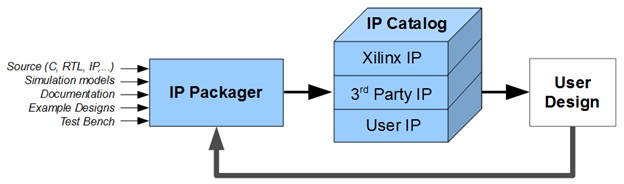

- Vivado IP Integrator allows engineers to quickly integrate and configure IP from the Xilinx large IP library . The integrator is also configured for MathWorks projects. Simulink, created using the Xilinx system generator and high-level Vivado synthesis .

- Vivado TCL Store — is a scripting system for developing add-ons for Vivado , and you can use it to add and modify Vivado features . TCL stands for Tool Command Language is the scripting language on which Viv ado itself is based . All basic Vivado functions can be called and controlled via TCL scripts.

Figure 1 — Simplified design route in Vivado HLS

(animation: 8 frames, delay 2s, 8 cycles of repeating, 39,8 KB)

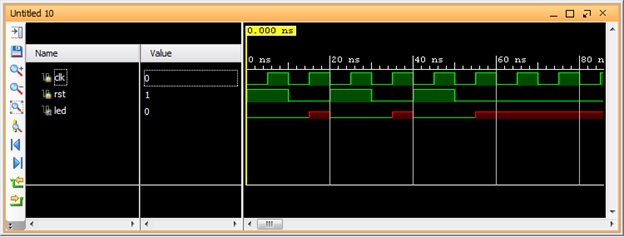

Figure 2 — Example of simulation in Vivado Similator

Figure 3 — Design process using Vivado IP Integrator

From the above, the following advantages and disadvantages of Vivado CAD software can be identified. Design Suite :

- Availability of powerful tools to automate the process of tracing, placement, temporary analysis of schemes.

- Availability of tools for high-level circuit synthesis in C , C ++ and System - C languages.

- The possibility of managing the entire development cycle using the script language Tcl.

- Ability to design circuits using various methodologies: RTL - descriptions, IP - cores, hardware description languages, high level synthesis.

Advantages:

- There is no possibility of specifying a design algorithm as a design technique for a certain class of devices with the subsequent re-use of this algorithm.

- Для работы с САПР Vivado Design Suite проектировщик должен обладать высоким уровнем знания предметной области.To work with Vivado CAD Design Suite the designer must have a high level of knowledge of the subject area.

Disadvantages:

5. Using TMO for the organization of logical inference.

The use of set-theoretic operations (TMO) for the organization of logical inference was described in detail in the works of A. Grigoryev. [10–12].

Briefly present the principle of operation of the logical inference engine based on TMT can be as follows :

- They are implemented (TMO) over the existing prototypes as a combination of structural components that have certain features;

- By lassification of a separate level, there is an AND-OR tree, where each node has a list of prototypes that have a given prize (input-output).

- The search for the required solution (prototype) is carried out through a dialogue, where each step involves the selection of a specific OR node followed by the continuation of the dialogue.

- After the selection step, the remaining prototypes are narrowed down, as well as the removal of those OR nodes, where the number of prototypes has reached 0.

6. Task setting and description of the add-in under development

As in all considered CADs there are such disadvantages as: 1) the inability to specify the design algorithm as a design technique for a certain class of devices with the subsequent re- use of this algorithm; 2) high requirements to the level of knowledge of the designer of the subject area; then there is a corresponding task: to create a software add-on over CAD FPGA for the possibility of creating a design algorithm for its reuse.

The developed software must meet the following requirements:

- The software add-on is created to summarize the user experience, which will later be used to create new products. Therefore, the existing component libraries should be fed into the system. It is assumed that they are already debugged and do not need to be checked.

- The add-in should simplify the design process by automating it.

- The system should reduce the requirements for the level of knowledge of the designer.

- The system should reduce the requirements for the level of knowledge of the designer.

- The logical conclusion of the program should be organized with the help of TMT. The choice in favor of this campaign was made for the following reasons:

- When using packages like Clips and Protege increases the requirements for the designer in the field of knowledge organization.

- In addition, there is a need to customize the software interaction between Clips / Protege and the superstructure above CAD.

- The approach with the use of TMT requires us to only program implementation of the approach itself.

- The system should implement the so-called

stupid expert

approach [13]. Astupid expert

— is a designer who lacks knowledge organization skills. In this case, the system itself undertakes all the work on the organization of knowledge (training, building a decision tree, the logical conclusion). - The system should be implemented as a superstructure over the Vivado CAD system. Design Suite , because it is the most advanced of all considered packages and one of the most popular among designers.

Conclusion

As a result of research work, materials were collected and studied on issues related to the theme of master's work.

The study analyzed the existing CAD REA, methods for creating logical inference machines, described the structure of the software being developed.

Automation of the design process is an important task , as it will significantly reduce the development time of the final product. In addition, today it is not fully implemented, and the one who makes it the first will have a significant advantage over competitors.

References

- Хвищук, А.Ю. Современные средства генерирования VHDL описаний аппаратуры при проектировании программируемых схем FPGA / Хвищук А.Ю., Григорьев А.В. // Микроелектроника и информатика — 2018. 25–я Всеросийская межвузовская научно–техническая конференция студентов и аспирантов: тезисы докладов. — М.:МИЭТ, 2018. — 316 с.

- Automated sports rim design in CAD system [Электронный ресурс] // IEEE Xplore Digital Library. — Режим доступа: https://ieeexplore.ieee.org/document/8376856/ — Загл. с экрана.

- A Methodology of Knowledge Management Based on Ontology in Collaborative Design [Электронный ресурс] // IEEE Xplore Digital Library. — Режим доступа: https://ieeexplore.ieee.org/document/4739796 — Загл. с экрана.

- Базы знаний интеллектуальных систем / Т.А. Гаврилова, В.Ф. Хорошевский — СПб: Питер, 2000. — 384 с.

- Исследование способов организации построения инструментальной интеллектуальной оболочки для проектирования сложных объектов на базе экспертных методик [Электронный ресурс] // Портал магистров ДонНТУ. — Режим доступа: http://masters.donntu.ru/2009/fvti/malyavka/diss/index.htm — Загл. с экрана.

- Процесс проектирования цифровых устройств с использованием ПЛИС [Электронный ресурс] // Электронная Образовательная Система МГТУ им. Н.Э.Баумана — Режим доступа: http://e-learning.bmstu.ru/moodle/pluginfile.php/2910/mod_resource/content/3/%D0%AD%D0%92%D0%9C_5.pdf — Загл. с экрана.

- Wikipedia contributors. (2018, December 26). Xilinx Vivado. In Wikipedia, The Free Encyclopedia. Retrieved 23:09, January 8, 2019, from https://en.wikipedia.org/w/index.php?title=Xilinx_Vivado&oldid=875403824 — Загл. с экрана.

- Wikipedia contributors. (2018, November 22). Intel Quartus Prime. In Wikipedia, The Free Encyclopedia. Retrieved 23:12, January 8, 2019, from https://en.wikipedia.org/w/index.php?title=Intel_Quartus_Prime&oldid=870064844 — Загл. с экрана.

- CLIPS [Электронный ресурс] : Материал из Википедии — свободной энциклопедии : Версия 95978215, сохранённая в 12:57 UTC 29 октября 2018 / Авторы Википедии // Википедия, свободная энциклопедия. — Электрон. дан. — Сан-Франциско: Фонд Викимедиа, 2018. — Режим доступа: https://ru.wikipedia.org/?oldid=95978215 — Загл. с экрана.

- Григорьев А.В. Методы поиска новых решений в специализированной инструментальной оболочке для создания интеллектуальных САПР // Десятая национальная конференция по искусственному интеллекту с международным участием КИИ–2006 (25–28 сентября 2006г., Обнинск): Труды конференции. — №. 3. — С. 1031–1046.

- Григорьев А.В. Теоретико–множественные операции над грамматиками как инструментарий для построения интеллектуальных САПР // XIII национальная конференция по искусственному интеллекту с международным участием КИИ–2012 (16–20 октября 2012 г., Белгород, Россия): Труды конференции. В 4–т., Белгород: Изд–во БГТУ, 2012, Т.3, с.202–209

- Григорьев А.В., Каспаров А.А. И/ИЛИ-ДЕРЕВО КАК СРЕДСТВО АБСТРАКТНОГО ПРЕДСТАВЛЕНИЯ БАЗЫ ЗНАНИЙ. — 2002.

- Григорьев А.В. Пути создания интеллектуальных САПР при различных уровнях квалификации экспертов //Донецк: ИПИИ МОН и НАН Украины

Наука и образование

. — 2005. — С. 758–763.

When writing this abstract the master's work is not completed yet. Final Completion: June 2019. The full text of the work and materials on the topic can be obtained from the author or his manager after the specified date.