Реферат за темою випускної роботи

Зміст

- Вступ

- 1. Актуальність теми

- 2. Мета і задачі дослідження та заплановані результати

- 3. Огляд досліджень та розробок

- 3.1 Огляд міжнародних джерел

- 3.2 Огляд національних джерел

- 3.3 Огляд локальних джерел

- 4. Процес проектування ПЛІС з використанням FPGA

- 5. Аналіз існуючих САПР

- 5.1 Vivado від Xilinx

- 5.2 Quartus—Prime від Altera Intel

- 5.3 Active–HDL від Aldec

- 6. Аналіз способів створення машин логічного висновку

- 6.1 CLIPS

- 6.2 Protege

- 6.3 Використання ТМО для організації логічного висновку

- Постановка завдання і опис розробляємої надбудови

- Висновки

- Перелік посилань

Вступ

На сьогоднішній день проектування ПЛІС є однією з найбільш швидко зростаючих предметних областей. Це обумовлено тим, що кількість різних гаджетів, для яких і потрібні чіпи, тільки росте, і з кожним роком тільки сильніше. Необхідність забезпечувати ринок за потрібне обсягом продукції змушує інженерів зменшувати час виготовлення кінцевого продукту, і, як наслідок цього, автоматизувати процес проектування.

Ефективність процесів проектування в будь—яких предметних областях багато в чому визначається наявністю і ступенем розвитку засобів, що дозволяють проектувальнику формалізувати і повторно використовувати експертні методики для проектування тих чи інших виробів. Методики проектування покликані істотно спростити проектувальнику рішення задачі проектування, виходячи з вимог технічного завдання на виріб (ТЗ). Такі інструментальні засоби дозволяють створювати методики проектування, зберігати їх, редагувати і—застосовувати в міру потреби. Ефект в цьому випадку полягає в скороченні часу і трудомісткості процесу прийняття проектних рішень.

1. Аактуальність

При проектуванні ПЛІС інженери використовують самі передові програмні комплекси, які беруть на себе такі трудомісткі операції як трасування схеми, часовий аналіз, перевірка на невідповідності і помилки і т.п. Але для роботи з будь—яким з пакетів, які зараз існують на ринку, проектувальник і раніше повинен мати високий рівень знань предметної області. Крім того, для провідних компаній в сфері проектування обчислювальної техніки (і не тільки для них) має місце проблема: «Як зберегти знання і досвід співробітників?» І, більш того: «Як отримати з цього практичну користь?»..

У зв'язку з цим виникає наступна задача: створення бази знань проектування ПЛІС. База знань, на даний момент, є найсучаснішим і технологічним рішенням в області зберігання даних. Вона дозволить не тільки зберегти накопичений роками досвід співробітників, але і зможе застосувати його для синтезу нових продуктів [1].

2. Мета і задачі дослідження та заплановані результати

Метою дослідження даної роботи є:

- Проаналізувати існуючі САПР FPGA і виявити їх основні позитивні якості;

- Проаналізувати існуючі підходи для створення машин логічного висновку;

- Вибрати кращий підхід для реалізації бази знань і обгрунтувати рішення.

- Описати структуру розроблюваного програмного продукту.

Об'єктом дослідження даної роботи є практична реалізація бази знань у вигляді надбудови над САПР РЕА.

3. Огляд досліджень та розробок

3.1 Огляд міжнародних джерел

В роботі Automated sports rim design in CAD system

M.S. Abdul Karim и Ahmad Zulhakim Ab Rashid [2]

дослідні затишок шляху створення автомат ізації на етапі проектування для скорочення часу на

проектування в рамках пакета автоматизованого проектування (САПР). Вияснілось, що одним з

найбільш ефективних спосо бов реалізації автоматизації в проектуванні є автоматизація повторюваних

кроків, які необхідно виконувати при кожному створенні деталі. Цей проект був націлений на розробку

способу автоматизації повторюваних кроків, і було проведено тематичне дослідження конструкції обода колеса.

В роботі A Methodology of Knowledge Management Based on Ontology in Collaborative Design

Junming Hou, Chong Su, Yingying Su, Wanshan Wang [3] запропонована

методологія управління знаннями в спільному дизайні, представляються концепції спільного проектування і

управління знаннями, а також вводиться вираз знань, засноване на онтології.

3.2 Огляд національних джерел

Книга Базы знаний интеллектуальных систем

Т.А. Гаврилової, В.Ф. Хорошевського [4] є учібником

для технічних вузів по вхідних в різні дисципліни питанням розробки інтелектуальних систем. Актуальність

предмета визначається зростаючим застосуванням інженерії знань і системного аналізу в р азлічних областях діяльності.

Особливістю викладу є його практична спрямованість: освоєння наявного матеріалу достатньо для початку самостійної роботи над створенням інтелектуальної системи, заснованої на знаннях.

У підручнику враховано все зростаюча роль Інтернету, і тому детально розглядається застосування інженерії знань в Мережі.

3.3 Огляд локальних джерел

Серед магістрів ДонНТУ можна виділити наступні публікації.

У магістерській роботі О.В. Малявки Исследование способов организации построения

инструментальной интеллектуальной оболочки для проектирования сложных объектов на

базе экспертных методик

[5] проведений аналіз існуючих інструментальних

засобів створення САПР, вдосконалені існуючі алгоритми. Здійснено оцен ка їх ефективності і побудований з їх допомогою інструментарій для автоматизації створення проблемно-орієнтованих САПР.

4. Процес проектування ПЛІС з використанням FPGA

Проектування цифрових устрій ств пр едставляет з себе ітераційний процес, заснований на принципах функціональної декомпозиції [6]. Проектування традиційно поділяють на етапи:

- системний,

- структурно-алгоритмічний,

- функціонально-логічний,

- конструкторсько-технологічний.

На системному етапівесь проект розбивається на частини, визначаються їх призначення і взаємозв'язок, приймається рішення про способи реалізації частин. Рішення про використання ПЛІС, прийняте на системному етапі, дозволяє виконувати конструкторсько-технологічне проектування модуля верхнього рівня паралельно з виконанням інших етапів.

Структурно-алгоритмічний і функціонально&ndashлогічний етапи проектування на ПЛІС являють собою ітераційний процес введення описів з подальшою їх верифікацією.

Сучасні САПР підтримують кілька способів опису пристрою:

- Опис з використанням мов опису апаратних засобів (VHDL, Verilog, AHDL та інших) за допомогою специализир ованного текстового редактора.

- Схемотехнічний спосіб за допомогою програми візуального проектування, в якій розробник поміщає на робочу область функціональні блоки і виробляє їх з'єднання. Після закінчення візуального проектування схема прео Бразил в мовне опис.

- Графічне представлення цифрових автоматів в спеціалізованому редакторі, що забезпечує перетворення отриманого графічного перед дання в мовне опис.

- Опис комбінаційної логіки за допомогою таблиць істинності, карт Карно, функцій алгебри логіки.

Конструкторсько-технологічний етап проектування з використанням ПЛІС розділяється на пов'язані підзадачі:

- Синтез (Synthesis).

- Глобальне розміщення (Mapping)

- Локальне розміщення (Placement).

- Трасування (Routing).

Синтез (Synthesis) — відображення схеми в базис логічних ресурсів ПЛІС. Мета синтезу—перетворення вихідного схемотехнического або високорівневого опису пристрою в опис, оптимально реалізується на обраної ПЛІС, а також придатне для подальшого розміщення і трасування.

Глобальне розміщення (Mapping) — призначення частин схеми макрообластей ПЛІС, що представляють собою групи сусідніх логічних блоків, макроячеек і блоків введення / виводу. Мета глобального розміщення: створення найкращих умов для локального розміщення і трасування. Для досягнення цього використовується інформація про призначення сигналів зовнішніх висновків, великою мірою впливає на призначення вільних областей ПЛІС частинах схеми. Як правило, призначення логічних ресурсів кристала макрообластям виробляють з надмірністю, що полегшує подальшу трасування.

Локальне розміщення (Placement) — детальне призначення логічних ресурсів макрообластей, обраних на стадії глобального розміщення, частинам схеми. При цьому переслідуються мети: рівномірне заповнення макрообластей елементами і трасами, мінімізація сумарної довжини ліній зв'язку та інші. Основна мета локального розміщення—створення найкращих умов для трасування.

Трасування (Routing) — визначення зв'язків між логічними блоками, макроячейками і блоками вводу-виводу у вигляді комутованих ділянок трас. На даній стадії переслідуються мети: вибору трас, що забезпечують заданий час поширення сигналу; мінімізації сумарної кількості програмованих точок зв'язку; мінімізація часу поширення сигналу по найдовшій лінії зв'язку. Важливим завданням стадії трасування є визначення часових параметрів отриманого варіанту пристрою і порівняння їх із заданими обмеженнями.

Процес проектування є ітераційним. Після виконання кожної стадії проводиться верифікація отриманого опису, для чого застосовуються різні засоби моделювання та аналізу. У сучасних САПР зазвичай передбачається моделювання на наступних етапах:

- Моделювання поведінкового опису.

- Моделювання опису на мові реєстрових передач.

- Моделювання технологічне кого опису (після синтезу).

- Моделювання на вентильному рівні.

- Моделювання після розміщення.

- Моделювання після трасування.

5. Аналіз існуючих САПР

5.1 Vivado від Xilinx

Vivado Design Suite — це програмний пакет, розроблений Xilinx для синтезу та аналізу HDL проектів, який замінює Xilinx ISE додатковими функціями для розробки систем на чіпах (System on Chip, SoC) і високий оуровневого синтезу (High—Level Synthesis). На відміну від ISE, який використовував для моделювання ModelSim, Vivado System Edition включає вбудований логічний симулятор [7].

Vivado дозволяє розробникам синтезувати проекти, виконувати часовий аналіз, вивчати RTL-діаграми, моделювати реакцію проекту на різноманітні впливи і налаштовувати цільовий пристрій за допомогою програміста. Vivado—це середовище розробки продуктів FPGA від Xilinx, тісно пов'язана з архітектурою таких чіпів, і її не можна використовувати з продуктами FPGA інших виробників.

До складу Vivado входять наступні компоненти:

- Компілятор Vivado High-Level Synthesis дозволяє описувати схеми на C, C ++ і SystemC для пристроїв Xilinx без необхідності створювати RTL вручну. Vivado HLS широко розглядається для підвищення продуктивності праці розробників, і підтверджений про, що він підтримує класи C ++, шаблони, функції і перевантаження операторів. У Vivado 2014.1 з'явилася підтримка автоматичного перетворення ядер OpenCL в IP для пристроїв Xilinx. Ядра OpenCL—це програми, які виконуються на різних платформах CPU, GPU і FPGA.

- Vivado Simulator — симулятор скомпільованої мови, який підтримує змішані мови, сценарії TCL, зашифрований IP і розширену перевірку.

- Vivado IP Integrator дозволяє інженерам швидко інтегрувати і налаштовувати IP з великою IP-бібліотеки Xilinx. Інтегратор також налаштований для проектів MathWorks Simulink, створених за допомогою системного генератора Xilinx і високорівневого синтезу Vivado.

- Vivado TCL Store — це система сценаріїв для розробки доповнень до Vivado, і її можна використовувати для додавання і зміни можливостей Vivado. TCL розшифровується як Tool Command Language і є мовою сценаріїв, на якому заснований сам Viv ado. Всі базові функції Vivado можуть викликатися і управлятися через сценарії TCL.

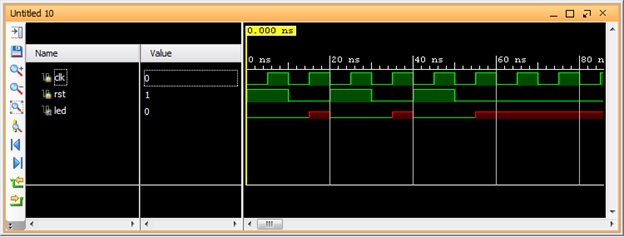

Рисунок 1 — Спрощений маршрут проектування в Vivado HLS.

(анімация: 8 кадрів, затримка 2 с, 8 циклів повторення, 39,8 КБ)

Рисунок 2 — Приклад симуляції в Vivado Similator.

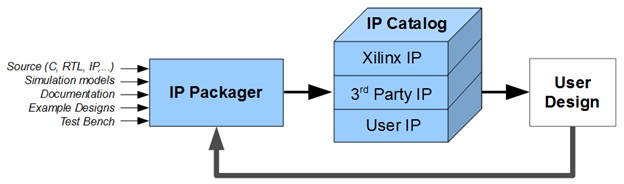

Рисунок 3 — Процес проектування з використанням Vivado IP Integrator.

З усього вищесказаного можна виділити наступні переваги і недоліки САПР Vivado Design Suite:

- Наявність потужних інструментів для автоматизації процесу трасування, розміщення, тимчасового аналізу схем.

- Наявність інструментів для високорівневого синтезу схем на мовах С, С ++ і System—C.

- Можливість управління всім циклом розробки за допомогою скриптового мови Tcl.

- Можливість проектування схем за допомогою різних методологій: RTL—описів, IP—ядер, мов опису апаратури, синтезу високого рівня.

Переваги:

- Немає можливості завдання алгоритму проектування як методики проектування певного класу пристроїв з подальшим повторним використанням цього алгоритму.

- Для роботи з САПР Vivado Design Suite проектувальник повинен мати високий рівень знання предметної області.

Недоліки:

5.2 Quartus-Prime від Altera Intel

Intel Quartus–Prime — це програмне забезпечення для проектування програмованих логічних пристроїв, розроблене Intel; до придбання Intel Altera інструмент називався Altera Quartus II. Quartus Prime дозволяє аналізувати і синтезувати проекти HDL, що дозволяє розробнику скомпілювати проекти, виконати часовий аналіз, вивчити RTL—діаграми, змоделювати реакцію проекту на різноманітні впливи і налаштувати цільове пристрій за допомогою програміста. Quartus Prime включає в себе реалізацію VHDL і Verilog для опису апаратного забезпечення, візуального редагування логічних схем і моделювання векторних сигналів [8].

Quartus–Prime включає в себе такі программні функції

- SOPC Builder, інструмент, який усуває завдання ручної системної інтеграції, автоматично генеруючи логіку межсоединений і створюючи тестову середу для перевірки функціональності.

- Qsys, інструмент системної інтеграції, який є наступним поколінням SOPC Builder. Він використовує оптимізовану FPGA архітектуру мережі на кристалі, яка подвоює продуктивність fMAX в порівнянні з SOPC Builder.

- SoCEDS, набір інструментів розробки, службових програм, програм в реальному часі і прикладів додатків, що допомагають розробляти програмне забезпечення для вбудованих систем SoC FPGA.

- DSP Builder, інструмент, який створює плавний міст між інструментом MATLAB / Simulink і програмним забезпеченням Quartus Prime, тому раз работчікі FPGA мають можливість розробки, моделювання та перевірки алгоритмів інструментів проектування на системному рівні MATLAB / Simulink.

- Інструментарій інтерфейсу зовнішньої пам'яті, який визначає проблеми калібрування і вимірює поля для кожного сигналу DQS.

- Створення файлів JAM / STAPL для програмістів внутрісхемних пристроїв JTAG.

- Також підтримує скріптові сценарії на мові Tcl.

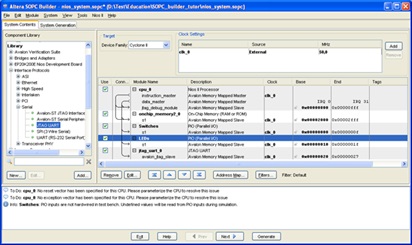

SOPC Builder

SOPC Builder (система на програмованому чіп билдері) — це програмне забезпечення, розроблене Intel, яке автоматизує підключення програмно-апаратних компонентів для створення повноцінної комп'ютерної системи, що працює на будь-якому з її різних чіпів FPGA. SOPC Builder включає в себе бібліотеку готових компонентів (включаючи флагманський програмний процесор Nios II, контролери пам'яті, інтерфейси і периферійні пристрої) і інтерфейс для включення користувальницьких компонентів. З'єднання осуще ствляют через шину Avalon. Арбітраж шини, узгодження ширини шини і навіть перетин годинного домену обробляються автоматично, коли SOPC Builder генерує систему. GUI—це єдина річ, яка використовується для налаштування програмно-апаратних компонентів (які часто мають багато опцій) і для вказівки топології шини.

Рисунок 4 — Зовнішній вигляд вікна SOPC Builder.

Отримана «віртуальна» система може бути потім підключена до зовнішнього світу через програмовані контакти FPGA або підключена всередині до інших програмним компонентам. Контакти FPGA направляються на роз'єми, такі як PCI або DDR, або, як це часто буває у вбудованих системах, на інші чіпи, встановлені на тій же платі.

Використання ресурсів на FPGA, на якій розміщена система SOPC Builder, дуже скромно за сучасними стандартами. Пристрої FPGA, що підтримують системи SOPC, включають майже всі FPG A Intel (і навіть деякі CPLD).

САПР Quartus—Prime дуже схожий на Vivado Design Suite, за невеликим винятком, тому і їхні переваги й недоліки подібні:

- У Quartus—Prime також є засоби автоматизації процесу трасування, розміщення, тимчасового аналізу схем.

- Є можливість створювати сценарії на мові Tcl для управління процесом розробки.

- Quartus—Prime може взаємодіяти з MATLAB / Simulink для створення і моделювання роботи схеми.

- Проектувальник має можливість використовувати різні методології при розробці схеми: RTL—опис, IP—отрута р а, мови опису апаратури.

Переваги:

- Відсутні інструменти для створення схем з допомогою високорівневого синтезу на мовах C, C ++.

- Немає можливості завдання алгоритму проектування як методики проектування певного класу пристроїв з подальшим повторним використанням цього алгоритму.

- Для роботи з САПР Quartus—Prime проектувальник повинен мати високий рівень знання предметної області.

Недоліки:

5.3 Active-HDL від Aldec

Active -HDL—середовище розробки ПЛІС, побудована на загальному ядрі симулятора HDL. Підтримує інструменти введення і налагодження текстового і графічного дизайну, забезпечує симуляцію на різних мовах (VHDL / Verilog / EDIF / SystemC / SystemVerilog) і надає уніфікований інтерфейс для різних інструментів синтезу і реалізації. Також підтримує перевірку на основі тверджень за допомогою тверджень Open Vera, PSL або Systemverilog Assertion. Доступні спеціальні версії програмного забезпечення, які підтримують тільки одного постачальника ПЛІС, наприклад, Active -HDL Lattice Edition .

- Наявність таких інструментів як Language Assistant і IP Core Generator для синтезу VHDL і Verilog коду.

- Є інструменти для автоматизованої трасування, розміщення, тимчасового аналізу схем.

Переваги:

- Відсутні інструменти для створення схем з допомогою високорівневого синтезу на мовах C , C ++ .

- Немає можливості завдання алгоритму проектування як методики проектування певного класу пристроїв з подальшим повторним використанням цього алгоритму.

- Для роботи з САПР Active—HDL , як і з усіма попередніми, проектувальник повинен мати високий рівень знання предметної області.

Недоліки:

6. Аналіз способів створення машин логічного висновку.

6.1 CLIPS

CLIPS — програмне середовище для розробки експертних систем. Синтаксис і назва запропоновані Чарльзом Форг ( Charles Forgy ) в OPS ( Official Production System ). CLIPS є продукционной системою. Реалізація в Висновки використовує алгоритм Rete .

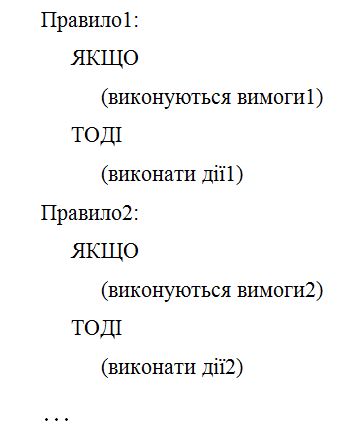

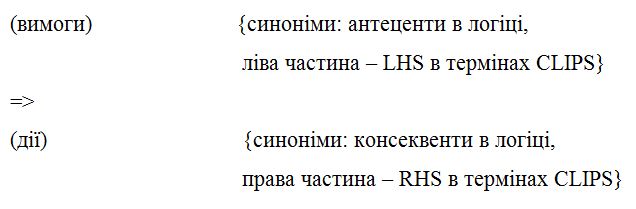

Основна ідея полягає в поданні знань у вигляді такої форми :

Рисунок 5 — Подання знань в Clips.

Таке уявлення близько до людського мислення і відрізняється від програм, написаних на традиційних алгоритмічних мовах, де дії впорядковані і виконуються строго дотримуючись алгоритму.

CLIPS є однією з найбільш широко використовуваних інструментальних середовищ для розробки експертних систем завдяки своїй швидкості, ефективності і безкоштовності. Будучи громадським надбанням, вона до цих пір оновлюється і підтримується своїм початковим автором, Гері Райлі ( Gary Riley ).

CLIPS включає повноцінний об'єктно-орієнтована мова COOL для написання експертних систем. Хоча вона написана на мові Сі, її інтерфейс набагато ближче до мови програмування LISP. Розширення можна створювати на мові Сі, крім того, можна інтегрувати CLIPS в програми на мові Сі [9].

CLIPS розроблений для застосування в якості мови прямого логічного висновку ( forward chaining ) і в своїй оригінальній версії не підтримує обратн ого виведення ( backward chaining ).

Як і інші експертні системи, CLIPS має справу з правилами та фактами.

Факти.

Інформація, на підставі якої експертна система робить логічний висновок, називається фактами. У CLIPS є 2 види фактів: впорядковані і шаблонні . Шаблонні факти мають шаблон, що задається конструкцією deftemplate . Впорядковані не мають явної конструкції deftemplate , проте вона мається на увазі. Шаблонний факт нагадує структуру в мові C або запис в мові Pascal , поля називаються слотами і оголошуються конструкцією slot .

Правила.

Знання предметної області представляються в CLIPS у вигляді правил, які мають наступну структуру:

Рисунок 6 — Правила в Clips.

Ліва частина правила—це умова його спрацьовування, а права частина—це ті дії, які повинні виконатися в разі виконання умов. Знак => спеціальний символ, що розділяє LHS і RHS. Правила оголошуються за допомогою команди defrule .

6.2 Protege

Protege — це вільний, відкритий редактор онтологій і фреймворк для побудови баз знань.

Платформа Protege підтримує два основних способи моделювання онтологій за допомогою редакторів Protege-Frames і Protege—OWL. Онтології, побудовані в Protege , можуть бути експортовані в безліч форматів, включаючи RDF (RDF Schema ), OWL і XML Schema .

Protege має відкриту, легко розширювану архітектуру за рахунок підтримки модулів розширення функціональності.

Prot?g? підтримується значним співтовариством, що складається з розробників і вчених, урядових і корпоративних користувачів, що використовують його для вирішення завдань, пов'язаних зі знаннями, в таких різноманітних галузях, як біомедицина, збір знань і корпоративне моделювання.

Редактор Protege–Frames

Редактор Protege—Frames дозволяє користувачам будувати і заповнювати онтології, засновані на фреймах, відповідно до OKBC ( Open Knowledge Base Connectivity protocol—прикладний інтерфейс програмування для доступу до баз знань систем уявлення знань). У цій моделі онтологія складається з набору класів, організованих в категоризовать ієрархію, для подання важливих понять області, набору слотів, пов'язаних з класами для опису їх властивостей і відносин між ними, і набору примірників цих класів—окремих екземплярів понять, які мають певні значення своїх властивостей.

Редактор Protege–OWL

Редактор Protege–OWL дозволяє користувачам будувати онтології для семантичної павутини, зокрема на OWL. OWL—онтологія може включати описи класів, властивостей і їх примірників. Даючи таку онтологію, формальна семантика OWL визначає як отримувати логічні слідства, тобто факти, які не присутні безпосередньо в онтології, але можуть бути виведені з існуючих за допомогою семантики. Ці висновки можуть бути засновані на одному документі або на безлічі розподілених документів, які були об'єднані з використаний ием певних механізмів OWL .

6.3 Використання ТМО для організації логічного висновку.

Використання Теоретико—множинних операцій (ТМО) для організації логічного висновку було детально описано в роботах Григор'єва О.В. [10–12].

Коротко представити принцип роботи машини логічного висновку, заснованої на ТМО можна наступним чином:

- Застосовуються (ТМО) над наявними прототипами як сукупностями структурних компонент, що мають ті чи інші ознаки;

- Классіфікація окремого рівня є І—АБО—дерево, де кожен вузол має список прототипів, що мають даний приз нак ( «вхід—вихід»).

- Пошук необхідного рішення (прототипу) виконується шляхом діалогу, де кожен крок передбачає вибір конкретного АБО—вузла з наступним продовженням діалогу.

- Після кроку вибору відбувається звуження залишилися в розгляді прототипів, а також видалення тих АБО—вузлів , де число прототипів дійшло до 0.

7. Постановка завдання та опис розробляємої надбудови

Так як у всіх розглянутих САПР є такі недоліки як: 1) відсутність можливості завдання алгоритму проектування як методики проектування певного класу пристроїв з подальшим повторним використанням цього алгоритму; 2) високі вимоги до рівня знання проектувальником предметної області; то виникає відповідна задача: створити програмну надбудову над САПР FPGA для можливості створення алгоритму проектування для його багаторазового використання.

Розроблюване ПЗ повинно відповідати наступним вимогам:

- Програмна надбудова створюється з метою узагальнення користувальницького досвіду, який в подальшому буде використаний для створення нових продуктів. Отже, на вхід системи повинні подаватися існуючі бібліотеки компонентів. Передбачається, що вони вже налагоджені і не потребують перевірки.

- Надбудова повинна спростити процес проектування шляхом його автоматизації.

- Система повинна знизити вимоги до рівня знань проектувальника.

- Процес роботи програмної надбудови полягає в тому, що вона за допомогою діалогу з користувачем дізнається потрібні йому структурні компоненти, і на підставі цієї інформації видає йому необхідну схему у вигляді VHDL коду або посилання на схему.

- Логічний висновок програми повинен бути організований за допомогою ТМО. Вибір на користь цього походу зроблений з наступних причин:

- При використанні таких пакетів як Clips і Protege підвищуються вимоги до проектувальника в області організації знань.

- Крім того, виникає необхідність настройки програмного взаємодії між Clips / Protege і надбудовою над САПР.

- Підхід із застосуванням ТМО вимагає від нас тільки програмної реалізації самого підходу.

- Система повинна реалізовувати так званий підхід

дурного експерта

[13].Дурний експерт

— це проектувальник, у якого відсутні навички в області організації знань. В такому випадку сама система бере на себе всю роботу по організації знань (навчання, побудова дерева рішень, логічний висновок). - Система повинна бути реалізована в якості надбудови над САПР Vivado Design Suite , оскільки він є найбільш просунутим з усіх розглянутих пакетів і одним з найбільш популярних серед проектувальників.

Висновки

В результаті науково—дослідної роботи були зібрані і вивчені матеріали з питань, пов'язаних з темою магістерської роботи.

У дослідженні були проаналізовані існуючі САПР РЕА, методи створення машин логічного висновку, описана структура розроблюваного програмного продукту.

Автоматизація процесу проектування є актуальним завданням , оскільки дозволить істотно скоротити час розробки кінцевого продукту. Крім того на сьогоднішній день вона повністю не реалізована, і той хто зробить це першим матиме суттєву перевагу над конкурентами.

Перелік посилань

- Хвищук, А.Ю. Современные средства генерирования VHDL описаний аппаратуры при проектировании программируемых схем FPGA / Хвищук А.Ю., Григорьев А.В. // Микроелектроника и информатика — 2018. 25–я Всеросийская межвузовская научно–техническая конференция студентов и аспирантов: тезисы докладов. — М.:МИЭТ, 2018. — 316 с.

- Automated sports rim design in CAD system Электронный ресурс] // IEEE Xplore Digital Library. — Режим доступа: https://ieeexplore.ieee.org/document/8376856/ — Загл. с екрану.

- A Methodology of Knowledge Management Based on Ontology in Collaborative Design Электронный ресурс] // IEEE Xplore Digital Library. — Режим доступа: https://ieeexplore.ieee.org/document/4739796 — Загл. с екрану.

- Базы знаний интеллектуальных систем / Т.А. Гаврилова, В.Ф. Хорошевский — СПб: Питер, 2000. — 384 с.

- Исследование способов организации построения инструментальной интеллектуальной оболочки для проектирования сложных объектов на базе экспертных методик Электронный ресурс] // Портал магистров ДонНТУ. — Режим доступа: http://masters.donntu.ru/2009/fvti/malyavka/diss/index.htm — Загл. с екрану.

- Процесс проектирования цифровых устройств с использованием ПЛИС Электронный ресурс] // Электронная Образовательная Система МГТУ им. Н.Э.Баумана — Режим доступа: http://e—learning.bmstu.ru/moodle/pluginfile.php/2910/mod_resource/content/3/%D0%AD%D0%92%D0%9C_5.pdf — Загл. с екрану.

- Wikipedia contributors. (2018, December 26). Xilinx Vivado. In Wikipedia, The Free Encyclopedia. Retrieved 23:09, January 8, 2019, from https://en.wikipedia.org/w/index.php?title=Xilinx_Vivado&oldid=875403824 — Загл. с екрану.

- Wikipedia contributors. (2018, November 22). Intel Quartus Prime. In Wikipedia, The Free Encyclopedia. Retrieved 23:12, January 8, 2019, from https://en.wikipedia.org/w/index.php?title=Intel_Quartus_Prime&oldid=870064844 — Загл. с екрану.

- CLIPS Электронный ресурс] : Материал из Википедии — свободной энциклопедии : Версия 95978215, сохранённая в 12:57 UTC 29 октября 2018 / Авторы Википедии // Википедия, свободная энциклопедия. — Электрон. дан. — Сан—Франциско: Фонд Викимедиа, 2018. — Режим доступа: https://ru.wikipedia.org/?oldid=95978215 — Загл. с екрану.

- Григорьев А.В. Методы поиска новых решений в специализированной инструментальной оболочке для создания интеллектуальных САПР // Десятая национальная конференция по искусственному интеллекту с международным участием КИИ–2006 (25–28 сентября 2006г., Обнинск): Труды конференции. — №. 3. — С. 1031–1046.

- Григорьев А.В. Теоретико–множественные операции над грамматиками как инструментарий для построения интеллектуальных САПР // XIII национальная конференция по искусственному интеллекту с международным участием КИИ–2012 (16–20 октября 2012 г., Белгород, Россия): Труды конференции. В 4–т., Белгород: Изд–во БГТУ, 2012, Т.3, с.202–209

- Григорьев А.В., Каспаров А.А. И/ИЛИ—ДЕРЕВО КАК СРЕДСТВО АБСТРАКТНОГО ПРЕДСТАВЛЕНИЯ БАЗЫ ЗНАНИЙ. — 2002.

- Григорьев А.В. Пути создания интеллектуальных САПР при различных уровнях квалификации экспертов //Донецк: ИПИИ МОН и НАН Украины

Наука и образование

. — 2005. — С. 758–763.

При написанні даного реферату магістерська робота ще не завершена. Остаточне завершення: червень 2019 року. Повний текст роботи та матеріали по темі можуть бути отримані у автора або його керівника після зазначеної дати.