Статистика поиска в интернет Электронная библиотека Биография Ссылки

|

Донецький національний технічний університет |

Останнім часом різноманітні дискретні пристрої знаходять застосування у практично

всіх сферах діяльності людини. У зв'язку з чим, при проектуванні пристроїв,

значну міру уваги приділяють їх надійності. Це пояснюється тим, що дуже часто

від правильної роботи пристроїв залежить здоров'я та життя людини.

Для забезпечення високої надійності необхідно застосовувати при проектуванні, виробництві та експлуатації пристроїв засобів технічної діагностики, які дозволяють здійснити контроль і локалізацію несправностей. Найбільш підходящими для цього є системи автоматичного проектування - САПР та нові методи діагностування апаратури. При застосуванні цих засобів можна швидко і точно виявити та усунути недоліки в пристроях на стадії їх проектування. В даний момент доступні такі САПР: Active-HDL, OrCAD, PCAD та інші. Active-HDL серед інших систем виділяється зручним інтерфейсом і широкими можливостями для створення дискретних пристроїв та їх моделювання. Також все більш завойовує популярність мова опису апаратних засобів VHDL. Вона дає розроблювачу апаратури широкі можливості для розробки цифрових пристроїв. До числа нових методів верифікації проектів апаратури належить HES-технологія, яка значно полегшує та прискорює процес розробки та перевірки нових проектів.

В даній роботі розробляється новий метод моделювання та аналізу константних

несправностей з використанням HES-технології.Мета роботи - розробити модель підсистеми моделювання та

аналізу константних несправностей, яка дозволить моделювати константні несправності комбінаційних

логічних схем.

1. ДІАГНОСТИКА ТА МОДЕЛЮВАННЯ АПАРАТУРИ З ВИКОРИСТАННЯМ HES-ТЕХНОЛОГІЇ

1.1. Загальні відомості про HES-технологію

При розробці складних проектів апаратури розробники зіштовхуються з проблемою

верифікації проекту. Тобто йдеться про

час, який витрачується на моделювання та перевірку в САПР. В процесі розробки

проекту, до нього кожного разу додаються нові модулі по мірі їх створення. При

цьому необхідно промоделювати ці модулі окремо один від одного, і потім, коли

вони будуть перевірені в програмно в САПР, їх можна під'єднати до інших модулів

в проекті. Після цього необхідно перевірити роботу проекту в цілому. Таким чином,

кожного разу, при під'єднанні нового модуля до проекту, стає необхідним моделювання

в кінцевому рахунку моделювання всього проекту в цілому, і з кожним кроком цей

процес стає все більш трудомістким та громіздким.

Для полегшення процесу розробки апаратури та збереження часу розроблювачів компанією

Aldеc Inc. була розроблена HES (Hardware Embedded Simulation)-технологія. HES

- це технологія, яка полегшує покрокову верифікацію FPGA та ASIC пристроїв.

Головною відмінністю HES-технології є те, що проект завантажується до FPGA на

платі і над ним виконується змішане апаратне та програмне моделювання. Плата

являє собою PCI-карту, котра вставляється до вільного слоту в комп'ютері. При

використанні HES-технології також є необхідним моделювання проекту в цілому.

Але кожна нова частина, яка вже була перевірена на програмному рівні, завантажується

до FPGA. Таким чином, програмний рівень відповідальний тільки за моделювання

нових модулів. Оскільки швидкість моделювання на платі не залежить від розміру

проекту, час моделювання ефективно зменшується.

Іншою важливою особливістю HES є те, що на її основі можна тестувати зовнішні

системи. Для цього на Можна під єднати зовнішню систему чи її частину подібно

процесору чи таймеру через дочірню плату до HES- плати. Також є можливим спільне

моделювання системи з її частиною чи іншою системою, яка підготовлена в програмному

середовищі, а потім, після завантаження її до HES- плати, моделювання взаємодії

систем в цілому на платі.

Розглянемо переваги та характеристики нового методу:

1.2. Розгляд структури HES-плати

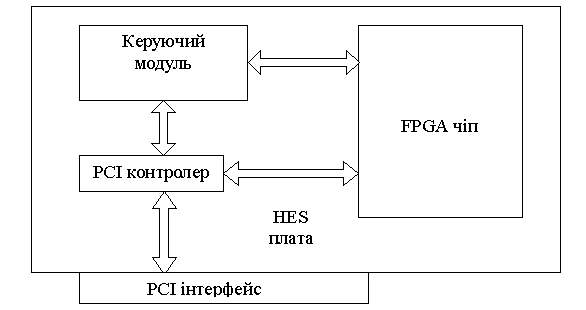

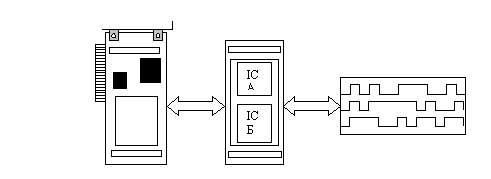

Структура HES- плати приведена на рис 1.1. Вона містить FPGA чіп, керуючий

модуль та PCI контролер. FPGA чіп - головна моделююча частина. Усі розроблені

модулі моделюються в цьому модулі. Для конфігурації FPGA використовується керуючий

модуль. Керуючий модуль виконує передачу даних між PCI контролером та FPGA чіпом.

До його обов'язків також входять внутрішні функції ідентифікації, контролю моделювання

та програмування FPGA. PCI контролер обслуговує передачу даних з/до шини PCI

до/з HES-плати.

Рис. 1.1 - Структура HES плати

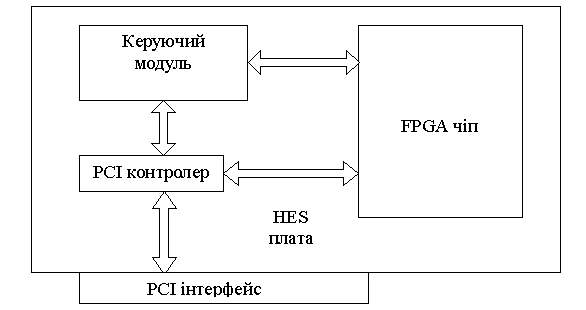

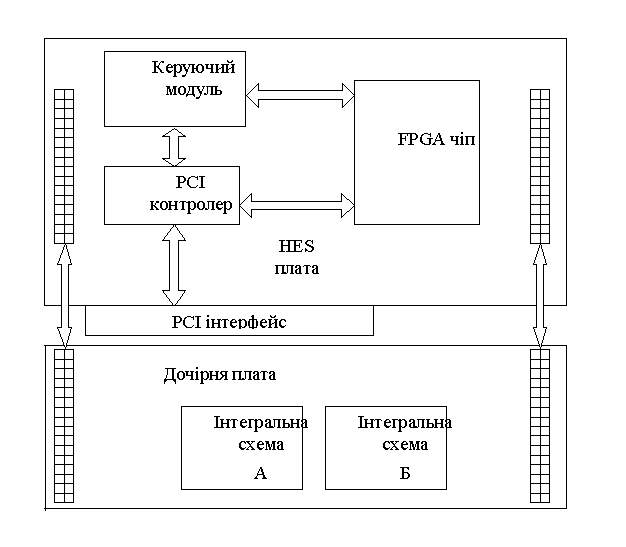

Структура, що приведена на рис.1.2, відображає зв'язки між HES-

платою та зовнішньою системою, яка базується на реальній схемі. Дочірня плата

являє собою інтерфейс по відношенню до HES- плати.

Рис. 1.2 - Структура HES- плати з можливістю під'єднання зовнішньої

схеми

1.3. Побудова системи моделювання на базі HES-технології

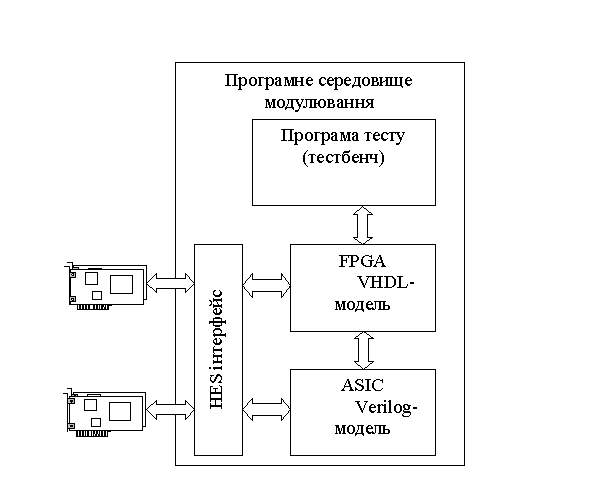

Увесь проект в цілому моделюється в HES оточенні, котре містить

програмне HDL середовище моделювання та PCI плати. Це оточення гарантує правильні

зв'язки між модулями, що знаходяться в платі та модулями, які моделюються на

програмному рівні. як видно зі структури на рис. 1.3, система моделювання підтримує

до чотирьох HES- плат та дозволяє розробнику використовувати HES- плати з різними

моделюючими середовищами.

Модулі, що завантажені до HES- плати, залишаються зв'язані з

програмним середовищем через PCI інтерфейс. Зв'язки між модулями на

Рис. 1.3 - Загальна структура системи моделювання на базі HES

програмному та на апаратному рівнях реалізовані в програмному середовищі.

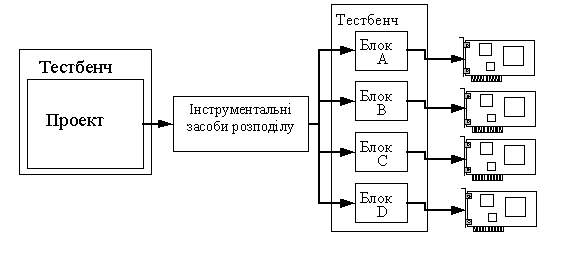

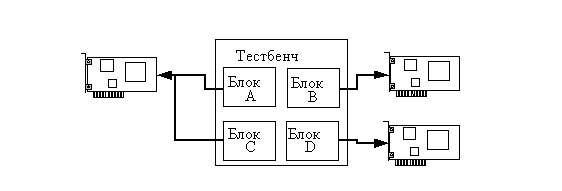

Розглянемо структури систем моделювання на базі HES-технології для конкретних

випадків. Для великих проектів є можливим виконання паралельного моделювання.

Тут існує два випадки. якщо це цільний проект, то для нього підійде структура

на рис. 1.4, з якого видно, що проект розподіляється на менші частини, котрі

завантажуються до різних HES-плат. якщо проект складається з окремих компонентів,

то для нього підійде структура на рис. 1.5, де кожний компонент може бути завантажений

до окремої плати, чи декілька компонентів до однієї плати.

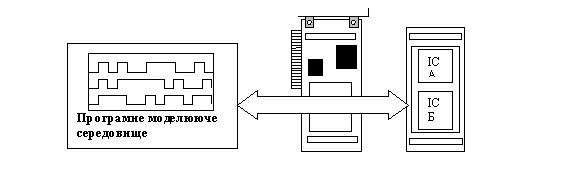

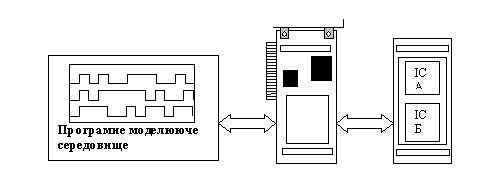

При використанні інтерфейсу дочірньої плати, можливості моделювання значно поширюються.

Можливі такі структури використання дочірньої плати. На рис. 1.6 відображена

структура, при якій HES- плата забезпечує зв'язок між інтегральними схемами

(ІС) на дочірній платі та моделюючим середовищем. В структурі на рис. 1.7 ІС

виступають в ролі частин проекту, котрий апаратно моделюється. Рис. 1.8 показує

випадок, при якому HES-плата працює в якості тестової платформи для ІС на дочірній

платі.

Рис. 1.4 - Варіант побудови системи моделювання для цільного

проекту

Рис. 1.5 - Варіант побудови системи моделювання для проекту, який

складається з компонентів

Рис. 1.6 - Структура забезпечення зв'язку HES-платою

Рис. 1.7 - Структура моделювання ІС як частини проекту

Рис. 1.8 - Структура використання HES- плати в якості тестової

платформи

2. ПОБУДОВА ДІАГНОСТИЧНОЇ МОДЕЛІ FPGA- ПРИСТРОЇВ НА БАЗІ Т-МОДЕЛІ З ВИКОРИСТАННяМ HES-ТЕХНОЛОГІЇ

2.1. Розробка структури підсистеми моделювання несправностей

В даному розділі розглядається альтернативний засіб отримання тестових наборів

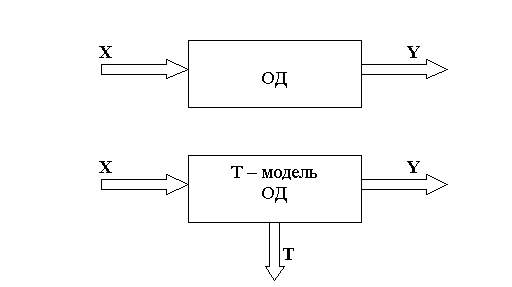

для логічних схем. Цей засіб базується на використанні Т-моделі об'єкту діагностики

(ОД). У загальному випадку ОД дискретного типу має безліч входів X, виходів

Y та безліч несправностей H. Його та його Т-модель можна представити такими

узагальненими структурами рис. 2.1:

Рис 2.1 - Узагальнена структура ОД та його Т-моделі

Особливістю Т-моделі є те, що при її розробці кожному логічному елементу вихідної

схеми ставиться у відповідність так званий Т-елемент. Припускається, що він,

окрім функцій які виконує базовий елемент, виконує функції, які необхідні для

побудови тестових наборів. Це функції спостерігання і тестування несправностей

схеми, зв'язаних з елементом схеми, що моделюється. Таким чином, Т вихід Т-моделі

об'єкту діагностики виражає умову виявлення несправності h вхідною тестовою

послідовністю на виходах Y.

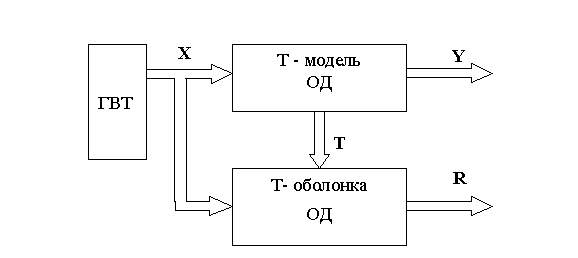

Для усієї логічної схеми будується діагностична оболонка, яка призначається

для вирішення конкретної діагностичної задачі. В процесі моделювання Т-моделі

та діагностичної оболонки одержуємо результати вихідних функцій логічної схеми

та діагностичні результати схеми, що тестується. Процес моделювання складається

з того, що на входи Т-моделі подаються різні тестові набори, а на її виходах

одержуємо список несправностей, які виявляються чи не виявляються в результаті

моделювання. З цього списку можна сформувати тест мінімальної довжини, який

буде покривати максимальну кількість несправностей схеми.

Таку підсистему моделювання несправностей (Т-модель та діагностична оболонка)

можна представити структурною схемою на

рис. 2.2:

Рис. 2.2 - Підсистема для вирішення діагностичних задач на базі Т-моделі

В такій підсистемі використовується генератор випадкових чи псевдовипадкових

тестів (ГВТ) для збудження функцій тестування по випадковому (псевдовипадковому)

закону. Під впливом тесту на виходах Т з'являється тестова реакція. якщо в деякий

момент часу на входах ОД генератор тестів виставляє тест несправності h, то

відповідний вихід тестування зводиться в логічну одиницю, в протилежному випадку

на цьому виході логічний нуль. Тестова реакція поступає на Т-оболонку, яка специфічна

для кожної задачі. Т-оболонка на своєму виході R виставляє результат вирішення

задачі.

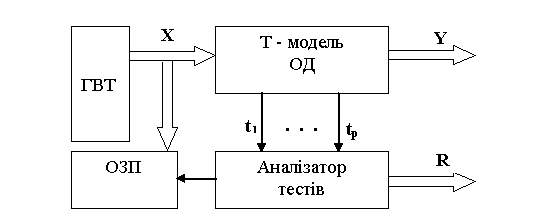

Розглянемо приклад задачі, яка може бути вирішена таким підходом. Синтез детермінованого

тесту для окремої константної несправності (КН) та ОД в цілому. Структура вирішення

такої задачі представлена на рис. 2.3.

Рис 2.3 - Структура вирішення задачі синтезу детермінованого тесту для

окремої КН та ОД в цілому

В структурі використовується ГВТ; Т-оболонка, яка представляє собою аналізатор

тестів, котрий виконує задачу виявлення тестових векторів та зберігання їх в

ОЗП тестів. При виявленні наступного тесту деякої КН аналізатор тестів визначає

також й ті КН, які тестуються спільно та "видаляються зі списку" невиявлених

несправностей. Моделювання виконується до "обнуління" вказаного списку

або до досягнення визначеної часової межі.

Для реалізації вищевикладеного засобу тестування для кожного логічного елементу

вхідної схеми розробляється відповідний T-елемент (тільки один раз, а після

цього він заноситься в бібліотеку). Вхідна схема замінюється на відповідну їй

схему, побудовану на T- елементах (так звану T-модель ОД). T-модель реалізується

в будь-якій САПР, що дозволить моделювати схему, не збираючи її насправді.

2.2. Розробка структури підсистеми моделювання на базі Т-моделі з використанням

HES-технології

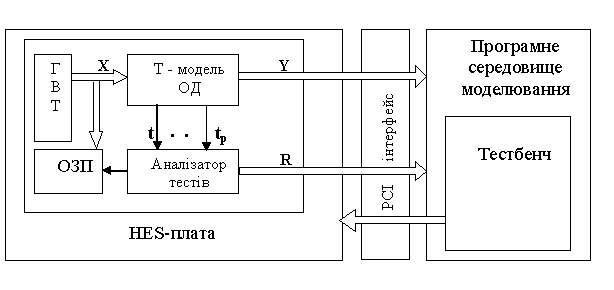

При використанні HES технології для побудови діагностичної моделі для FPGA-пристроїв можна піти двома шляхами, програмного чи апаратного моделювання. При використанні першого варіанту стає проблемою діагностика навіть середніх проектів, бо, як відомо, кількість вентилів діагностичної моделі пропорційна кубу кількості вентилів об'єкту діагностики. Тому час верифікації проекту може становити від декількох діб до неділь. Ця проблема зникає при використанні другого варіанту. При апаратному моделюванні час верифікації практично не залежить від розміру проекту, тому цей варіант є більш привабливим. Для використання апаратного моделювання при діагностиці FPGA пристроїв найбільш підходящою є HES-технологія, всі переваги якої були перелічені в другій главі. Загальна структура системи моделювання на базі Т-моделі ОД з використанням HES-плати приведена на рис. 2.4.

Рис. 2.4 - Загальна структура системи моделювання на базі

Т-моделі з використанням HES-плати.

як видно з рисунку тестова модель завантажується до HES-плати.

Результати моделювання передаються до програмного середовища моделювання. Процесом

моделювання керує тестбенч. Обмін між апаратним та програмним середовищем відбувається

через PCI інтерфейс.

Процес проектування системи моделювання та діагностики апаратури на базі Т-моделі

з використанням HES-технології буде включати наступні етапи: