Cвистунов С. Н.

IV международная конференция студентов, аспирантов и молодых учёных "Компьютерный мониторинг и информационные технологии", г. Донецк, 13-14 мая, 2008

Данный доклад представляет цифровую функциональную тестирующую архитектуру, в которой временные диаграммы аппаратных средств системы тестирования работают с последовательностью событий, таких же как и в интегральных схемах (ИС) моделирования времени\логики.

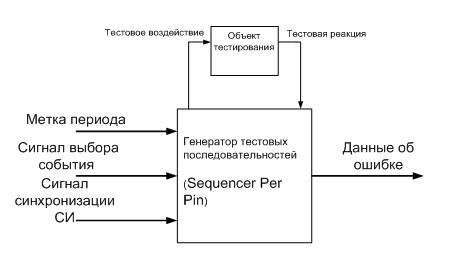

Поскольку постоянно усложняется структура и увеличивается количество выводов интегральных схем, то написание тестирующих программ для таких схем становится сложной задачей. Для упрощения этой задачи применяется тестирующая система с SPP(Sequencer Per Pin)-архитектурой. Данная архитектура представляет собой отдельных генератор тестовых последовательностей для каждого вывода интегральной схемы.

Генератор тестовых последовательностей программируется на основе тех данных, которые получены непосредственно в процессе симуляции тестируемого устройства. Далее эти данные, полученные с выходов симулятора, поступают на входы тестируемого устройства. И теперь нет необходимости ориентировать систему тестирования на архитектуру тестируемого цифрового устройства, так как все особенности архитектуры уже заложены в симулятор. Таким образом значительно упрощается процесс составления программ для тестирования цифровых устройств[1].

Генератор тестовых последовательностей содержит: локальную память с локальной адресацией, схему генерации временных событий, схему генерации сигналов стробирования, память последовательности временных событий, схему калибровки аппаратных средств, схему сравнения строба, схему хранения ошибок логики. Все генераторы работают независимо друг от друга.

Упрощенная структура тестирующей системы с SPP-архитектурой изображена на рис. 1.

Рисунок 1 – SPP-архитектура системы тестирования цифровых устройств

Генератор тестовых последовательностей получает метку периода и сигнал выбора события. Сигнал выбора события интерпретируется как 'тестовый вектор', аналогично тестовым системам других архитектур. Эти сигналы, вместе с сигналом синхронизации СИ, синхронизируют все входы. Временные диаграммы сгенерированные генератором тестовых последовательностей посылаются на вход ОД. Каждый генератор тестовых последовательностей так же получает данные выхода ОД для сравнения с заданными предельными величинами. Метка периода содержит время начального события, который синхронизируется по сигналу СИ, а также значение, которое сообщает генератору тестовых последовательностей, что определенная в пределах периода, последовательность событий должна начаться.

Архитектура генератора тестовых последовательностей упрощает программирование сложных временных диаграмм . Пользователь только должен определить тип события и время, в которое должно произойти событие. Форматы временных диаграмм, которые использовались в предыдущем поколении автоматических систем тестирования, легко генерируются использую концепцию последовательности событий.

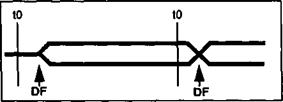

DF@1ns

Это выражение указывает аппаратным средствам переходить к данным текущего вектора каждую 1 нс (рис 2).

Рисунок 2 – Временная диаграмма запрограммированного события

На базе вышеописанной архитектуры разрабатывается блок контрольно-диагностической аппаратуры (КДА) в составе диагностического комплекса предназначенного для тестирования цифровых схем (пост контроля цифровых устройств).Применение технологии FPGA при разработке позволит реализовать пост с меньшими габаритами и материальными затратами.

На КДА возлагаются следующие функции:

- подача тестових векторов (ТВ) на внешние входы ОД;

- снятие и обработка тестовых реакций (ТР) с ОД;

- управление синхронизацией ОД;

- управление питанием ОД;

- обмен информацией с ЭВМ;

- сопряжение на физическом уровне ОД и ЭВМ.

Для работы с архитектурой генератора тестовых значений разрабатываются специальные программные инструменты. Прогрммное обеспечение будет направлено на упрошениепроцессов рассмотрения и изменения временных диаграмм тестовой программы делают простым. Временная диаграмма будет изображаться графически, тем самым позволяя пользователю изменить тестовую программу через графический интерфейс.

Литература

1. Sequencer Per Pin Test System Architecture,Burnell West and Tom Napier

Schlumberger Technologies -ATE Division 1601 Technology Dr. San Jose, CA

95110-1397

2. Соловьев В.В. Проектирование цифровых систем на основе программируемых

логических интегральных схем.- М.: Горячая линия – Телеком, 2001.- 636с.

3. Автоматизация диагностирования электронных устройств/ Ю.В. Малышко, В.П.

Чипулис, С.Г. Шаршунов. – М.: Энергоатомиздат, 1986. – 216 с.

|

Cвистунов Сергей Николаевич

Cвистунов Сергей Николаевич

Cвистунов Сергей Николаевич

Cвистунов Сергей Николаевич