Dovganich Egor

Computer Science Faculty

The Speciality of Computer Systems and Networks

The Theme of Masters Degree Work:

Research-and-development methods of FPGA diagnostics

Supervisor: Zinchenko Yuriy

Abstract

Introduction

Programmable logic integrated circuits have taken a stable position in the modern electronics world. That's why the question about unification methods of FPGA diagnostics has became a topical issue. However, became required methods of diagnostics, which could be applied to different types of logic circuits.

Topical issue

During the diagnostic can be identified some failure patterns, as a result of errors in the tehnological manufacturing process of FPGA, and errors made in the scheme in its design. To ensure that such situations can be traced and corrected, it is essential that faults should be detectable. The design can be inadvertently build such a combination scheme, not all of which point would be diagnostic in the future. It's necessary to avoid such situations.

The purpose and objectives of development and research

The main target of the master's work is modification of the method and software implementation critical path tracing method. This implementation involves commissioning original combination logic in the form of a text file in ISCAS-standard and results in the form of established test vector for the circuit, as well as the faults coverage percentage.

Scientific novelty

This method of FPGA diagnostics was proposed in 1990 by Mike Abramovich, but this method gave a low percentage of constant faults (CF) covering.[1] When the method has been modified, this percentage could be considered satisfactory, because it generated a test vector that is able to cover more than 80% detectiinf CF.

Practical innovation

A software implementation of the classic method of critical path tracing, and its modified version. The program can work with many cascade circuit, which has an arbitrary number of inputs.[3]

The practical significance of the results

With the success of all these tasks, the final product will be one of uniform FPGA diagnostic, which will help realize design, which can be diagnostic.

Conferences

A report on this theme appeared at the Fourth International Conference of students, graduate students and young scientists in the section "Design of computers and digital devices".

Review of research and development

Regional:

At the regional level, one of the few who learned this problem was Master of DonNTU Bobrovsky K. In his work, he thoroughly explored the question of the probe FPGA diagnostics through VHDL. This work is the closest to my Master's work.

1. Магистр ДонНТУ Бобровский Константин Викторович

Тема магистерской работы: "Разработка структуры поста контроля зондовой диагностики ТЭЗ на базе HDL- и FPGA-технологий", 2001г.

http://www.masters.donntu.ru/2006/fvti/bobrovskyy/diss/index.htm

National:

In reviewing the national-level the book of Butakov E. have found. It addresses the diagnosis of programmable logic array, which in fact is a major component of FPGA. This book was published in Moscow, but placed in the national level on linguistic criteria.

2. Бутаков Е.А. Диагностика программируемых логических матриц / Е.А. Бутаков, М.Б. Волынский, В.Г. Новоселов – М.: Радио и связь, 1991 – 160 с.

Global:

In the world dealing with this issue much more intensely. One of the first who began the study of diagnostic logic, was M. Abramovichi. He has a large number of articles and studies in this area.

The website IEEE Xplore contains many scientific papers, including in this subject. However, only summaries and conclusions of the articles are in the public domain, but the main content is only available to registered users.

3. Abramovici, M. Strond, C. Hamilton, C. Wijesuriya, S. Verma, V. Murray Hill, NJ

Using roving STARs for on-line testing and diagnosis of FPGAs infault-tolerant applications Test Conference, 1999.

http://ieeexplore.ieee.org/iel5/6540/17459/00805830.pdf?arnumber=805830

4. Stroud, C. Lashinsky, M. Nall, J. Emmert, J. Abramovici, M.

On-line BIST and diagnosis of FPGA interconnect using roving STARs, On-Line Testing Workshop, 2001.

http://ieeexplore.ieee.org/iel5/7458/20291/00937813.pdf?arnumber=937813

5. Stroud, C. Lee, E. Abramovici, M.

BIST-based diagnostics of FPGA logic blocks,

Test Conference, 1997.

http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=639662

6. Jack Smith, Tian Xia, Charles Stroud

An Automated BIST Architecture for Testing and Diagnosing FPGA Interconnect Faults, Journal of Electronic Testing, Theory and Applications 2006.

http://www.springerlink.com/index/FR805MQQ78876118.pdf

Main content

This method of critical paths tracing is a research method of combinational circuits, which help to build a test vector for the scheme. The test vector includes a set of tests, it means set of initial values of primary input patterns, which provide an opportunity to find the maximum number of detected CF.

Critical path method is an alternative to fault simulation, referred to as critical path tracing, that determines the faults detected by a set of tests using a backtracing algorithm starting at the primary outputs of a circuit.[1] Critical path tracing is an approximate method, but the approximations introduced occur seldom and do not affect its usefulness. This method is more efficient than conventional fault simulation.[1]

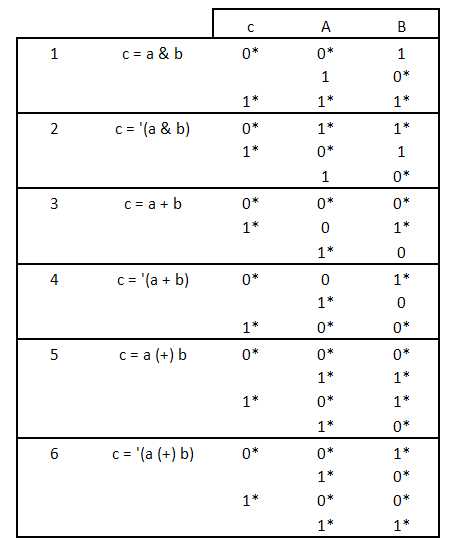

To determine the detected CF performed modeling correct scheme in which the calculated values for the critical signal paths. This calculation is performed from the primary outputs to primary inputs. Construction of the critical paths based on the theory logic cubes. For this analysis, it is necessary to create 0- and 1-logic covers of the logic cubes (table 1).[5]

Table 1. Logic covers of the cubes.

Using this method we construct a test circuit and identifies the line, whose values affect the values of primary outputs. Constant failure on the lines show the test circuit at the inputs (Fig. 1).

Figure 1. Practical using of the method (animation, 16 frames, 5 cycles, 88.4 Кbytes).

After the test vector would be completed, in the list will be all detected faults, therefore, we can conclude what faults remained undetected. To do this, from the set of all fault circuits (a single zero, and each line of the scheme, including the primary inputs and outputs (based on fault equivalence)) take a subset of the detected faults. Thus calculated completeness test, but the known and undiscovered faults, which can try to find by other methods of diagnostic.

This method of FPGA diagnostic is capable to reduce the simulation time and the diagnostic time of printed circuit boards, as well as in sharing with other methods gives a high rate of completeness of coverage and the CF does not require large hardware cost if practical implementation.

The master's work is not completed now.

Conclusions

The successful implementation of the critical paths tracing will be received by a software resource that can and should be applied in practice. There is currently no such software implementations of this method of diagnosis or at least, they are in closed access.

References

1. M. Abramovici, P.R. Menon and D.T. Miller. Critical path tracing - an alternative to fault simulation. - IEEE Design and test, Feb. 1984 - pp. 83-92.

2. M. Shadfar, A. Paymandoust, Z. Navabi. Using VHDL Critical Path Tracing Models for Pseudo Random Test Generation. - Electrical and Computer Engineering Department - pp. 8.

3. Барашко А.С., Скобцов Ю.А., Сперанский Д.В. Моделирование и тестирование дискретных устройств. – К., Наукова думка, 1992 - c. 28-32.

4. Бутаков Е.А. Диагностика программируемых логических матриц / Е.А. Бутаков, М.Б. Волын-ский, В.Г. Новоселов – М.: Радио и связь, 1991 – 160 с.

5. Новоселов В.Г. Синтез полных проверяющих тестов И–НЕ схем произвольной структуры на базе модели расширения и исчезновения интервалов / В.Г. Новоселов // Труды четвертой междунар. конф. «CADD’2001» сент. 2001, г. Минск — Минск: Ин-т техн. кибернетики НАН Беларуси, 2001 - c. 143-155.

6. Новоселов В.Г. Построение проверяющего теста для современных ПЛМ (CPLD) / В.Г. Новоселов, А.В. Борисевич // Вестник СевНТУ, вып. 74 — Севастополь: изд-во СевНТУ, 2006 — с. 47-57.

7. Беннетс Р. Проектирование тестопригодных логических схем. - Пер. с английского. - М.: Радио и связь, 1990 - 176 с.

8. Тарасенко А.Н. Методы оценки и показатели тестируемости дискретных устройств (обзор) //Зарубежная радиоэлектроника, 1989, выпуск 7 - с. 24-29.

9. Зинченко Ю.Е. T-модель дискретного устройства и решение диагностических задач на ее основе. - Электронная библиотека магистра Маркитанова В.Р. http://www.masters.donntu.ru/2001/fvti/markitantov/diss/library/zinchenko1/index.html, Портал магистров, 2001.

10. Уильямс Т.У., Паркер К.И. Проектирование контролепригодных устройств //ТИИЭР, 1983 - с. 122-139.