Библиотека

Тематическая статья №2

Об одном подходе к снижению трудоемкости на этапе проверки функционирования электронных устройств на ПЛИС

Дмитрий Зыкав, Владимир Ковригин

Журнал "Компоненты и технологии", 3й выпуск, 2004 г.

В настоящее время при разработке сложных цифровых изделий приобретают все большую популярность программируемые логические интегральные схемы (ПЛИС). На этапе производства цифровых электронных устройств на базе ПЛИС можно выделить два этапа контроля работоспособности продукции - входной контроль ПЛИС и функциональный контроль устройства в целом.

Входной контроль предназначен для тестирования ПЛИС на соответствие требованиям технических условий. Данный вид контроля, как правило, осуществляется на производственном участке по изготовлению цифровых электронных устройств (ЦЭУ) с использованием стандартных диагностических средств.

Недостатками этого подхода являются сложность и трудоемкость поиска и анализа неисправностей, так как источниками неисправностей могут быть как неисправности монтажа ПЛИС, так и ошибки, допущенные при проектировании логической структуры ЦЭУ. Устранение этих неисправностей требует привлечения дополнительных ресурсов для проведения диагностики.

1. Особенности контроля монтажа ПЛИС на печатных платах ЦЭУ

Для упрощения процедуры поиска неисправностей монтажа предлагается перейти от двухэтапной процедуры к трехэтапной, выделив в самостоятельный этап контроль исправности монтажа ЦЭУ. Этот этап предшествует этапу функционального контроля ЦЭУ.

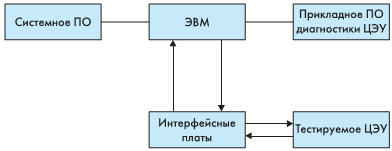

Рисунок 1. Структурная схема диагностического программноаппаратного комплекса

В этом случае тестирование монтажа ПЛИС на печатных платах должно осуществляться напроизводственном участке с использованием специализированного диагностического программно-аппаратного комплекса.

В данной статье рассматриваются вопросы практической реализации этапа контроля монтажа.

На рис. 1 представлена структурная схема диагностического программно-аппаратного комплекса (ДПАК) для тестирования состояния исследуемого ЦЭУ. Комплекс выполняет анализ качества монтажа ЦЭУ путем генерации и передачи на ЦЭУ тестовых воздействий, а также приема и распознавания реакции ЦЭУ. ДПАК состоит из ЭВМ, интерфейсных плат и прикладного диагностического программного обеспечения. Интерфейсные платы служат для обеспечения совместимости ЦЭУ и ЭВМ. Интерфейсные платы могут быть как стандартными, покупными, так и специализированными. Диагностическое программное обеспечение управляет процессом тестирования ЦЭУ, формирует входные тестовые последовательности и обрабатывает выходные сигналы ЦЭУ.

Тестовый сигнал представляет собой двоичную последовательность, состоящую из 0 и 1. В общем случае ПЛИС имеет P входов и Q выходов. При этом множество всех возможных входных воздействий равно 2P. Задача заключается в том, чтобы из этого множества выделить такой набор тестовых последовательностей, который гарантирует достоверность контроля.

Можно выделить следующие типовые неисправности монтажа:

- обрыв внешних соединений ПЛИС на печатной плате ЦЭУ;

- замыкание внешних соединений ПЛИС на линию питания;

- перепутывания внешних соединений ПЛИС и короткое замыкание;

- этих соединений между собой.

Обрыв соединения с функциональной точки зрения эквивалентен подаче постоянного сигнала, соответствующего логической 1 [1].

Замыкание соединения на линии питания также эквивалентно подаче постоянного сигнала, причем в случае замыкания на линию высокого потенциала этот сигнал соответствует логической 1, а в случае линии низкого потенциала — логическому 0.

Перепутывание соединений и короткое замыкание нескольких соединений между собой эквивалентно изменению функциональности ЦЭУ.

Особенностью этих неисправностей является их скрытый характер, что требует дополнительных ресурсов для их обнаружения и локализации. Эти неисправности могут, непосредственно не влияя на логическую структуру ПЛИС, изменять условия ее функционирования. Например, они могут быть причиной нагревания ПЛИС и возникновения побочных соединений, не предусмотренных логической структурой ПЛИС.

2. Алгоритм проверки монтажа ПЛИС на печатных платах

ПЛИС допускают многократное перепрограммирование логической структуры. Для проверки монтажа предлагается предварительно программировать ПЛИС специальной диагностической структурой, предназначенной только для тестирования монтажа. После окончания этапа тестирования монтажа ПЛИС программируется основной логической структурой ЦЭУ. Последовательность входных и выходных выводов у диагностической структуры должна быть такой же, как и у основной структуры ПЛИС.

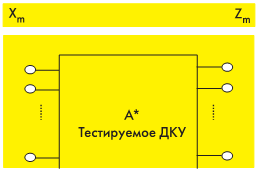

Неисправности монтажа являются подмножеством множества всех неисправностей ЦЭУ. Будем рассматривать ПЛИС как совокупность дискретных комбинационных устройств (ДКУ) с N-входами и N-выходами, где N≤min(P,Q) (рис. 2). Под ДКУ понимается устройство, состояния выходных контактов которого определяется только текущим состоянием входных контактов, то есть в структуре ДКУ отсутствуют цепи обратных связейи элементы памяти [2]. Будем считать, что у ДКУ входные и выходные контакты упорядочены, так что каждому контакту присвоен порядковый номер от 1 до N. Припрограммировании ПЛИС диагностической структурой n-й вход соединяется с n-м выходом, 1≤n≤N. При этом тестовые воздействия подаются непосредственно на входные выводы ДКУ, а их отклики фиксируются на выходных контактах [3]. Вэтом случае на формирование принимаемых данных влияют только неисправности монтажа. Ошибки внутреннего соединения выводов ПЛИС исключаются на этапе входного контроля.

Обозначим исправное ДКУ символом A. Под неисправностью монтажа ДКУ будем понимать последствия некоторого события, которые преобразуют исправное устройство A в некоторое другое, неисправное, отличное от A устройство A, и поддерживают его внеисправном состоянии в течение некоторого интервала времени Δt. Неисправности монтажа не изменяют последовательности входов и выходов ДКУ. На рис. 2 через A* обозначено тестируемое ДКУ.

Рисунок 2. Тестируемое ДКУ

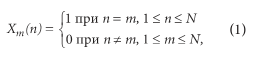

Обозначим множество тестовых последовательностей как {Xm}, а множество откликов — {Zm}. Каждая из этих последовательностей представляет собой N-разрядное двоичное слово (то есть число разрядов равно числу контактов ДКУ). Входной сигнал Xm представляет собой последовательность, укоторой m-й элемент равен 1, а остальные N–1 элементов — 0.

где n — номер контакта ДКУ, m — индекс входной последовательности.

Для реализации данной последовательности на -й входной контакт будем подавать напряжение, соответствующее 1, а на остальные входы — напряжение, отображающее 0. В алгоритме предполагается, что выходной сигнал Zm представляет собой отклик на соответствующее воздействие Xm.

При функциональном описании тестируемого ДКУ A* процедура диагностирования состоит в последовательном сравнении откликов Zm с соответствующими тестовыми последовательностями Xm. Правило диагностики может быть формализовано следующим образом. Монтаж тестируемого устройства является исправным (A*=A), если Zm=Xm для всех m. Монтаж тестируемого устройства является неисправным (A*≠A), если Zm ≠Xm хотя бы для одного mиз 1≤m≤N.

Таким образом, имеем:

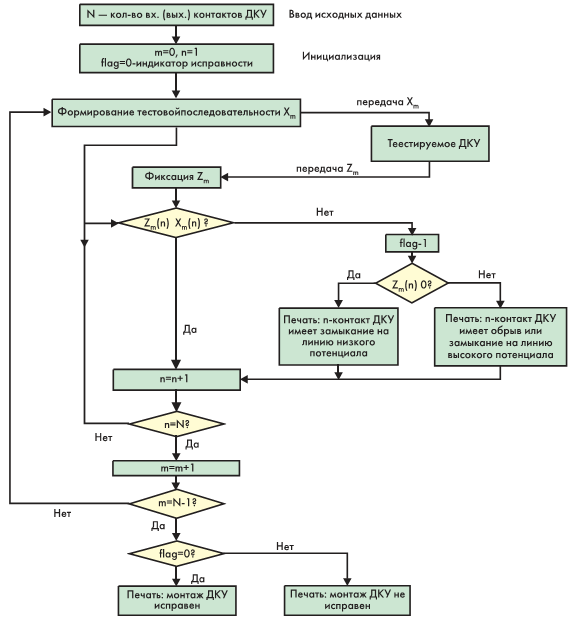

Структурная схема алгоритма диагностики монтажа ДКУ представлена на рис. 3.

Алгоритм дифференцирует вид неисправности монтажа и идентифицирует номер дефектного контакта. При этом выявленная неисправность может относиться как к входному, так и к выходному контакту ДКУ или к обоим контактам одновременно. Если Zm≠Xm , то найдется хотя бы один -й контакт, для которого Zm(n)≠Xm(n). При этом, если Zm(n)=1 при n≠m, то n-й контакт ДКУ имеет либо обрыв соединения, либо замыкается налинию высокого потенциала. В случае, если Zm(n)=0 при n=m, то n-й контакт ДКУ замыкается на линию низкого потенциала. Процедура формирования тестовой входной последовательности на рис. 3 реализует формулу (1).

Рисунок 3. Структурная схема алгоритма диагностики исправности дискретного устройства

Выводы

Предлагаемый подход к организации контроля работоспособности позволяет упростить процедуру поиска неисправностей сложных цифровых изделий на базе ПЛИС и существенно снизить трудоемкость обнаружения этих неисправностей. Контроль осуществляется с помощью диагностического программно-аппаратного комплекса, который включает в основном стандартные средства вычислительной техники. Разработано алгоритмическое и программное обеспечение диагностического программно-аппаратного комплекса. Количество генерируемых тестовых последовательностей линейно зависит от числа контактов ПЛИС. Предлагаемый алгоритм был апробирован при разработке сложной цифровой системы, построенной на базе ПЛИС фирмы Altera для партии из трех изделий. Исследуемая система состояла из ПЛИС с шириной входных и выходных шин данных более 200 линий каждая. Наибольшее количество дискретных комбинационных устройств, необходимых для реализации в одной ПЛИС, равнялось шести. Время, затрачиваемое на проверку качества монтажа печатной платы с тремя ПЛИС при использовании диагностического программно-аппаратного комплекса, составляет от трех до пяти минут. При традиционном подходе на проверку функционирования изделий аналогичной сложности может уходить до четырех часов и более. Причем при наличии неисправностей существенная часть этого времени уходит на обнаружение и локализацию дефектов монтажа.

Литература

- Пархоменко П. П. Основы технической диагностики. М.: Энергия. 1976.

- Угрюмов Е. П. Цифровая схемотехника. СПб.: БХВ — Санкт-Петербург. 2000.

- Беннеттс Р. Дж. Проектирование тестопригодных логических схем. М.: Радио и связь. 1990.