Фазовая автоподстройка частоты (PLL)

Источник: http://www.erg.abdn.ac.uk/users/gorry/eg3567/phy-pages/dpll.html

Перевел Бурховецкий Д.В.

Фазовой автоподстройкой частоты (PLL) является электронная схема, которая управляет генератор так, что он поддерживает постоянный сдвиг по отношению к фазе опорного сигнала. Генератор, как правило, находится в приемнике, и опорный сигнал извлекается из сигнала, полученного от удаленного передатчика. Фазовая автоподстройка частоты широко используются в космической связи для когерентной несущей

отслеживание и расширение порога, битовой синхронизации, а также для синхронизации.

Цифровая фазовая автоподстройка частоты (DPLL)

Цифровая фазовая автоподстройка частоты (DPLL) может включать в себя последовательный регистр сдвига, который получает на вход дискретные эталонные сигналы, в которых содержатся тактовые импульсы попадающие в регистр сдвига, принимают текущее время и восстанавливают стабильность тактов в фазу принимаемого сигнала, затем медленно корректирует фазу и регенерирует в соответствии с принимаемым сигналом.

Упрощенная схема фазовой автоподстройки частоты

Эта схема полезна, когда данные и часы отправляются вместе в течение определенного общего кабеля (например, в Манчестере кодирования), поскольку это позволяет приемнику отдельный (регенерации) тактового сигнала из полученных данных. Регенерации сигнала синхронизации затем используется для образца полученные данные и определить значение каждого бита получил.

Когда сигнал получен первый, регенерации часов и получила сигнал не будет приведена в соответствие. (Это происходит в начале кадра Ethernet, так как получатель не имеет знание которых передатчик отправил фрейм и, следовательно, частоты и фазы сигнала получил часы). Петля начинает отслеживать принимаемого сигнала, и в конечном итоге замки в до требуемого сигнала, что позволяет ему найти в центре каждого бита данных полученных и надежно расшифровать полученную информацию. Зная, что этот процесс требует времени, многие системы (в том числе Ethernet) используется преамбула, в которой содержатся известные и простые данные образцу, который увеличивает скорость, при которой доходы DPLL замок сигнал времени.

Эксплуатация Простые DPLL

Есть много конструкций фазовой автоподстройки контуру, но принципы работы похожа в каждом случае. Получил сигнал оцифровывается на местном тактовой частотой (которая кратной номинальной тактовой частоты регенерации, например, 8 или 32 раз). Каждый образец (0 или 1), помещается в регистр сдвига. Необходимость корректировки фазы обнаружено, просмотрев множество образцов принимаемого сигнала. В каждой регенерации бит период, регистр консультации. Если центр получил бит находится в центре регистр сдвига, 2 часы находятся в фазе. Если регенерации сигнала синхронизации отстает от опорного сигнала, то регулятор фазы должна компенсировать это путем продвижения регенерации часов. Если это приводит опорного сигнала, фазовый корректор должен сделать противоположные изменения.

С «Манчестер кодирования всегда содержит немного перехода (0-1 или 1-0) в центре каждого бита регистр сдвига (с помощью местных 32x часов) должен содержать либо значение:

00000000000000001111111111111111 (если 1 было отправлено и часы были заперты)

или

11111111111111110000000000000000 (если 0 было отправлено и часы были заперты).

Регистр сдвига содержит шаблон 11111000000000000000011111111111 если регенерации часы из соответствия полученных данных 5 часов местного периодов частоты.

Переходов в центре каждого бита позволяет замок на Манчестер кодированные сигналы особенно легко. Еще один способ ввести часы переходов в данных является использование 4b/5b или 8b/10b кодирования, как в Fast Ethernet и Gigabit Ethernet на витой паре.

После обновления поэтапного регулировки каждого периода получил бит, частота регенерации часы могут быть точно выровнены по необходимости reference.When разница будет найден, регенерации часы, как правило, продвинулись всего лишь небольшое количество каждый раз регистр сдвига для чтения, Таким образом, количество принятых бит периоды должны компенсировать большую разницу в 2 часов. Чем больше разница, тем больше времени требуется для цикла, чтобы установить желаемую частоту регенерации часов. После того как петля нашли желаемого тактовая частота регенерации, лишь незначительные изменения должны держать часы увязанные с полученными данными.

Одним из важных аспектов применения этой схемы, является то, что после фазы автоподстройки частоты нашла нужную частоту, шум в принимаемого сигнала вызывает только очень маленький (случайных) изменений в работе устройств ввода часы - часы регенерации продолжает оказывать хорошие задания, которые могут быть использованы для нахождения в центре каждого бита получил.

Преамбула

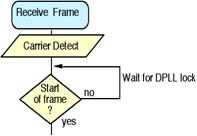

Когда данные передаются в рамки и DPLL используется для восстановления сроков (например, Ethernet), DPLL необходимо приобрести блокировку перед началом первого бит данных в кадре. Чтобы приобрести замок, требует DPLL получить бит, в начале каждого кадра таким образом, часто с приставкой набора битов, направленных на обеспечение блокировки DPLL, это называется «преамбулу». В Ethernet, состоит из преамбулы 8 байт, последний из которых имеет специальную последовательность, известная как начало Frame разделитель (СФР), который указывает, что актуальной информации следующим образом.

Узел начинает передачу, отправив 8 байт (64 бит) преамбуле последовательности. Он состоит из 62 переменных 1 и 0, за которой следует модель 11. Строго говоря, последний байт называется «Frame разделитель». Когда закодированная в Манчестере кодирования, в 10 Мбит / с, 62 бит переменного производить 5 МГц меандр.

Цель преамбула, чтобы дать время для приемника в каждом узле для достижения замок приемник цифровых систем фазовой автоподстройки частоты, который используется для синхронизации данных получают часы передавать данные часы. В тот момент, когда первый бит преамбулы получил, каждый получатель может быть в произвольном состоянии (т.е., произвольная фаза для своих местных часов). В ходе преамбуле он учится на правильную фазу, но при этом он может не заметить (или прибыль) число битов. Особый рисунок (11), поэтому используется для обозначения двух последних битов преамбулы (в результате быстрого transistion). Когда это будет получено, Ethernet интерфейс начинает получать собирать биты в байты для обработки слоя MAC.