Введення

Будова і принципи функціонування оперативної пам'яті

Огляд існуючих засобів тестування пам'яті

Аналіз проблеми тестування пам'яті

Алгоритм визначення обсягу пам'яті

Читання SPD

Висновки

Перелiк лiтератури

Актуальність

Оперативна

пам'ять - один

з найважливіших елементів комп'ютера.

Саме з неї процесор бере програми і вхідні дані для

обробки, у неї він записує отримані результати. Виробництво

оперативної пам'яті технологічно складний процес. Складність

виробництва полягає в тому, що переважає тенденція на постійне

зменшення розмірів інтегральних схем і підвищення вимог до готової

продукції, що в свою чергу порушує вимоги до матеріалів, з

яких виготовлена пам'ять, піддаючись постійному фізичному

впливу, він повинен, на тривалий час, зберегти свої властивості.

Все це робить неминучим поява несправностей у виготовлених

мікросхемах[8]. У будь-якій партії готових мікросхем завжди присутній

певних відсоток браку, здебільшого його відстежують на

виробництві, однак частина несправних мікросхем потрапляє на ринок, що

ж робити в тому випадку. Збої в роботі пам'яті можуть стати причиною

втрати цінної для користувача

інформації та частини системної ОС. Особливим випадком є несумісність

модулів

пам'яті

різних виробників між собою або з материнськими платами[9].

При експлуатації пам'яті важливо точно знати її дійсні характеристики.

Сучасні

материнські плати допускають настроювати деякі параметри, інформація

про

яких прочитується з самих модулів пам'яті. Це, в першу чергу

значення

таймінгів, які зберігаються в спеціальній пам'яті, SPD,

яка

знаходиться на модулі.

Система ідентифікує модулі пам'яті по протоколу Serial Presence Detect

(SPD).

Модуль SPD,

це енергонезалежна мікросхема EPROM

(обсягом 256 байт), в якій міститься інформація про модуль пам'яті, яка

необхідна для його правильного конфігурування: серійні номери виробів

та імена виробників і т.д. BIOS

зчитує ці дані при запуску, і для ініціалізації використовує їх.

Запущені під ОС програми діагностики читають SPD.

При порівнянні обсягу оперативної пам'яті, що виділяється ОС і BIOS з

реальною ємністю встановлених модулів, можна виявити різницю.

Названі причини свідчать про те, що способи програмної оцінки обсягу

пам'яті, її розподілу, а так само доступ до SPD є актуальними

завданнями у створенні архітектурної бази конкретної платформи

персонального комп'ютера.

Цілі і завдання

Метою

роботи є розробка алгоритмів тестування пам'яті, а також розробка

програмного забезпечення на основі розроблених алгоритмів.

Новими завданнями цієї проблеми є побудова нових тестових алгоритмів,

чия ефективність має в рази перевищувати існуючі аналоги.

Основні завдання, які підлягають вирішенню:

1.Аналіз існуючих алгоритмів

тестування

пам'яті.

2.

Розробка концепції нових алгоритмів.

3.

Розробка нових алгоритмів.

4.Розробка програмного забезпечення,

заснованого на

розроблених алгоритмах.

Оперативна пам'ять - частина системи комп'ютерної пам'яті, якій тимчасово зберігаються дані та команди, необхідні процесору для виконання різних операцій В даний час в персональних комп'ютерах IBM PC використовується пам'ять типу DDR SDRAM, DDR SDRAM II і DDR SDRAM III.Аббревіатура SDRAM розшифровується як Synchronous Dynamic Random Access Memory - синхронна динамічна пам'ять з довільним доступом, DDR - Double Data Rate (подвоєна швидкість передачі даних) . Загальний принцип організації та функціонування мікросхем динамічної пам'яті (DRAM) практично єдиний для всіх її типів - як первинної асинхронної, так і сучасної синхронної. Масив пам'яті можна розглядати як матрицю (двовимірний масив) елементів, кожен з яких містить одну або кілька фізичних осередків, здатних вміщати елементарну одиницю інформації - один біт даних. Осередки представляють собою поєднання транзистора (ключа) і конденсатора (запам'ятовуючого елемента) рис.1. Доступ до елементів матриці здійснюється за допомогою декодерів адреси рядки і адреси стовпця. З міркувань мінімізації розміру упаковки мікросхеми, адреси рядків і стовпців передаються по одинм і тим же адресним лініях мікросхеми. Особливістю пам'яті даного типу є те, що конденсатори з часом втрачають свій заряд, для запобігання втрати даних необхідно періодично оновлювати вміст комірок. У сучасних типах пам'яті, які підтримують режими автоматичної регенерації (у "пробудженому" стані) і саме регенерації (у "сплячому" стані), звичайно це є завданням внутрішнього контролера регенерації, розташованого безпосередньо в мікросхемі пам'яті. Схематичне зображення модуля оперативної пам'яті представлено на рис.2. Ще однією особливістю SDRA, є розбиття масиву даних на кілька логічних банків (як мінімум - 2, зазвичай - 4). Розбиття масиву пам'яті SDRAM на банки було введено, головним чином, з міркувань продуктивності. Розрядності шини даних контролера пам'яті і для всіх сучасних типів контролерів пам'яті SDRAM (DDR, DDR2 і DDR3) становить 64 біта. Особливістю SDRAM є одне банкові (або "одноранковие", single-rank) і двох банкові ("двухранковие", dual-rank) модулі. Двох банкові модулі пам'яті найбільш часто представлені конфігурацією "16 мікросхем x8", при цьому один з фізичних банків (перші 8 мікросхем) розташований з лицьового боку модуля, а другий з них (решта 8 мікросхем) - з тильного. Наявність більше однієї фізичної банку в модулі пам'яті не можна вважати певною перевагою, тому що може вимагати збільшення затримок командного інтерфейсу. Ще до появи першого типу синхронної динамічної оперативної пам'яті SDR SDRAM стандартом JEDEC передбачається, що на кожному модулі пам'яті має бути присутня невелика спеціалізована мікросхема ПЗУ, іменована мікросхемою "послідовного виявлення присутності" (Serial Presence Detect, SPD). Ця мікросхема містить основну інформацію про тип і конфігурації модуля, тимчасові затримки, яких необхідно дотримуватися при виконанні тієї або іншої операції на рівні мікросхем пам'яті, а також іншу інформацію, що включає в себе код виробника модуля, його серійний номер, дату виготовлення і т.п.Схема взаємодії оперативної пам'яті з іншими компонентами ПК зображена на рис.3.

Рисунок 1 – Устройство ячейки динамической памяти.

Рисунок 2 –Схематичне зображення модуля оперативної пам'яті (1); мікросхеми пам'яті (2); матриці (3) і окремої комірки пам'яті (4).

Рисунок 3 – Схема взаємодії оперативної пам'яті з іншими компонентами ПК.

Memtest86 +.

Цю утиліту можна запускати з завантажувальної дискети або компакт-диска. MemTest86 +, крім своїх прямих обов'язків, визначає основні характеристики комп'ютера, такі як чіпсет, процесор і швидкість роботи пам'яті. У програми є два режими роботи: basic і advanced (основний і розширений). Вони відрізняються часом тестування. У основному режимі можна визначити якісь глобальні проблеми з пам'яттю, а в розширеному режимі проводиться більш ретельне тестування.

Docmem - Тест оперативної пам'яті.

Docmem - це зручна програма для тестування пам'яті, яка користується заслуженою популярністю. Її можна переписати з сайту виробників безкоштовно, тільки потрібно зареєструватися. Програму Docmem потрібно записати на дискету, за допомогою якої потім треба завантажити комп'ютер. Програма теж пропонує два режими тестування: швидкий (quick) і основний (burn in), який виконується, поки не буде зупинений користувачем.

Windows memory diagnostic - Тест оперативної пам'яті.

Компанія Microsoft пропонує власну діагностичну програму, схожу на дві попередні. Вона пропонується у вигляді стандартного інсталяційного файлу з образом завантажувального компакт-диска і програмою для створення завантажувальної діскети. Windows memory diagnostic - це більш проста програма, ніж попередні. Крім того, вона має додатковий набір тестів для перевірки комп'ютера. Вона дозволяє визначити, який саме модуль є джерелом проблем, якщо в системі встановлено кілька модулів пам'яті. Щоб запустити Memory Diagnostic, запустіть файл програми і виберіть, що вам зручніше - створити завантажувальний компакт-диск або дискету. При виборі компакт-диска у вас запитають, куди зберегти його образ. Запам'ятайте, куди ви його зберегли, і скористайтеся якоюсь програмою для запису CD дисків, наприклад, Nero.

Якщо ви виберете створення завантажувальної дискети (create startup disk), то залишиться просто вставити в дисковод дискету і почекати, поки на неї буде записана вся потрібна інформація. Після цього перезавантажте свій комп'ютер, завантаживши його за допомогою створеної дискети або компакт-диска.

Основним недоліком цих програм є тестування пам'яті в щадять режиму. Незважаючи на просунутість тестів і багатий алгоритмічний набір, вони не можуть виявляти проблеми, що виникають у режимах, близьких до критичних, тому бувають ситуації, в яких всі запропоновані тестери не виявлять помилок, а під час максимального завантаження комп'ютера починають відбуватися збої в роботі оперативної пам'яті. Виходом з даної ситуації є написання власної програми тестування пам'яті.

Розгін пам'яті - це дуже радикальний засіб збільшення продуктивності, але і надзвичайно вимогливе до якості модулів пам'яті. Втім, неякісні модулі можуть давати збій навіть у штатному режимі без будь-якого розгону. Наслідки таких помилок дуже різні: від аварійного завершення програми до втрати та спотворення даних для обробки.

Судячи з усього, придбання "битою" пам'яті - аж ніяк не рідкість і зі збоями пам'яті народ стикається досить регулярно. До його негайного відмови. Найчастіше дефект виявляється лише при певному збігу низки обставин. Важковагове додаток, "ганяють" пам'ять "і в хвіст, і в гриву", має всі шанси за короткий час "підібрати" потрібну комбінацію, яка провокує збій.

Популярні діагностичні програми, навпаки, тестують вельми обмежений спектр режимів у вельми сприятливих умовах. Відповідно, і ймовірність знайти помилку в останньому випадку значно нижче.

Вихід - Розробляти власну програму для тестування. По-перше, необхідно враховувати, що ймовірність збою тісно пов'язана з температурою кристала. Чим вище температура - тим вірогідніше збій. А температура в свою чергу залежить від інтенсивності роботи пам'яті. При лінійному читанні осередків мікросхема пам'яті за рахунок пакетного режиму встигає декілька призупинення, підтримуючи всередині себе помірну температуру. Дійсно, при запиті одного осередку вся DRAM-сторінка читається цілком, зберігаючись у внутрішніх буферах, і до тих пір, поки не буде запитана наступна сторінка цього ж банку, ніяких звернень до ядра пам'яті не відбувається!

Тому, перш ніж приступати до реального тестування, пам'ять необхідно як слід прогріти, читаючи її з кроком, рівним довжині DRAM-банку, це змусить ядро цього банку працювати максимально інтенсивно, на кожному кроці виконуючи процедуру читання і відновлювальної запису даних. Не варто тестувати кілька банків одночасно. По-перше, це кілька знизить температуру "напруження" кожного з них, а, по-друге, перепад температур усередині кристала збільшує вірогідність виявлення збою.

Коли модуль пам'яті нагрівся так, що не втримаєшся рукою, саме час приступати до справжніх тестів. Заповнюємо DRAM-сторінку контрольної послідовністю чисел (далі по тексту - шаблоном), перемикаємо сторінку, щоб гарантовано оновити комірки пам'яті (в іншому випадку мікросхема може повернути вміст своїх буферів, не звертаючись до матриці пам'яті). Знову перемикаємо сторінку назад і перевіряємо, що ми записали.

До шаблону пред'являються дуже жорсткі вимоги. По-перше, він повинен тестувати кожен біт осередку, причому, на обидва значення - одиницю і нуль, оскільки "биті" осередки матриці можуть давати або "завжди нуль", або "завжди одиниця". По-друге, вкрай бажано, щоб під восьмерню слові сусідні біти мали протилежні значення. Така комбінація створює найбільший рівень перешкод і тим самим провокує систему на помилку. По-третє, шаблон повинен забезпечувати виявлення помилок адресації, тобто ситуації, коли мікросхема повернула зміст осередку не того рядка та стовпця. Оскільки всі ці вимоги взаємовиключні, для тестування буде потрібно кілька шаблонів. Тільки не забувайте час від часу виконувати "неодружене" читання для підтримки температури мікросхеми на максимально досяжному рівні, інакше ефективність тесту почне падати.

Розглянемо перебір сторінок. Послідовний перебір, потім - хаотичні звернення до сторінок за випадковим шаблоном. Однак цього не досить, сучасні контролери пам'яті самостійно визначають кращий порядок обробки запитів, проаналізувавши алгоритм, він може видати зміст буфера, замість реального значення.

Для обходу механізму буферизації необхідно перевіряти осередку не відразу після запису, а через деякий час, коли внутрішні буфери контролера будуть гарантовано перекриті подальшими запитами. Це ж дозволяє виявити помилки регенерації, коли з-за якихось дефектів заряд з клітинки матриці стікає раніше, ніж її встигають регенерувати.

Розроблений алгоритм програми реалізує функції визначення обсягу встановленої пам'яті, отримання карти розподіл оперативної пам'яті, читання вмісту мікросхеми SPD.

Визначення обсягу оперативної пам'яті виконується за допомогою переривання BOIS int 15h ax = E810h [2]. Воно дозволяє визначити обсяг встановленої пам'яті до 4 Гб. Переривання повертає в регістр AX кількість 64 кб. блоків між 1 і 16 мегабайтами встановленої пам'яті, в регістр BX кількість 64кб. блоків між 16Мб. і 4гб. встановленої пам'яті, прочитавши значення цих регістрів визначаємо об'єм встановленої оперативної пам'яті.

Отримання карти розподіл адресного простору встановленої пам'яті виконуємо за допомогою переривання BIOS int 15h AX = E820h. Воно дозволяє формувати карту розподілу адресного простору оперативної пам'яті. В якості вхідних параметрів передається покажчик на буфер в регістрі ES: DI, об'єм буфера у регістрі ECX, EBX, для першого виклику дорівнює "0", для подальших викликів в EBX буде адреса наступного блоку пам'яті, яке буде повернуто перед йде викликом переривання. Після вдалого виклику переривання в буфер повертаються значення, що характеризують розглянутий ділянку пам'яті. [3] Структура даних, що повертаються наведена в таблиці 1.

Таблица 1.Структура даних, що повертаються

| Зсув | Назва | Опис |

| 0 | BaseAddrLow | Low 32 Bits of Base Address |

| 4 | BaseAddrHigh | High 32 Bits of Base Address |

| 8 | LengthLow | Low 32 Bits of Length in Bytes |

| 12 | LengthHigh | High 32 Bits of Length in Bytes |

| 16 | Type | Address type of this range |

Поле Typе визначає можливі типи пам'яті, його структура приведена у таблиці 2. Таблица 2. Структура поля е.

| Значення | Опис |

| 1 | AddressRangeMemory, available to OS |

| 2 | AddressRangeReserved, not available to OS |

| 3 | AddressRangeACPI, available to OS |

| 4 | AddressRangeNVS,not available to OS |

Виклик даного переривання виконується у циклі, поки значення регістра EBX не буде дорівнює "0".

Жоден сучасний модуль пам'яті не може обійтися без компонента - мікросхеми SPD (Serial Presence Detect). Інтерфейс послідовного детектування, регламентований на даний момент для всіх модулів пам'яті форм-фактора SIMM / DIMM / RIMM, використовує шину управління системою (SMBus - System Management Bus), сумісний зі специфікацією Inter-IC (I2C або IIC). Принцип використання шини SMBus у разі SPD зводиться до передачі даних від мікросхеми EEPROM. [10]

Для доступу до SPD необхідно використовувати конфігураційні регістри шини SMBus, які знаходяться в конфігураційному просторі PCI.

Конфігураційний адресний простір PCI складається з 256 байт, які можна адресувати, знаючи номер шини PCI, номер пристрою і номер функції в пристрої. Перші 64 байта з 256 стандартизовані, а інші регістри можуть бути використані на розсуд виготовлювача пристрою.

Доступ к PCI через порты I/O. Доступ до PCI через порти I / O. Для роботи з шиною PCI в PC-AT і сумісних машинах виділено два основних порту:

-0CF8h -W порт адреса Address.

-0CFCh RW порт данных Data.

Обидва порти є 32 бітними. Порт адреси являє собою наступну 32 бітну структуру, яка задає шину, пристрої, і адреса регістра в конфігураційному просторі пристрою. Структура порту адреси наведена в таблиці 3.

Таблица 3. Порт адреса.

| 31 | 30.....24 | 23.....16 | 14....11 | 10....8 | 7....2 | 1 | 0 |

| C | Резерв | Шина | пристрій | функція | Індекс регістру |

У цій структурі пристрій - це фізично присутня пристрій, де функція -

це логічне устройство.С - прапор доступу до пристрою. Молодші два біти

в порту адреси завжди 0.По закінчення роботи з пристроєм слід скинути

адреса в 0.

Першим кроком у доступі до мікросхеми SDP є створення списку PCI пристроїв, шляхом послідовного перебору всіх можливих адрес PCI і запиту читання нульового регістру. Якщо у відповідь на запит нульового регістру повертається 0FFFFh, то пристрою не існує. Якщо пристрій існує ми запам'ятовуємо його адресу у списку пристроїв.

Другим кроком є пошук шини SMBus в отриманому списку PCI пристроїв. Пошук здійснюється шляхом опитування кожного адреси зі списку PCI пристроїв та перевірки вмісту конфігураційних регістрів, з метою пошуку ознакою SMBus шини [4].

Третій крок. У разі якщо шина SMBus знайдена, вибираємо один з можливих адрес SDP (50h, 51h, 52h, 53h), після чого виконуємо побайтного читання 256 байт в буфер, починаючи з поточного адреси.

Наступним етапом є взаємодія з контролером SMBus через його діапазон портів введення-виведення. Базова адреса SMB_Base. Обнуляємо статусні біти в регістрі Host Status (SMB_Base +0) для підготовки контролера до чергової операції. Біти цього регістра використовують дисципліну Read / Write Clear, і обнуляються при записі "1" в них.

Надсилаємо 8-бітний адресу осередку мікросхеми SPD, яку потрібно прочитати. Він записується в регістр Host Command (SMB_Base +3). При виконанні транзакції на шині SMBus, значення цього регістра передається в полі Command.

Передаємо 8-бітний адресу мікросхеми SPD, до якої виконується звернення. Він записується в регістр Transmit Slave Address (SMB_Base +4). При виконанні транзакції на шині SMBus, значення цього регістра передається в полі Slave Address.

Запускаємо виконання транзакції, параметри якої були підготовлені. Для цього необхідно записати код операції в регістр Host Control (SMB_Base +2). Для запуску операції передачі байта використовується код 01001000b = 48h.

Контролер SMBus починає операцію читання байта з SPD. Програма повинна чекати завершення операції. Опитуємо стан біта Host Busy, це біт 0 регістру Host Status (SMB_Base +0). За значенням Host Busy = 1 визначаємо момент початку операції, потім очікуємо Host Busy = 0, тобто завершення операції. Відсутність очікуваного події протягом заданого інтервалу (близько 50 мс) інтерпретується як помилка - таймаут шини.

Прочитуємо з регістра Host Data 0 (SMB_Base +5) байт, прочитаний з SPD. Його значення достовірно лише за відсутності помилок.

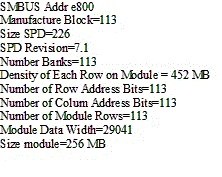

Перевіряємо відсутність помилок. Для цього зчитуємо регістр Host Status (SMB_Base +0) і аналізуємо статусні біти. Після успішного завершення транзакції, стан бітів 4-1 повинно бути 0001b. Маскуємо вказане бітове поле і перевіряємо його значення. Отримавши 256 байт перевіряємо їх значення, якщо всі байти рівні FF, то SPD за даною адресою недоступна. Якщо SPD присутній, то виконуємо аналіз цікавлять нас бітів з лічених буфера. Результат роботи програми, розробленої магістром Хачатуровим, наведен на рисунку 4.

Рисунок 4.Фрагмент результату роботи програми. Адреса шини SMBus і вміст SPD.

Тестування програми показало, що вона успішно виконує поставлені завдання: визначення обсягу оперативної пам'яті, встановленої на комп'ютері, створення карти розподілу пам'яті, читання мікросхеми SPD. Спосіб доступу до SDP, розглянутий у цій статті має особливості пов'язані з реалізація доступу до шини SMBus різна на різних чіпсетах. Розроблена програма може бути використана при розробці операційних систем "з нуля", розробці спеціалізованого програмного забезпечення для діагностики, оскільки може бути запущено на частково справній системі і виконати свої функції, при налагодженні процесу взаємодії функцій програми з апаратурою.

Научная новизна

Наукова новизна роботи полягає в розробці алгоритму тестування пам'яті, який буде заснований на методі розігріву, а так само в доказі ефективність нового алгоритму, що дозволяє виявити, на відміну від раніше існуючих алгоритмів, несправності пам'яті, які з'являються при екстремальних режимах роботи пам'яті. Розробляються алгоритми відрізняються також тим, що мають малу ресурсомісткість.

1. OSDev Wiki [Electronic resource]/ Интернет-ресурс. –Режим доступа: www/URL : http://ru.osdev.wikia.com/wiki/Карта_распределения_памяти

2. INTERRUPT LIST [Electronic resource]/ Интернет-ресурс. –Режим доступа: www/URL : http://www.ctyme.com/intr/rb-1739.htm

3. INTERRUPT LIST [Electronic resource]/ Интернет-ресурс. –Режим доступа: www/URL : http://www.ctyme.com/intr/rb-1741.htm

4. SMBus [Electronic resource]/ Интернет-ресурс. –Режим доступа: www/URL : http://smbus.org/

5. JEDEC [Electronic resource]/ Интернет-ресурс. –Режим доступа: www/URL : http://www.jedec.org/

6. М. Гук. Аппаратные средства IBM PC. Энциклопедия. 3-е изд. [Текст]/ М. Гук// “Питер” 2008.-C.1072.

7. INTEL [Electronic resource]/ Интернет-ресурс. –Режим доступа: www/URL : http://www.intel.com/index.htm?ru_RU_05

8. CITFORUM [Electronic resource]/ Интернет-ресурс. –Режим доступа: www/URL : http://citforum.ru/book/optimize/ram.shtml

9. Lipworld [Electronic resource]/ Интернет-ресурс. –Режим доступа: www/URL : http://www.lipworld.by.ru/Lipworld_Text/zelezo/ozu/vvedenie.html

10. Wikipedia [Electronic resource]/ Интернет-ресурс. –Режим доступа: www/URL : http://en.wikipedia.org/wiki/Serial_presence_detect