Abstract. Summary of research and developments

Contents:

- Introduction

- Conclusion

Substantiation of subject topicality

Today electronics and automation is large part of our lives, we sometimes do not notice, that the associated with her in almost all spheres of our activity. Now for the implementation of digital systems as a hardware basis is often used PLD (programmable logic integrated scheme). The use of PLDs to accelerate development, improve reliability, the degree of integration produced and razrabatyvaemy devices.

The most important part of any digital system is a control device, whose effectiveness largely determines the characteristics of the system. The principle of microprogram control has been proposed 1951. M. Wilkes, and presupposes the existence of any digital system control unit (CU) coordinating the work of all units of the system. In the theme of diploma work addresses microprogram control device (MCI). Microprogram control unit is divided into automata "programmable" logic, which is based on storage management teams in memory or on machines with "hard" logic, which is a scheme with a clear sequence, synthesized by description of a given abstract machine. Each of these types of machines have their disadvantages, which successfully solved using CMCU (compositional microprogram control unit). However, more effectively be used CMCU with multiple sources of codes.

One of the most popular PLDs are the CPLD. The high cost of this basis puts the current the objective of reducing hardware expenses in the scheme.

Purposes and tasks

Purpose of work is reduce hardware expenses in the scheme CMCU by minimizing logical scheme through the use of structures with multiple sources of codes that would reduce the cost of the final product.

Scientific novelty

Scientific novelty of the results of master's work will be to develop structures CMCU focused on minimizing the cost. The planned scientific value would be structuring CMCU with better performance in the basis of CPLD.

Description of results

Necessary for the conduct of research data were obtained using the software package consisting of the following components:

Animation 4 frames, 13,6 KB, number of cycles: 9

The system includes:

- FSM-Editor - a specialized tool allows you to create a graph scheme of algorithm (GSA) through their graphic input or automatic packet generation according to specified parameters. Further, the description algorithm can be saved in XML.

- VHDL-Generator - a specialized tool designed to produce VHDL code the required control device according to the chosen structure and description of the algorithm in XML.

- Xilinx ISE - a development tool, free of charge provided by Xilinx. Allows on the basis of VHDL description of the control unit to obtain estimates of the characteristics of hardware costs for implementing algorithm on PLD CPLD.

- GNU Octave - free analogue MathLab. Used to analyze data obtained from the Xilinx ISE and build graphics

Results

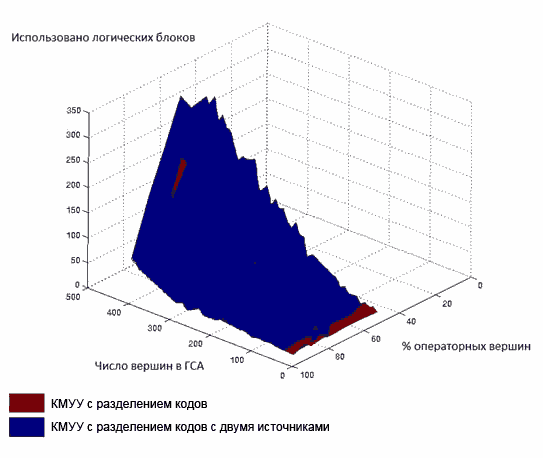

As a result of the software package had been received some dependencies, reflecting the effectiveness of

some of the proposed structures (shown in the figure). The drawings reflect the surface that determines under what

conditions, the minimum hardware cost. The surface is painted the color of the structure for which

the minimum in each of its points.

Conclusions

Research has shown that in comparison with the base CMCU, the application of the proposed structure can reduce hardware expenses.

As the project today can be concluded that further research should be aimed at adapting the proposed structure to the base PLD CPLD, and to develop methods optimization provided by the scheme.

Sources

- Baranov S. Logic Synthesis for Control Automata. – Kluwer Academic Publishers, 1994. – 312 pp.

- Соловьев В.В. Проектирование цифровых схем на основе программируемых логических интегральных схем. – М.: Горячая линия-ТЕЛЕКОМ, 2001. – 636 с.

- Barkalov A., Titarenko L. Logic Synthesis for Compositional Microprogram Control Units. – Berlin: Springer, 2008. – 272 pp.

- Maxfield C. The Design Warrior’s Guide to FPGAs. – Amsterdam: Elseveir, 2004. – 541 pp.

- Баркалов А.А., Палагин А.В. Синтез микропрограммных устройств управления. - Киев: ИК НАН Украины, 1997. - 156с.

- Саломатин В.А., Баркалов А.А., Стародубов К.Е. Оптимизация логической схемы микропрограммного устройства управления на ПЛМ и ПЗУ // УСиМ. - 1987. - №2. - С. 57-60.

- Баркалов А.А. Оптимизация логической схемы автомата Мура на CPLD / А.А. Баркалов, А.В. Матвиенко, С.А. Цололо // Комп'ютерні засоби, мережі та системи. – 2007. – № 6. – С. 46-51.

- Баркалов А.А. Оптимизация схемы МПА Мура на CPLD / А.А. Баркалов, С.А. Ковалев, С.А. Цололо // Материалы Восьмого международного научно-практического семинара «Практика и перспективы развития партнерства в сфере высшей школы». – Донецк-Таганрог, 2007. – Том 3. – С. 26-36.

- Zeidman B. Designing with FPGAs and CPLDs / B. Zeidman. – Elsevier, 2002. – 224 pp.

- Технология устройств CPLD [Электронный ресурс]: Режим доступа: URL: http://www.parallel.ru/FPGA/cpld.html