Реферат за темою випускної роботи

Зміст:

- Введення

- Огляд

- Висновок

Актуальність

На сьогоднішній день електроніка і автоматика є частиною нашого життя, ми, часом не помічаючи, тісно стикаємося з нею практично у всіх сферах діяльності. Зараз для реалізації цифрових систем задля апаратного базису часто використовується ПЛІС (інтегральні логічні схеми). Застосування ПЛІС дозволяє прискорити розробку, збільшити надійність, ступінь інтеграції вироблених і розроблюваних пристроїв.

Найважливішою частиною будь-якої цифрової системи є пристрій керування, ефективність якого багато в чому визначає характеристики системи. Принцип мікропрограмного управління був запропонований в 1951р. М. Уїлксом і передбачає наявність у будь-який цифровий системи пристрою управління (УУ), координує роботу всіх блоків системи. У темі дипломної роботи розглядаються мікропрограмні пристрої керування (Муу). Мікропрограмні пристроЇ управління поділяються на автомати з «програмованою» логікою, які засновані на зберіганні команд у керуючої пам'яті і на автомати з «жорсткою » логікою, які представляють собою схему з чіткою послідовністю, синтезовану з опису заданому абстрактним автоматом. У кожного з цих типів автоматів є свої мінуси, які з успіхом вирішуються при використанні КМПК (композиційних мікропрограмних пристроїв керування). Однак більш ефективно було б використовувати КМПК з декількома джерелами кодів.

Одними з найбільш популярних ПЛІС є CPLD. Висока вартість цього базису ставить актуальну задачу скорочення апаратурних витрат у схемі.

Цілі і задачі

Метою роботи є зменшення апаратурних витрат у схемі КМПК, шляхом мінімізації логічної схеми за рахунок застосування структури з кількома джерелами кодів, що призведе до зменшення вартості кінцевого продукту.

Передбачувана наукова новизна і наукова цінність

Наукова новизна отриманих результатів магістерської роботи буде полягати в розробці структури КМПК, орієнтованої на мінімізацію вартості. Планована наукова цінність буде полягати в розробці структури КМПК з поліпшеними характеристиками в базисі CPLD.

Локальний огляд теми

У Донецьку даною темою займається ДонНТУ, проходять дослідження на тему синтезу і оптимізації керуючих пристроїв, на тему захищено досить велика кількість магістерських робіт, писалися дисертації.

- Мірошкин Олександр Миколаевич займався синтезом і дослідженням композиційних мікропрограмних пристроїв керування з базовою структурою.

- Лаврік Олександр Сергійович займався синтезом і дослідженням композиційних мікропрограмних пристроїв керування з модифікованою системою мікрокоманд на ПЛІС.

- Цололо Сергій Oлексійович займався дослідженням методів синтезу пристроїв керування на запрограмованих користувачем вентильних матрицях.

- Професор Баркалов Олександр Олександрович працює на кафедрі ЕОМ з 1976 року. Область наукових інтересів - синтез мікропрограмних пристроїв управління в базисі програмованих логічних пристроїв.

Національний огляд теми

- http://www.opu.ua/ru/index.html Одеський національний політехнічний університет, кафедра «Комп'ютерні інтелектуальні системи та мережі».

- http://snu.edu.ua/welcome.php Східноукраїнський національний університет ім. В. Даля, кафедра автоматики і систем управління.

- http://www.kture.kharkov.ua Харківський національний університет радіоелектроніки.

Світовий огляд теми

- http://iaac.technion.ac.il/home.html Ізраїльська асоціація автоматичного керування (IAAC), професор Езра Зехеб.

- http://www.iie.uz.zgora.pl/ Інститут інформатики та електроніки Зеленогурського університету (Зелена Гора, Польща).

- http://scwww.math.uni-augsburg.de/~control/indexen.html Група університету Аугзбурга (Німеччина) на чолі з професором, доктором Фріцем Колоніусом.

Опис отриманних результатів

Необхідні для проведення досліджень дані були отримані за допомогою програмного комплексу складається з наступних частин:

Анiмацiя 4 кадра, розмiр 13,6 кб, кiлькiсть циклiв: 9

До складу системи входять

- FSM-Editor - спеціалізоване засіб дозволяє створювати граф-схеми алгоритму (ГСА) шляхом їх графічного введення або автоматичною пакетної генерації згідно заданим параметрам. Далі, опис алгоритму можна зберегти у форматі XML.

- VHDL-Generator - спеціалізоване засіб призначений для одержання VHDL коду необхідного пристрої управління відповідно до обраної структурі і опису алгоритму у форматі XML.

- Xilinx ISE - засіб розробки, безкоштовно надається компанією Xilinx. Дозволяє на основі VHDL опису пристрою управління отримати оціночні характеристики апаратурних витрат при реалізації алгоритму на ПЛІС CPLD.

- GNU Octave - безкоштовний аналог MathLab. Використовується для аналізу даних, отриманих від Xilinx ISE і побудови графіків.

Отриманні результати

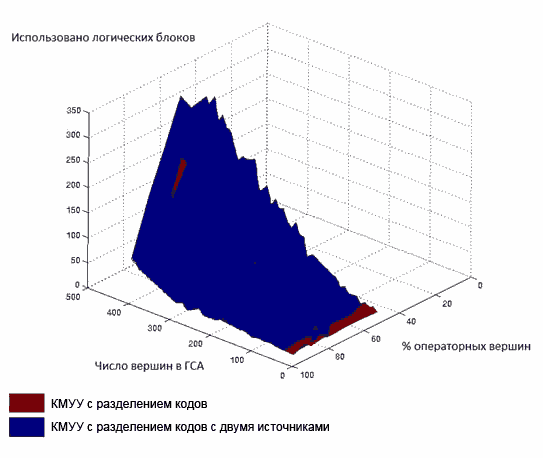

У результаті роботи програмного комплексу були отримані деякі залежності, що відображають ефективність

деяких із запропонованих структур (відображено на рисунку). На рисуннках відображена поверхню, визначальна при

яких умовах досягається мінімум апаратурних витрат. Поверхня пофарбована кольором тієї структури, для

якої досягається мінімум в кожній її точці.

Висновки

Дослідження показали, що у порівнянні з базовим КМПК, застосування запропонованої структури дозволяє знизити апаратурні витрати.

Станом проекту на сьогоднішній день можна зробити висновок про те, що подальші дослідження повинні бути спрямовані на адаптацію запропонованої структури до базису ПЛІС CPLD, а також на розробку методів оптимізації представленої схеми.

Джерела

- Baranov S. Logic Synthesis for Control Automata. – Kluwer Academic Publishers, 1994. – 312 pp.

- Соловьев В.В. Проектирование цифровых схем на основе программируемых логических интегральных схем. – М.: Горячая линия-ТЕЛЕКОМ, 2001. – 636 с.

- Barkalov A., Titarenko L. Logic Synthesis for Compositional Microprogram Control Units. – Berlin: Springer, 2008. – 272 pp.

- Maxfield C. The Design Warrior’s Guide to FPGAs. – Amsterdam: Elseveir, 2004. – 541 pp.

- Баркалов А.А., Палагин А.В. Синтез микропрограммных устройств управления. - Киев: ИК НАН Украины, 1997. - 156с.

- Саломатин В.А., Баркалов А.А., Стародубов К.Е. Оптимизация логической схемы микропрограммного устройства управления на ПЛМ и ПЗУ // УСиМ. - 1987. - №2. - С. 57-60.

- Баркалов А.А. Оптимизация логической схемы автомата Мура на CPLD / А.А. Баркалов, А.В. Матвиенко, С.А. Цололо // Комп'ютерні засоби, мережі та системи. – 2007. – № 6. – С. 46-51.

- Баркалов А.А. Оптимизация схемы МПА Мура на CPLD / А.А. Баркалов, С.А. Ковалев, С.А. Цололо // Материалы Восьмого международного научно-практического семинара «Практика и перспективы развития партнерства в сфере высшей школы». – Донецк-Таганрог, 2007. – Том 3. – С. 26-36.

- Zeidman B. Designing with FPGAs and CPLDs / B. Zeidman. – Elsevier, 2002. – 224 pp.

- Технология устройств CPLD [Электронний ресурс]: Режим доступу: URL: http://www.parallel.ru/FPGA/cpld.html