ТЕСТИРОВАНИЕ ЗНАНИЙ ПО VHDL НА БАЗЕ ПАКЕТА ATP4

Авторы: Ю. Е. Зинченко, А. А. Корченко –,А. Л. Масюк

Источник: «Образование и виртуальность – 2002».

Сборник научных трудов 6-й Международной конференции Украинской ассоциации

дистанционного образования – Харьков-Ялта, 2002.

Аннотация

Рассматривается пакет АТР4, предназначенный для тестирования знаний студентов об аппаратном описании языка VHDL. АТР4 выполняет интерактивное тестирование по широкому спектру типов вопросов. Система реализована на Object Pascal с использованием RAD Borland Delphi 5 от Inprise corp. Его можно использовать для тестирования VHDL-знаний на разных уровнях обучения. Система внедрена в нескольких вузах Украины.

ТЕСТИРОВАНИЕ ЗНАНИЙ ПО VHDL НА БАЗЕ ПАКЕТА ATP4

Актуальность разработки обучающих и тестирующих программ в настоящее время ни у кого не вызывает сомнений. Известно множество подобного рода программ, в том числе и по обучению языкам описания (программирования) аппаратуры (HDL – Hardware Description Language), среди которых наибольшую популярность получили VHDL и VERILOG. Так например, получила широкое распространение обучающая система EVITA, поставляемая в составе САПР Active-HDL [1]. Имеются также онлайновые тестирующие программы, размещенные на сервере компании ALDEC [2] и на сервере НТУУ-КПИ[3]. Анализ этих систем показал их общие недостатки: ограниченность типов и отсутствие возможности редактирования задаваемых вопросов, а также сложность адаптации к учебному процессу.

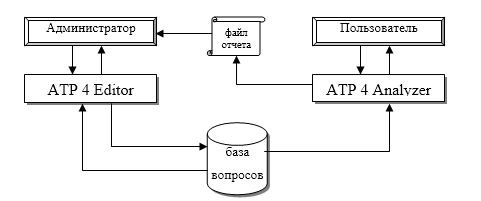

В данной работе предлагается система ATP4, предназначенная для тестирования знаний по языку VHDL, в которой авторами предпринята попытка преодолеть указанные недостатки. Структура пакета ATP4 приведена на рис.1.

Рисунок 1 – Структура пакета ATP 4

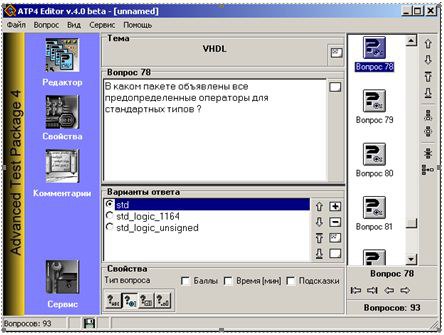

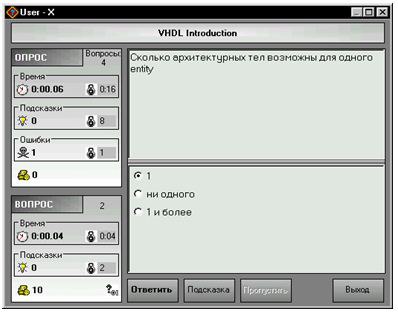

Работа пакета АТР4 организуется следующим образом. На предварительном этапе Администратором (преподавателем или уполномоченным лицом) создается база вопросов к конкретному опросу (опрос к лабораторной работе, промежуточный контрольный опрос по лекционному материалу, рейтинговый, модульный, экзаменационный опрос и т.д.). На этом этапе используется ATP 4 Editor (рис.2). На основе подготовленной базы вопросов далее с помощью ATP 4 Analyzer (рис.3) осуществляется тестирование знаний студентов. По результатам тестирования анализатор генерирует файл отчета, который предполагается использовать для автоматизации учета успеваемости в «электронном журнале».

Рисунок 2 – Редактор базы вопросов

Рисунок 3 – Окно анализатора ответов

ATP 4 реализован на языке Object Pascal с использованием RAD Borland Delphi 5 фирмы Inprise. Основные возможности пакета:

- создание базы вопросов по любой теме практически без ограничения на ее объем;

- использование четырех типов вопросов: «однозначный ответ», «одиночный выбор», «множественный выбор», «хронология»;

- гибкие настройки по ограничению времени, количества подсказок, допущенных ошибок, а также по оценке ответов студента;

- защита базы вопросов от несанкционированного доступа и изменения;

- предоставление полного отчета по проведенному опросу и размещение его в требуемом месте;

- возможно параллельное проведение опроса нескольких студентов (по количеству компьютеров), что экономит время;

- исключается возможность необъективной оценки знаний студента; объективность оценки повышается также за счет того, что каждый студент получает однотипные вопросы и имеет равные условия по ограничению во времени, попыткам и т.д.;

- программа выдает полный отчет по каждому проведенному опросу, который преподаватель может просмотреть как сразу после окончания теста, так и в любое другое время.

Пакет АТР4 может быть использован для построения тестирующих программ не только по VHDL, но и по другим дисциплинам. В таком виде он был внедрен в учебный процесс 4-х ПТУЗов [4]. Он также используется на кафедре КСС ДонНТУ. Планируется использование пакета ATP 4 для проведения серии опросов студентов по VHDL в рамках читаемых на 3-5 курсах дисциплин, а также для проведения внутривузовских и всеукраинских олимпиад по VHDL [5].