ДонНТУ | Портал магистров ДонНТУ | RU | UA | EN

Масякин Евгений Анатольевич

Масякин Евгений Анатольевич

Факультет компьютерных наук и технологий (КНТ)

Кафедра компьютерной инженерии (КИ)

Специальность «Компьютерные системы и сети» (КС)

«Разработка и исследования методов и структур аппаратного генерирования аналоговых тестов на базе FPGA»

Научный руководитель: к.т.н., доцент кафедры КИ, Зинченко Юрий Евгеньевич

Автобиография | Реферат | Библиотека | Перечень ссылок | Отчет о поиске | Индивидуальный раздел

Разработка и исследования методов и структур аппаратного генерирования аналоговых тестов на базе FPGA

Актуальность и обоснование выбора темы

Современный мир сложно представить без электроники. Каждый день, час, минуту создаются новые устройства, приборы, системы, которые делают жизнь человека более комфортной, безопасной, позволяют ему открывать новые горизонты научных знаний. Садясь за руль современного автомобиля, человек взаимодействует с десятками и сотнями электронных систем, различного уровня сложности: от простейших датчиков уровня масла до автоматизированных систем паркования автомобиля. Цифроаналоговая техника, как правило, играет роль посредника между окружающей средой и цифровыми системами. Исключением является военно-промышленный комплекс, где широко используются подобные устройства ввиду их высокой надежности и долговечности сравнительно с исключительно цифровыми системами [1]. В свою очередь повсеместное использование техники диктует все более и более жесткие требования к ее надежности, тестируемости, что вызывает необходимость разработки новых структур и методов синтеза и генерации, в том числе и аналоговых, тестов.

Цели и задачи исследования

Целью работы является разработка и исследование высокоэффективных структур и методов аппаратного генерирования аналоговых тестов с использованием современных возможностей FPGA-технологий в области цифровой обработки сигналов.

Задачи, решаемые в ходе выполнения данной работы:

- анализ существующих методов и структур генерирования аналоговых тестов;

- разработка метода и структуры генерации аналоговых тестов на базе ЦОС и ПЛИС;

- разработка программно-аппаратных средств на базе ПЛИС;

- проведение эксперементальных исследований.

Предполагаемая научная новизна

Возможная научная новизна состоит в разработке методов и структур генерирования аналоговых тестов на базе ЦОС, которые дадут более эффективное решение этой проблемы при реализации с использованием ПЛИС. Планируется, что подобная структура позволит обеспечить высокою эффективность, компактность, а также низкую стоимость устройств генерирующих аналоговые тестовые последовательности.

Обзор существующих разработок

Главным инструментом инженера-диагноста на сегодняшний день является автоматизированная система диагностики (АСД). Их ведущими производителями стали такие компании как Teradyne, Agilent, World Test Systems, DMT и другие. Однако, подавляющее большинство подобных систем предназначены для тестирования цифровых устройств, и не позволяют в полной мере автоматизировать процесс построения теста для аналогово-цифровых схем. В свою очередь построение функциональных аналоговых тестов требует высокой производительности, скорости генератора аналоговой тестовой последовательности. [2]

Уровни представления аналогово-цифровых схем при генерирования тестов.

По способу представления АЦ-устройства рассматривают:

- Структурный уровень — представление АЦ-устройства совокупностью компонент и связей между ними;

- Поведенческий или функциональный уровень — представление АЦ-устройства вход-выходной зависимостью: системой дифференциальных уравнений, графом, алгоритмом и т.д.

По степени детализации различают:

- транзисторный уровень — структурно схема представляется с помощью списка компонентов и списка соединений между ними, которые дополняются детальными моделями компонентов. Поведенческое представление схемы на этом уровне описывается системой нелинейных дифференциальных уравнений в частных производных;

- структурно-функциональный уровень — структурным представлением схемы на этом уровне является сигнальный ориентированный граф (СОГ), который графически отображает идеализированную систему уравнений. В свою очередь поведенческое представление на этом уровне описывается передаточной функцией схемы.

Выделяют структурные и функциональные аналоговые тесты. Основная разница между ними состоит в происхождении неисправностей и процедуре моделирования. Функциональное тестирование часто предполагает, что неисправны компоненты и при этом генерируется список неисправностей, который включает катастрофические и параметрические неисправности. Структурное тестирование использует статистику производственных дефектов. [2]

Аналоговые схемы имеют сложные зависимости между входными и выходными сигналами. Многие аналоговые схемы являются нелинейными системами (например, МОП-транзистор, используемый как усилитель). Значения параметров схемы изменяются в широких пределах даже в исправных схемах. Детерминистические модели не эффективны для аналоговых схем, поэтому сигналы определяются номинальными значениями вместе с приемлемыми диапазонами их изменений, которые определяются путем моделирования процесса измерения погрешностей и колебания процесса производства ИС. Статистическое распределение аналоговых неисправностей обычно не известно с достаточной точностью, чтобы безошибочно предсказать покрытие неисправностей тестовой последовательностью. Некоторые отчеты свидетельствуют о том, что аналоговые схемы с катастрофическими неисправностями не обнаруживаются стандартными производственными статистическими тестами, что в свою очередь ставит проблему создания эффективной системы генерирования функциональных аналоговых тестов. [2]

Использование DSP-процессоров в современных автоматизированных системах диагностики

В настоящее время практически все аналоговые схемы тестируются с использованием автоматизированных систем диагностики (АСД), построенных на базе DSP-процессоров. Такие АСД вместо использования реальных аналоговых измерительных инструментов(осциллограф, генератор аналоговых сигналов, мультиметр), выполняют их эмуляцию на основе быстрого преобразования Фурье (БПФ) и дискретного преобразования Фурье (ДПФ), для того чтобы уменьшить ошибку измерения и устранить нежелательное время установления сигнала при тестировании.

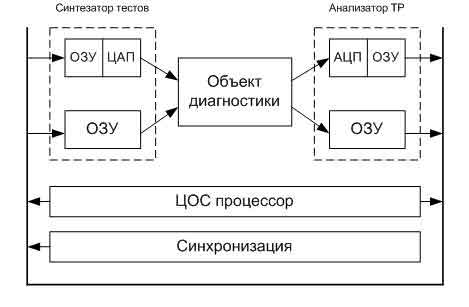

На рисунке 1 представлена традиционная аналоговая АСД. При использовании подобных систем процесс построения и применения функциональных аналоговых тестов с высоким уровнем покрытия неисправностей может занять значительное время даже для небольшой схемы. Низкий уровень автоматизации этого процесса в свою очередь ставит проблему дороговизны тестирования АЦ-устройств. [2]

На рисунке 2 представлена АСД на базе DSP-процессора, которая имеет соответствующую синхронизацию, и состоит из АЦП, ЦАП, памяти для хранения воздействий и реакций, DSP-процессора, который управляется на программном уровне.

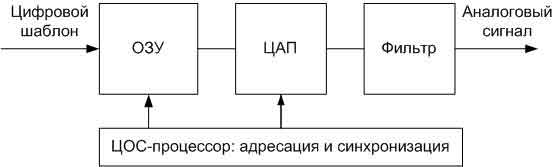

DSP может эмулировать широкий набор измерительных инструментов. Инструментами теперь являются подпрограммы, которые обрабатывают вектора численных значений. Вектор может представлять собой набор выборок сигнала, частотный спектр и т.д. Специалист по тестированию создает набор векторов в виде тестовых сигналов. Генератор сигналов подает эти вектора на ЦАП, выход которого соединен с восстанавливающим фильтром для получения непрерывного сигнала с ограниченной полосой пропускания. Полученный сигнал подается на испытываемое устройство, с которого снимаются реакции. [2]

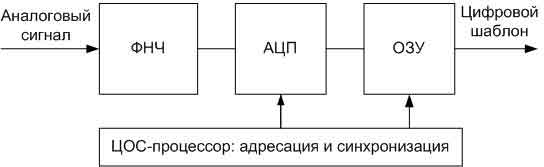

Дискретизатор аналоговых сигналов выполняет оцифровку снятых реакций с использованием высокоскоростного АЦП и сохраняет выборки в ОЗУ. Когда в качестве испытываемого устройства выступает аналогово-цифровая схема, сигналы с выходов цифровой части записываются во входную память, а тесты для цифровой части подаются на объект диагностики (ОД) из выходной памяти. [2]

На рисунке 3 изображен процесс синтеза аналогового сигнала, а на рисунке 4 процесс оцифровки.

Преимущества АСД на базе DSP-ядер

- Точность. АСД на базе DSP практически всегда обладают большей точностью, чем аналоговые инструменты, так как ошибка в наборе выборок сигнала значительно меньше после цифровой обработки, чем ошибка индивидуальной выборки. Наводки, шум и отклонения сигналов значительно сокращаются в DSP-тестерах, так как аналоговый сигнал оцифровывается на самой ранней стадии. Старение компонентов тестера и температурные эффекты вызывают значительно меньше проблем, так как цифровые компоненты лучше сохраняют свои характеристики, чем аналоговые.

- Скорость. DSP тестер может получить набор выборок от ОД за один период выборки, а далее используя ДПФ и БПФ выполнить над ним различные измерения путем эмуляции инструментов. Для выполнения кратных измерений DSP тестер значительно более эффективен, чем аналоговый, котором надо выполнять кратные измерения. Также в DSP тестере отсутствуют временные расходы на установление сигнала в фильтре, которые присутствуют в аналоговом тестере.

- Простота использования. Так как тестер цифровой, то легко повторять тестирование, выполнять настройку и сохранять выполненные настройки.

- Больше измерительной информации. DSP тестер предоставляет дополнительную информацию вместе с измеряемым параметром, например, пиковый детектор сообщает не только о значении пика, но и про расположение пика во времени.

- Размер и мощность. АСД общего назначения на базе DSP меньше, дешевле и требует меньшей мощности, чем соответствующая аналоговая АСД. [2]

Недостатки АСД на базе DSP-ядер

- Они дороги, хотя цена снижается благодаря использованию СБИС. Разрядность, необходимая для достижения приемлемой точности, и требования по полосе пропускания делают DSP дорогими.

- Когда необходимо выполнять только одно измерение, чисто аналоговые тестеры дешевле. DSP обладают преимуществом только при кратных измерениях.

- Гибкость инструментария является проблемой для неопытного оператора, так как необходимо знать теорию их использования.

- Специалист по тестированию должен знать физические и математические принципы, которые лежат за каждым тестом и источником ошибок. [2]

Преимущества использования ПЛИС для реализации DSP-ориентированных устройств

При разработке систем цифровой обработки сигналов (Digital System Processing, DSP) традиционным является подход, при котором используются DSP-процессоры общего назначения, а требуемые специфические алгоритмы обработки реализуются программно (в основном на языке С). Однако в последнее время все чаще можно наблюдать применение аппаратных методов, основанных на использовании программируемых логических интегральных схем (ПЛИС) с FPGA-архитектурой в качестве препроцессоров и сопроцессоров. Такой подход позволяет получить существенный прирост производительности, снизить стоимость и потребляемую мощность системы. Однако его повсеместному распространению препятствует то, что разработчики DSP-систем не всегда имеют опыт проектирования на базе FPGA. [7]

Архитектура FPGA обладает большой гибкостью, на ее базе можно реализовывать распараллеливание операций, что позволяет существенно повысить производительность всей DSP-системы. Наиболее типичные примеры такого использования FPGA – реализация быстрого преобразования Фурье, цифрового преобразования с понижением частоты, блоков прямого исправления ошибок.

Микросхемы семейств FPGA Virtex-4 и Virtex-5 фирмы Xilinx включают до 512 параллельных умножителей, работающих на частоте свыше 500 МГц. При построении DSP-системы операции, требующие высокоскоростной обработки данных в параллельном режиме, реализуются на базе FPGA, а операции высокоскоростной последовательной обработки – с помощью DSP-процессоров. Такое распределение ресурсов системы позволяет добиться оптимального соотношения цена-качество и снизить энергопотребление. [7]

Дополнительные возможности для распараллеливания операций обработки сигнала, оптимального распределения функций в системе с сопроцессором на базе FPGA обеспечивает наличие встроенных в FPGA процессоров. Микропроцессорное ядро MicroBlaze (soft processor, по терминологии Xilinx) предусматривает возможность реализации его на ПЛИС различных серий и часто оказывается удобным для организации управления системой. Более производительный процессор PowerPC реализован на кристалле в виде отдельного аппаратного блока.

Гибкость архитектуры ПЛИС FPGA позволяет организовать ускорение и распараллеливание операций различными способами. Например, блок на основе FPGA может быть непосредственно включен в тракт обработки данных DSP-системы. Другой возможный вариант – реализация аппаратного ускорителя на базе одного из встроенных процессоров. Распределение функций DSP-системы по имеющимся аппаратным ресурсам, при котором для системы в целом обеспечивается оптимальное соотношение цена-качество. [10]

Текущие и планируемые результаты

На данный момент были получены следующие результаты:

- выполнен обзор существующих методов генерирования аналоговых тестов;

- в качестве элементной базы для реализации программно-аппаратного комплекса генератора аналоговых тестовых воздействий был выбран отладочная FPGA-плата Xilinx Spartan 3AN;

- проведены исследования и разработано эксперементальное устройство генерирования аналоговых тестов.

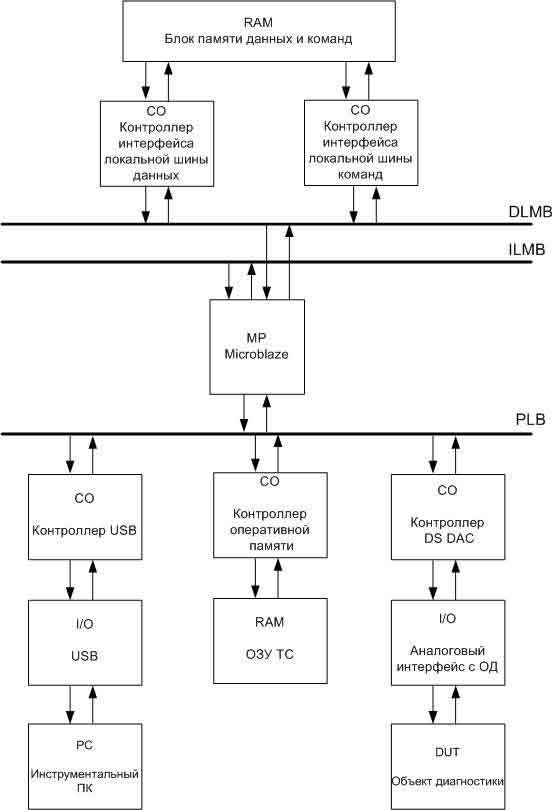

Структурная схема разработанного устройства приведена на рисунке 5.

Рисунок 5 — Структурная схема разработанного устройства

- МП Microblaze — soft-процессорное RISC ядро, разработанное компанией Xilinx для использования в FPGA. MicroBlaze реализуется с помощью стандартной логики и блоков памяти ПЛИС. В разработанной структуре данный элемент выполняет роль арбитра.

- Шина PLB — основная шина ввода-вывода. Обеспечивает взаимодействие между процессорным ядром и периферийными устройствами.

- iLMB, dLMB — локальная шина данных и локальная шина команд используется для доступа к внутренней памяти BRAM. Использование данных шин позволяет снизить нагрузку на другие шины.

- Интерфейс USB выбран по причине его распространенности, миниатюрности и доступности. Практически все современные персональные компьютеры, оснащены этим интерфейсом.

- Контроллер оперативной памяти — предназначен для организации работы с внешней RAM.

- Внешняя RAM-память используется для хранения тестовых векторов и тестовых реакций.

- PC — клиентская программа установленная на нём служит для задания параметров диагностики и отображения результатов.

Апробация

Промежуточные результаты работы докладывались на V юбилейной международной научно-технической конференции студентов, аспирантов и молодых ученых «Информатика и компьютерные технологии» 24-26 ноября 2009 г.

Выводы

Таким образом, существующие системы автоматического генерирования аналоговых тестов не всегда являются эффективными, а полноценных автоматизированных систем диагностики для аналогово-цифровых плат еще не создано, поэтому задача разработки методов автоматического генерирования аналоговых тестов является актуальной.

В дальнейшем будут разработаны методы и структура на базе ЦОС, которая даст более эффективное решение проблемы генерирования аналоговых тестов на ПЛИС.

Важное замечание

При написании данного реферата магистерская работа еще не завершена. Окончательное завершение: декабрь 2010 г. Полный текст работы и материалы по теме могут быть получены у автора или его руководителя после указанной даты.Список использованной литературы

- Давыдов П.С. Техническая диагностика радиоэлектронных устройств и систем / Давыдов П.С. // М.: Радио и связь, 1988. — 256 с.

- Agrawal V.D Essentials of electronic testing for digital, memory and mixed-signal VLSI circuits / Agrawal V.D, Bushnell M. L. // Boston: Kluwer Academic Publishers, — 2000, 650 p

- Bapiraju Vinnakota. Analog and mixed-signal test / Bapiraju Vinnakota // Prentice Hall PTR, 1998. — 261p.

- Prithviraj Kabisatpathy Fault Diagnosis of Analog Integrated Circuits / Prithviraj Kabisatpathy, Alok Barua, Satyabroto Sinha // Springer, 2005.

- A. Birolini, Quality Reliability of Technical Systems / A. Birolini // Springer-Verlag, Berlin, 1994.

- F.J. Langley, Printed Circuits Handbook / F.J. Langley // McGraw-Hill Publishing Company, Inc., New York, pp.21.1-21.26

- Перекрест А.А. Преимущества использования сопроцессоров на базе ПЛИС FPGA в системах цифровой обработки сигналов [Электронный ресурс] — Режим доступа: http://www.electronics.ru/issue/2006/6/18

- J. Galiay. Physical versus logical fault models MOS LSI circuits: Impact on their testability / J. Galiay //, IEEE Transactions on Computers, Vol. C-29, pp. 527-531, June 1980.

- Рувинова Э. Внутрисхемный контроль жив и будет жить // Рувинова Э./ Электроника: Наука, Технология, Бизнес, № 5 - 2001г.

- Ридико Л. DDS: прямой цифровой синтез частоты [Электронный ресурс] — Режим доступа: http://ru3ga.qrz.ru/UZLY/dds.htm