1. Введение

2. Общие понятия

3. Классификация оперативной памяти

3.1 Статические оперативные запоминающие устройства

3.2 Динамические оперативные запоминающие устройства

4. Организация основной памяти

4.1 Организация ОП на основе блочной схемы

4.2 Организация ОП на основе блочной схемы с чередованием адресов по циклической схеме

4.3 Организация ОП на основе блочной схемы с блочно-циклической схемой расслоения

Выводы

Литература

Важное замечание

1. Введение

Вычислительное направление применения компьютеров всегда оставалось основным двигателем прогресса

в компьютерных технологиях. В качестве основной характеристики

компьютеров используется такой показатель, как производительность — величина, показывающая,

какое количество арифметических операций он может выполнить за единицу времени.

Именно производительность с наибольшей очевидностью демонстрирует масштабы прогресса,

достигнутого в компьютерных технологиях.

В любой ВМ, вне зависимости от ее архитектуры, программы и данные хранятся в памяти.

Функции памяти обеспечиваются запоминающими устройствами (ЗУ), предназначенными для фиксации,

хранения и выдачи информации в процессе работы ВМ.

Тема анализа функционирования основной памяти с блочно-циклической схемой расслоения

является актуальной в наше время, ведь блочное построение памяти обладает такими важными

достоинствами, как сокращение времени доступа к информации и податливость к наращиванию емкости.

Это возможно благодаря потенциальному параллелизму,

присущему блочной организации. Большей скорости доступа можно достичь за счет одновременного доступа

ко многим банкам памяти.

Цель работы заключается в анализе функционирования основной памяти с блочно-циклической схемой расслоения.

Можно выделить следующие задачи магистерской работы:

- Обзор методов анализа функционирования основной памяти

- Построение и реализация марковских моделей основной памяти с блочно-циклической схемой расслоения

- Проведение анализа основной памяти на основе блочной схемы

- Анализ основной памяти с чередованием адресов по циклической схеме

- Анализ основной памяти с блочно-циклической схемой расслоения

Планируемые практические результаты заключаются в выработке рекомендаций по организации

объемов банков и блоков в зависисмости от критериев надежности или скорости.

Научная новизна заключается разработке и реализации марковских моделей основной памяти

с блочно-циклической схемой расслоения.

2. Общие понятия

Основная память (ОП) — это единственный вид памяти, к которой может непосредственно

обращаться ЦП (за исключением регистров центрального процессора). После того, как информация,

хранящаяся на внешних ЗУ, будет переписана в основную память, она становится доступной процессору.

ОП состоит из запоминающих устройств с произвольным доступом. Такие запоминающие устройства

организуются как массив ячеек. Каждая ячейка имеет уникальный адрес и содержит фиксированное число запоминающих элементов. Уникальный адрес позволяет различать ячейки при обращении к ним для выполнения операций считывания и записи.

Обращение к любой ячейке занимает одно и то же время и может выполняться в произвольной

последовательности («произвольный доступ»).

3. Классификация оперативной памяти

Основная память может включать в себя два типа устройств:

• постоянные запоминающие устройства (ПЗУ)

• оперативные запоминающие устройства (ОЗУ)

1) Постоянные запоминающие устройства (ПЗУ)

Меньшую долю основной памяти образуют ПЗУ (ROM — Read-Only Memory).

В отличие от ОЗУ, они обеспечивают считывание информации, но не допускают

ее изменения (существует ряд случаев, когда информация в ПЗУ может быть изменена,

но этот процесс отличается от считывания и требует значительно большего времени).

Микросхемы ПЗУ энергонезависимы.

2) Оперативные запоминающие устройства (ОЗУ)

Большую долю основной памяти образуют ОЗУ (RAM — Random Access Memory, память с

произвольным доступом) , называемые оперативными, потому что допускают однотипное,

производимое практически с одной и той же скоростью, выполнение операций записи и

считывания информации (при помощи электрических сигналов).

Но следует учитывать, что микросхема ОЗУ может использоваться только как временная память,

потому что должна быть постоянно подключена к источнику питания.

Существует два основных типа памяти с произвольным доступом:

• статическая (SRAM — Static RAM)

• динамическая (DRAM — Dynamic RAM)

Рассмотрим их подробнее.

3.1 Статические оперативные запоминающие устройства

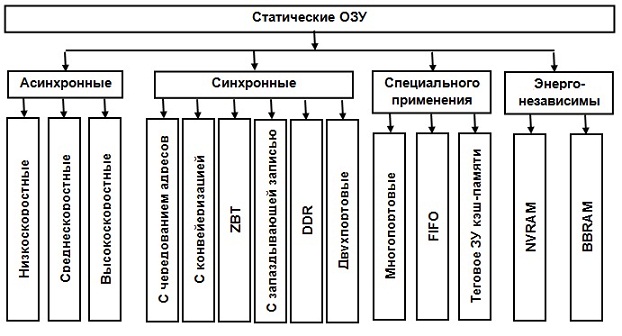

Статические ОЗУ — это наиболее быстрый, правда, и наиболее дорогостоящий вид оперативной памяти. Выделяется множество различных вариантов реализации SRAM, отличающихся по технологии, способам организации и сфере применения (рис. 1).

Рисунок 1 — Виды статических ОЗУ

Асинхронные статические ОЗУ.

Асинхронные статические ОЗУ применялись в кэш-памяти второго уровня в течение многих лет

(с момента появления микропроцессора i80386). Для таких ИМС время доступа составляло 12-20 нс,

что не позволяло кэш-памяти второго уровня работать в темпе процессора.

Синхронные статические ОЗУ.

В рамках данной группы статических ОЗУ выделяют ИМС типа SSRAM и РВ SRAM (более совершенные).

По сравнению с асинхронными статическими ОЗУ, значительно лучшие показатели достигнуты в

синхронных SRAM (SSRAM). Все события в SSRAM происходят с поступлением внешних тактовых импульсов.

Отличительной особенностью SSRAM являются входные регистры, где фиксируется входная информация.

Последние модификации микропроцессоров Pentium, начиная с Pentium II,

оснащаются статической оперативной памятью с пакетным конвейерным доступом

(РВ SRAM — Pipelined Burst SRAM), взамен SSRAM. За счет внутренней конвейеризации в РВ SRAM ,

скорость обмена пакетами данных возрастает примерно вдвое. Память данного типа хорошо работает

при повышенных частотах системной шины. Время доступа к РВ SRAM составляет от 4,5 до 8 нс.

3.2 Динамические оперативные запоминающие устройства

Именно DRAM используется в качестве основной памяти ВМ, следовательно, динамической памяти в

вычислительной машине значительно больше, чем статической.

Как и SRAM, динамическая память состоит из ядра (массива ЗЭ) и интерфейсной логики

(буферных регистров, усилителей чтения данных, схемы регенерации и др.). Количество видов

DRAM уже превысило два десятка, однако ядро у них организовано практически одинаково, главные

различия связаны с интерфейсной логикой (также, они обусловлены и областью применения микросхем).

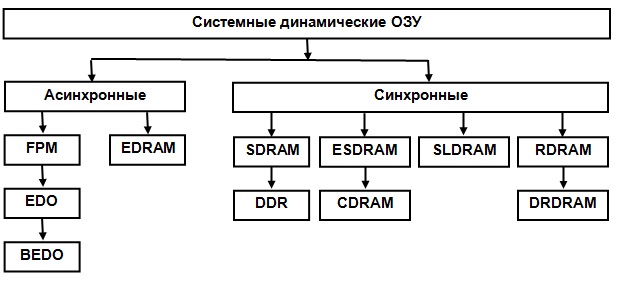

Классификация микросхем динамической памяти показана на рис. 2.

Рисунок 2 — Классификация динамических ОЗУ. Микросхемы для основной памяти

4. Организация основной памяти

Для реализации основной памяти используют объединение нескольких интегральных микросхем (ИМС, ICs — Integrated Circuits).

Причиной объединения является большая ёмкость ОП и превышение разрядности слов ВМ

разрядности ячеек микросхемы ЗУ.

Увеличение разрядности ЗУ реализуется за счет объединения адресных входов объединяемых ИМС ЗУ.

Информационные входы и выходы микросхем являются входами и выходами модуля ЗУ увеличенной разрядности (рис. 3).

Совокупность микросхем называют модулем памяти. Один или несколько модулей образуют банк памяти.

Рисунок 3 — Увеличение разрядности памяти (анимация: объем — 40.8 КБайт, количество кадров — 6, количество повторов — 7, размер — 559 х 280)

Для получения требуемой емкости ЗУ необходимо определенным образом объединить несколько банков

памяти меньшей емкости. В общем случае основная память ВМ практически всегда имеет блочную структуру

(содержит несколько банков).

При использовании блочной памяти, которая состоит из В банков, адрес ячейки А преобразуется в

пару (b, w), где b — номер банка, w — адрес ячейки внутри банка.

Схемы распределения разрядов адреса А между b и w:

• блочная (номер банка b определяет старшие разряды адреса);

• циклическая (b=A mod В; w = A div В);

• блочно-циклическая (комбинация двух предыдущих схем).

4.1 Организация ОП на основе блочной схемы

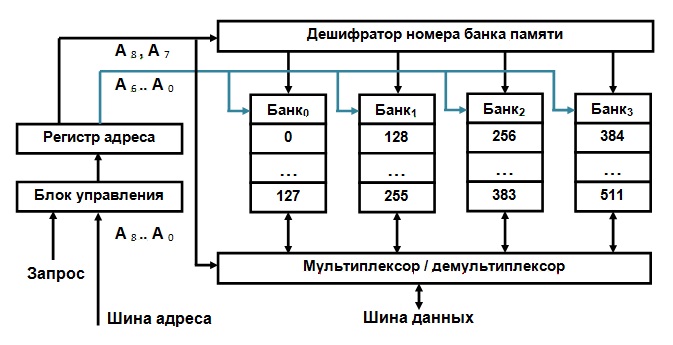

Рассмотрение основных структур блочной ОП проведем на примере памяти емкостью 512 слов, построенной из четырех банков по 128 слов в каждом. Структура памяти, организованная в соответствии с рассматриваемой структурой, показана на рис. 4.

Рисунок 4 — Структура основной памяти на основе блочной схемы

Адресное пространство памяти разбивается на группы адресов (последовательных),

каждая такая группа обеспечивается отдельным банком памяти.

Для обращения к ОП используется 9-разрядный адрес. Семь младших разрядов (А6-А0)

поступают параллельно на все банки памяти и выбирают в каждом из них одну ячейку.

Два старших разряда адреса (А8, А7) содержат номер банка.

Выбор банка обеспечивается либо путем мультиплексирования информации, либо с

помощью дешифратора номера банка.

В функциональном отношении, такая ОП может рассматриваться как единое ЗУ,

емкость которого равна суммарной емкости составляющих, а быстродействие — быстродействию отдельного банка [1].

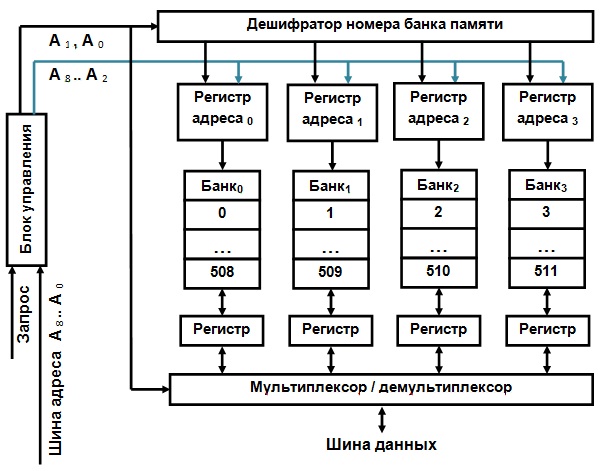

4.2 Организация ОП на основе блочной схемы с чередованием адресов по циклической схеме

К достоинствам блочной памяти можно отнести наращивание ёмкости и сокращение времени

доступа к информации благодаря потенциальному параллелизму.

Скорость доступа увеличивается за счет одновременного доступа ко многим банкам памяти.

Одна из используемых для этого методик называется расслоением памяти. В ее основе лежит так

называемое чередование адресов (address interleaving), заключающееся в изменении системы

распределения адресов между банками памяти.

Чередование адресов обеспечивается за счет циклического разбиения адреса.

В приведенном примере (рис. 5) для выбора банка используются два младших разряда адреса

(A1, A0), а для выбора ячейки в банке — 7 старших разрядов (A8-A2).

Рисунок 5 — Блочная память с чередованием адресов по циклической схеме

Последовательный доступ в память обычно производится к ячейкам, имеющим смежные адреса.

Можно достичь в В (В — количество банков) раз большей скорости, обмена с, памятью в целом,

чем у отдельного ее банка, если обеспечить одновременное последовательное обращение к

данным в каждом из банков.

Если запросы к одному и тому же банку следуют друг за другом, каждый следующий запрос

должен ожидать завершения обслуживания предыдущего. Такая ситуация называется конфликтом по доступу.

При частом возникновении конфликтов по доступу метод становится неэффективным

4.3 Организация ОП на основе блочной схемы с блочно-циклической схемой расслоения

В блочно-циклической схеме расслоения памяти каждый банк состоит из нескольких модулей, адресуемых по круговой схеме. Адреса между банками распределены по блочной схеме. Адрес ячейки разбит на три части. Старшие биты определяют номер банка, следующая группа разрядов адреса указывает на ячейку в модуле, а младшие биты адреса выбирают модуль в банке (рис. 6).

Рисунок 6 — Блочно-циклическая схема расслоения памяти

Выводы

Приведенные способы расслоения памяти хорошо работают при решении одной задачи, для которой

характерно свойство локальности. В многопроцессорных системах с общей памятью, где запросы на

доступ к памяти достаточно независимы, рассматривается развитие идеи расслоения памяти. Для этого

в систему включают несколько контроллеров памяти, что позволяет отдельным банкам работать

абсолютно автономно. Эффективность данного приема зависит от частоты независимых обращений

к разным банкам.

Чем больше количество банков, тем меньше вероятность последовательных обращений к

одному и тому же банку памяти.

Литература

- Цилькер Б.Я. Организация ЭВМ и систем [Текст]: — М : ПИТЕР, 2004. — 668 с.

- Столингс У. Структурная организация и архитектура компьютерных систем [Текст]: — М. : Вильямс, 2002. — 893 с.

- Оперативная память [Электронный ресурс]. — Режим доступа: http://ru.wikipedia.org/wiki/Оперативная память

- Шпаковский Г.И. Организация параллельных ЭВМ и суперскалярных процессоров [Текст]: — Мн.: Белгосуниверситет, 1996. — 296 с.: ил.

- Халабия Р.Ф. Организация вычислительных систем и сетей [Текст]: — М. : МГАПИ-Москва, 2000. — 141 с.

- Фельдман Л.П., Михайлова Т.В. Вероятностная модель блочной памяти // Искусственный интеллект.— Донецк: ІПШІ МОН і НАН України “Наука і освіта”, 2010.

- Мюллер C. Модернизация и ремонт ПК, 18-е издание [Текст]: пер. с англ. — : ООО «И.Д. Вильямс», 2009. — 1280 с.

- Алиев Т.И. Основы моделирования дискретных систем [Текст]: — СПб. : СПбГУ ИТМО, 2009. — 363 с.

- Букатов А. А., Дацюк В. Н., Жегуло А. И. Программирование многопроцессорных вычислительных систем [Текст]: — Ростов-на-Дону : ООО «ЦВВР», 2003. — 208 с.

- Архитектура компьютера [Электронный ресурс]. — Режим доступа: http://itblock.ru/

Важное замечание

На момент написания данного реферата магистерская работа еще является не завершенной. Предполагаемая дата завершения: 1 декабря 2011 г., ввиду чего полный текст работы, а также материалы по теме могут быть получены у автора или его руководителя только после указанной даты.