Реферат за темою випускної роботи

Зміст

- Вступ

- 1. Актуальність теми

- 2. Мета і задачі дослідження та заплановані результати

- 3. Огляд досліджень та розробок

- 3.1 Огляд міжнародних джерел

- 3.2 Огляд національних джерел

- 3.3 Огляд локальних джерел

- 4. Розробка методології верифікації СнК на базі FPGA

- Висновки

- Перелік посилань

Вступ

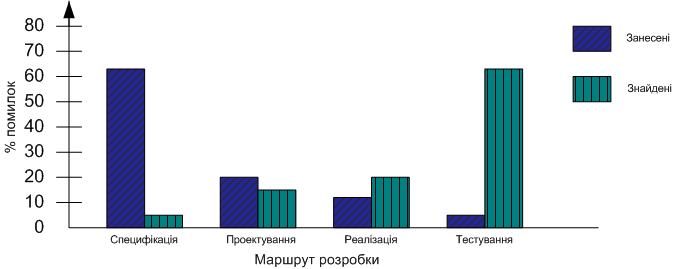

Процес проектування цифрових пристроїв нерозривно пов'язаний з поняттям верифікації. Поняття верифікації в загальному випадку має на увазі під собою перевірку збігу результатів роботи пристрою, що розробляється, і вимог, які до них пред'являються. Щоб представити усю важливість верифікації досить сказати, що вона займає більше 60% від загального часу проектування [1] і залучає більшу частину персоналу, що працює над проектом. Більшість існуючих методик проектування цифрових пристроїв передбачають верифікацію лише на етапі відлагодження готового виробу. При такому підході навіть невелика помилка, занесена на ранній стадії, надалі може привести до серйозніших наслідків, що зазвичай виражається в додаткових матеріальних і часових витратах. При збереженні існуючих методик проектування до 70% помилок виникають на початкових етапах проектування і тільки на етапі відлагодження готового приладу вдається усунути близько 70% раніше внесених помилок [2]. Дана ситуація зображена на рис. 1.

Рисунок 1 — Розподіл помилок при даній методиці проектування

Ця ситуація до того ж посилюється тим, що технологічні можливості засобів проектування і верифікації помітно відстають від рівня складності сучасних цифрових пристроїв. Динаміка розвитку технологічних можливостей по відношенню до можливостей засобів САПР і верифікації показана на рис. 2.

Рисунок 2 — Динаміка розвитку технологічних можливостей

(анімація: 6 кадрів, 5 циклів повторення, 140 кілобайт)

Як видно з малюнка, можливості засобів верифікації помітно відстають від засобів проектування ЦП і ще більше — від поточного рівня складності проектів. За останній час ситуація стала трохи змінюватися у бік створення і освоєння нових методологій верифікації проектів цифрових пристроїв, а також їх застосування на усіх етапах проектування.

1. Актуальність теми

Актуальність проблем верифікації проектів цифрових пристроїв підтверджується як зростаючою кількістю різних FPGA-систем, що вбудовуються, так і періодичністю виходу публікацій в зарубіжних і вітчизняних виданнях, присвячених проблемам верифікації цифрових пристроїв. Остання оглядова публікація, присвячена методам верифікації, датована лютим 2012 року [3].

Магістерська робота присвячена актуальній проблемі розробки підходу до верифікації FPGA-проектів типу СнК, що занурені в FPGA, спрямованого на зменшення загального часу розробки проектів цифрових пристроїв. В якості цільового базису використовується налагоджувальні FPGA плати фірми Xilinx, що поєднують достатню функціональність, здатність програмування, здатність реконфігурації і доступність широкому споживачеві, а інструментальними засобами дослідження і проектування виступають САПР Xilinx ISE, Xilinx EDK, Xilinx ChipScope Pro, Aldec Active-HDL.

2. Мета і задачі дослідження та заплановані результати

Метою досліджень є розробка методології верифікації проектів цифрових пристроїв типу система-на-кристалі (СнК), що занурені в кристал FPGA, спрямованої на зменшення загального часу верифікації/проектування.

Основні завдання дослідження:

- Аналіз існуючих методик і засобів верифікації проектів цифрових пристроїв.

- Оцінка можливості застосування існуючих методик верифікації цифрових пристроїв для верифікації СнК на базі FPGA.

- Оцінка можливостей спільного використання існуючих методик для досягнення більшої ефективності верифікації.

- Дослідження можливостей максимізації покриття верифікації.

- Аналіз причин можливої надмірності верифікації.

- Оцінка можливостей застосування базових алгоритмів зондової діагностики для верифікації FPGA-проектів на апаратному рівні.

Об'єкт дослідження: верифікація FPGA-проектів.

Предмет дослідження: об'єднання існуючих методик верифікації проектів цифрових пристроїв і їх адаптація для виконання верифікації FPGA-проектів типу СнК.

У рамках магістерської роботи планується отримання актуальних наукових результатів по наступних напрямках:

- Розробка методології верифікації проектів цифрових проектів типу система-на-кристалі (СнК), що занурені в кристал FPGA, спрямованої на зменшення загального часу верифікації/проектування.

- Визначення можливостей спільного використання існуючих методик верифікації на різних етапах проектування цифрових пристроїв на базі FPGA.

- Адаптація базових алгоритмів зондової діагностики для верифікації FPGA-проектів на апаратному рівні.

Для експериментальної оцінки отриманих теоретичних результатів і формування фундаменту подальших досліджень, в якості практичних результатів планується застосування розробленої методології для проведення повного маршруту проектування/верифікації СнК, що призначена для занурення в кристал FPGA.

3. Огляд досліджень та розробокк

Проблеми верифікації проектів цифрових пристроїв є найважливішими при проектуванні. Останнім часом проводиться все більше досліджень в цьому напрямі як зарубіжними, так і вітчизняними фахівцями. Цим питанням присвячений ряд робіт, здебільшого зарубіжних авторів.

3.1 Огляд міжнародних джерел

На міжнародній арені першість в питаннях верифікації проектів цифрових пристроїв належить таким компаніям як Mentor Graphics, Cadence и Accellera.

Компанія Mentor Graphics просуває три основні методології функціональної верифікації: верифікація, що побудована на використанні ассертів (ABV — Assertion Based Verification), UMV/OVM методології і верифікація, що ведеться процесором (Processor-Driven Verification) [4].

Верифікація, що побудована на використанні ассертів — це методологія, при якій проектувальники використовують ассерти для контролю конкретної властивості проекту та, або за допомогою моделювання, формальної верифікації, або емуляції цих ассертів, переконуються, що проект правильно реалізує цю властивість [5].

UVM (Universal Verification Methodology) є першим промисловим стандартом методології верифікації, що надає відкриту і єдину бібліотеку класів і методологію для використання сумісних ядер верифікації (Verification IP) і testbench [6]. UVM є розробкою компанії Accellera, що базується на більш ранній методології OVM (Open Verification Methodology), над якою спільно працювали фахівці компаній Mentor Graphics і Cadence. Ця методологія є найбільш прогресивною, поточний стан досліджень в цьому напрямі відображений на порталі Verification Academy [7].

Сучасні методи застосування тестових векторів з HDL testbench тільки починають імітувати поведінку процесорної шини. Введення testbench, що ведуться процесором, в існуючу методологію верифікації робить можливою верифікацію в реальному часі і екстенсивне повторне використання програмного забезпечення testbench упродовж усього проекту. Одним з обмежень для ефективного використання тестів, що ведуться процесором, була складність відлагодження програмного забезпечення в процесорі, який запускається в логічному симуляторі [8].

Питання тестування вбудованих систем, що базуються на ядрах, висвітлені в статті Е. Зориана [9]. Тестування СнК, що базується на використанні мікропроцесора, розглянуто в статті С. А. Папахристова, Ф. Мартіна і М. Нурані [10].

Написання testbench для функціональної верифікації HDL моделей розглядається в книзі Б. Яніка [11]. Засоби функціональної верифікації детально розглядаються в статтях А. Л. Лохова [12-15]. Огляд маршруту проектування і верифікації компанії Mentor Graphics, а також засоби для формальної верифікації розглядаються в статтях А. Рабоволюка [16-17].

Проектування і верифікація проектів цифрових пристроїв на основі ПЛІС фірми Xilinx розглядається в статтях В. Зотова [18‒20].

3.2 Огляд національних джерел

На національному рівні питання проектування і верифікації цифрових систем-на-кристалі активно досліджуються в Харківському національному університеті радіоелектроніки. Питання тестування і верифікації цифрових систем висвітлені в статтях В.І. Хаханова, В.В. Єлісєєва, В.І. Обризана, Ваде Грибі, Хасана Ктеймана [21-22].

Детально проблеми синтезу, аналізу і верифікації цифрових систем із застосуванням мов опису апаратури Verilog і System Verilog розглянуті в книзі В. І. Хаханова [23].

3.3 Огляд локальних джерел

У Донецькому національному технічному університеті питання верифікації проектів цифрових пристроїв досліджуються на кафедрі комп'ютерної інженерії в лабораторії FPGA і HDL технології проектування і діагностики КС

під керівництвом Ю. Є. Зінченко. Методи тестування і верифікації FPGA-проектів із застосуванням технології Boundary Scan досліджуються в магістерських роботах Є. О. Астахова [24], Д. О. Ковтуна [25], О. С. Мірошникова [26]. Питання контролю і тестування цифрових пристроїв розглядаються в магістерських роботах С. В. Свистунова [27], О. О. Мядельца [28], О. С. Ритова [29], Ю. В. Блинова [30].

4. Розробка методології верифікації СнК на базі FPGA

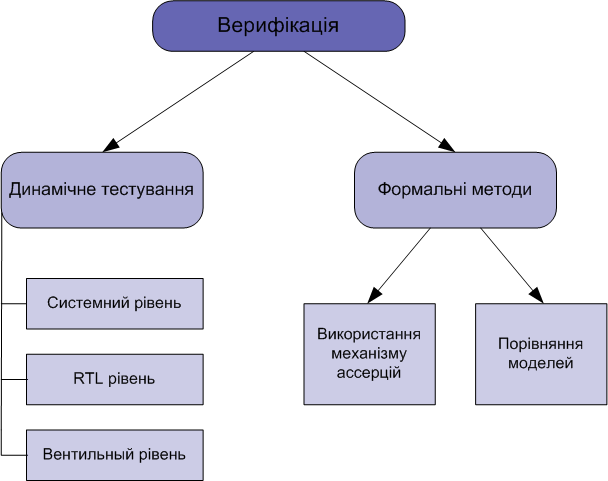

Усю безліч методів організації верифікації можна розділити на дві великі категорії — динамічні методи і формальні (статичні). При розгляді методів найважливішими критеріями успішності верифікації являються повнота покриття проекту тестами і витрачений на верифікацію час. Класифікація основних методів верифікації приведена на рис. 3.

Рисунок 3 — Основні методи верифікації

До динамічних методів відносяться симуляційні експерименти над проектом, що розробляється, на різних етапах проектування — системний рівень, рівень RTL, топологічний рівень. У кожному з випадків на вхід системи подається набір тестових стимулів у вигляді testbench або waveform і звіряються отримані результати з очікуваними. При цьому об'єкт, що тестується, може бути як фізичним зразком (прототипом), так і моделлю. При такому підході до верифікації може контролюватися окремо як функціональність моделі (при цьому тимчасові показники опускаються або приймаються рівними нулю), так і її відповідність часовим характеристикам (упор на задоволення часовим показникам), а також ці чинники в сукупності. Перевагою цього методу є теоретична можливість повного покриття верифікації. На практиці ж часто трапляється так, що пристрій, який тестується, представлено у вигляді чорного ящика

і неможливо згенерувати стимули так, щоб повністю перевірити функціональність, або кількість тестових векторів для повного покриття може виявитися занадто великою і привести до великих часових витрат. Ще одним недоліком цього підходу є можливість ситуації, коли неможливо спостерігати джерело виникнення помилки у внутрішніх ланцюгах. Такі помилки, як правило, проявляють себе на пізніших етапах проектування, що призводить до додаткових часових і матеріальних витрат.

До формальних методів верифікації можна віднести впровадження специфікацій проекту в його модель, а також докази еквівалентності різних моделей.

Методи впровадження специфікацій проекту в його модель побудовані на різних властивостях проекту, які контролюються шляхом тверджень усередині самого проекту. Таким чином, модель проекту міститиме як опис роботи, так і опис контролю своїх властивостей. При створенні моделі застосовуються методи строгого математичного доказу відповідності володіння моделлю запланованими властивостями майбутньої системи [2]. Ці методи отримали назву методів ассертування (тверджень). Простою реалізацією такого методу є включення в код ассертів, що контролюють певні властивості проекту. Це досягається шляхом застосування як простих HDL операторів типу assert, так і використанням спеціальних мов опису тверджень — PSL (Property Specification Language), OVA (OpenVera Assertions) для опису складних поведінкових алгоритмів. Розвиток цієї методики привів до появи цілої методології, побудованої на застосуванні ассертування — ABD (Assertion-Based Design), в основі якої лежить ідея застосування цілих модулів ассертування, наприклад, з бібліотеки OVL (Open Verification Library) фірми Accellera. Найважливішим моментом у використанні ассертів є правильний вибір властивостей об'єкту, що контролюється, від якого залежить повнота покриття верифікації. При правильному виборі властивостей повнота покриття може досягати максимуму.

Метод доказу еквівалентності моделей побудований на порівнянні роботи моделі, що проектується, з іншою моделлю. При цьому виникає проблема визначення правильності роботи іншої моделі, яка береться в якості еталонної. Прикладом використання цього методу є порівняння на еквівалентність RTL- та gate- уявлень.

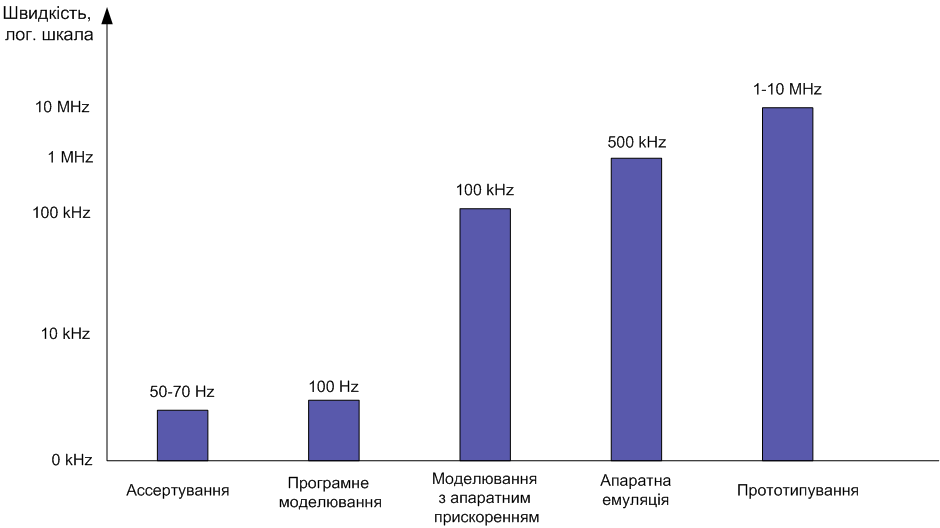

Перевагою застосування формальних методів є досить велика повнота покриття в порівнянні з динамічними методами за умови правильного і повного вибору властивостей, що контролюються, а також можливість перевірки контрольних точок системи. Недоліком цих методів є неможливість їх застосування на стадії апаратної реалізації, на відміну від динамічних, які припускають роботу з дослідним зразком проекту; також недоліком є складність САПР, що реалізовують методи формальної верифікації. Порівняльна характеристика швидкісних показників методів верифікації [31] приведена на рис. 4.

Рисунок 4 — Порівняльна характеристика швидкісних показників

Особливості проектування цифрових пристроїв на базі FPGA, зважаючи на автоматизацію етапів проектування в САПР, істотно знижують ціну помилки проектування. Проте важливим все ще залишається часовий чинник. Тому при проектуванні складних пристроїв, якими є СнК, необхідно враховувати важливість повнішого покриття верифікації на усіх етапах проектування із застосуванням існуючих методик і їх комбінацій. Це спричиняє за собою необхідність створення якісно нової методології верифікації СнК на базі FPGA, з урахуванням особливостей цільової платформи.

Розробка нової методології повинна вирішувати наступні проблеми:

- зменшення часу від початку проектування до виходу готового виробу на ринок;

- максимізація покриття верифікації проекту;

- виключення верифікаційної надмірності.

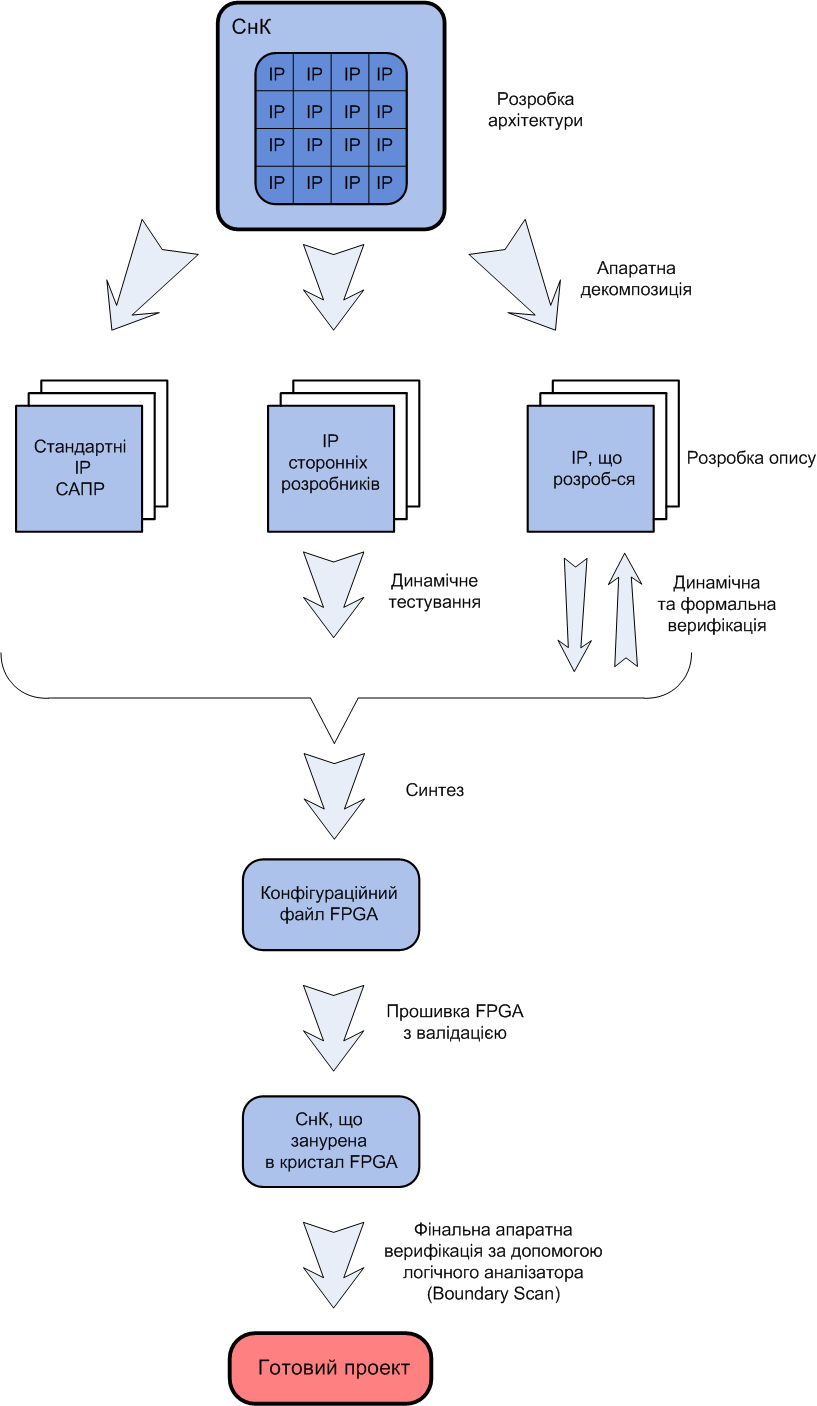

Маршрут проектування/верифікації СнК на базі FPGA наведено на рис. 5.

Рисунок 5 — Маршрут проектування/верифікації СнК на FPGA

Засоби, за рахунок яких планується рішення перерахованих проблем:

- декомпозиція СнК на складові IP-ядра, із застосуванням індивідуальних методик верифікації;

- правильний вибір методик верифікації та їх використання на всіх етапах проектування, на відміну від стандартного маршруту проектування FPGA-проектів на основі ПЛІС фірми Xilinx [19], де процедура верифікації має місце лише після етапу синтезу у вигляді функціонального моделювання пристрою без урахування верифікації вихідного опису;

- поєднання по можливості методик низхідної і наскрізної верифікації для забезпечення максимального покриття проекту;

- застосування технології граничного сканування для верифікації достовірності прошивки кристала, шляхом зворотного читання конфігураційних даних із запрограмованої ПЛІС і порівняння з вмістом відповідного файлу програмування, який вказаний для вибраного елементу ланцюжка периферійного сканування [20];

- застосування технології граничного сканування для динамічної верифікації проекту на апаратному рівні шляхом підключення відповідних ядер, наприклад, за допомогою утиліти ChipScope Pro із застосуванням стандартних алгоритмів зондової діагностики.

Висновки

Магістерська робота присвячена актуальному науковому завданню застосування існуючих методів верифікації цифрових пристроїв для верифікації СнК на FPGA.

У ході огляду існуючих методик проектування цифрових пристроїв було виявлено, що недостатність використання процедур верифікації на різних етапах проектування і використання верифікації лише на кінцевій стадії часто призводить до додаткових матеріальних і часових витрат, пов'язаних з поверненням на ранні стадії розробки для усунення виявлених помилок. При цьому навіть невелика невиявлена логічна помилка на ранній стадії проектування може привести до непрацездатності усього виробу після виготовлення дослідного зразка.

Для вивчення існуючих рішень по застосуванню методів верифікації на різних етапах проектування для скорочення загального часу проектування і виявлення помилок на ранніх стадіях розробки був проведений оглядовий аналіз найбільш типових методів верифікації, що використовуються нині. Були виявлені переваги і недоліки кожного з методів, а також сфери їх можливого застосування.

З урахуванням виконаного аналізу було прийнято рішення про створення якісно нової методології верифікації систем-на-кристалі на базі FPGA, з урахуванням особливостей цільової платформи, яка повинна вирішувати ряд поставлених проблем. Особливості цільової платформи хоч і мінімізують вартість помилки проектування, мінімізація термінів розробки все ще залишається актуальною проблемою. Нова методологія верифікації повинна будуватися на правильному виборі і використанні існуючих методів на кожній із стадій проектування індивідуально і забезпечувати належне покриття верифікації проекту при виключенні надмірності верифікації. Ключовим моментом тут повинно стати використання механізму граничного сканування, який би забезпечив доступ до внутрішніх сигналів проекту для їх контролю, що істотно розширить можливості динамічної верифікації і зведе нанівець деякі з її недоліків, що обмежують її застосування.

При написанні цього реферату магістерська робота ще не завершена. Остаточне завершення: грудень 2012 року. Повний текст роботи і матеріали по темі можуть бути отримані у автора або його керівника після вказаної дати. Поточний стан досліджень в ході написання магістерської роботи відображений на особистому сайті [32], який присвячений проблемам верифікації FPGA-проектів.

Перелік посилань

- Немудров В., Мартин Г. Системы-на-кристалле. Проектирование и развитие [текст] / В. Немудров, Г. Мартин — М.: Техносфера. — 2004. — 216 с.

- Грушвицкий Р., Михайлов М. Проектирование в условиях временных ограничений: верификация проектов (1 часть) [Электронный ресурс]. — Режим доступа: http://www.kit−e.ru/assets/files/pdf/2008_3_96.pdf.

- Verification Horizons. A publication of Mentor Graphics — volume 8, issue 1 [Электронный ресурс]. — Режим доступа: http://www.mentor.com/products/fv/verificationhorizons/.

- Methodologies of Functional Verification, Mentor Graphics [Электронный ресурс]. — Режим доступа: http://www.mentor.com/products/fv/methodologies/.

- Assertion-Based Verification, Mentor Graphics [Электронный ресурс]. — Режим доступа: http://www.mentor.com/products/fv/methodologies/abv/.

- UVM/OVM, Mentor Graphics [Электронный ресурс]. — Режим доступа: http://www.mentor.com/products/fv/methodologies/uvm−ovm/.

- Verification Academy - The Most Comprehensive Resource for Verification Training [Электронный ресурс]. — Режим доступа: http://verificationacademy.com/.

- Processor-Driven Verification, Mentor Graphics [Электронный ресурс]. — Режим доступа: http://www.mentor.com/products/fv/methodologies/pdv/.

- Zorian Y. Test Requeirements for Embedded Core-Based Systems and IEEE P1500 / Y. Zorian // In Proceedings IEEE International Test Conference (ITC). — Washington, DC. — November 1997. — IEEE Computer Society Press. — pp. 191-199.

- Papachristou C. A. Microprocessor based testing for core-based system on chip / C. A. Papachristou, F. Martin, M. Nourani // In Proceedings of the 36th ACM/IEEE conference on Design automation conference. — ACM Press. — 1999. — pp. 586-591.

- Janick B. Writing testbenches: functional verification of HDL models / B. Janick. — Boston. — Kluwer Academic Publishers. — 2001. — 354 pp.

- Лохов А. Л. Функциональная верификация СБИС / А.Л. Лохов // Электроника: Наука, Технология, Бизнес. — 2004. — № 1.

- Лохов А. Л. Современный функциональной уровень верификации СБИС / А. Л. Лохов // Труды конференции «Проблемы разработки перспективных микроэлектронных систем (МЭС - 2005)» — 2004.

- Лохов А. Л. Обзор средств функциональной верификации компании Mentor Graphics / А. Л. Лохов // Современная электроника №5. — 2005. — с. 50-54.

- Лохов А. Л. Современные методы функциональной верификации цифровых HDL-проектов: методология ABV, библиотеки OVL и QVL / А. Л. Лохов // Современная электроника №1. — 2010. — с. 56-59.

- Рабоволюк А. Обзор маршрута проектирования ПЛИС FPGA Advantage компании Mentor Graphics / А. Рабоволюк // Компоненты и технологии №7. — 2005.

- Рабоволюк А. Применение средств Mentor Graphics O-In и Mentor Graphics Questa для верификации проекта с использованием формальных методов / А. Рабоволюк // Современная электроника №6. — 2005. — с. 52-54.

- Зотов В. Средства внутрикристальной отладки цифровых устройств и встраиваемых микропроцессорных систем, разрабатываемых на базе ПЛИС с архитектурой FPGA фирмы Xilinx — ChipScope Pro / В. Зотов // Компоненты и технологии №10. — 2008. — с. 41-45.

- Зотов В. Практический курс сквозного проектирования цифровых устройств на основе ПЛИС фирмы Xilinx (Часть 2) / В. Зотов // Современная электроника №2. — 2007. — с. 72-77.

- Зотов В. Практический курс сквозного проектирования цифровых устройств на основе ПЛИС фирмы Xilinx (Часть 20) / В. Зотов // Современная электроника №2. — 2009. — с. 48-55.

- Хаханов В. И. Иерархическое тестирование программно-технических комплексов / В. И. Хаханов, В. В. Елисеев, В. И. Обризан, Ваде Гриби, Хасан Ктейман // АСУ и приборы автоматики № 1. — 2005. — с. 93-102.

- Хаханов В. И. Accept-метод верификации цифровых систем на основе стандарта IEEE 1500 SECT / В. И. Хаханов, В. В. Елисеев, В. И. Обризан, Ваде Гриби, Хасан Ктейман // АСУ и приборы автоматики № 3. — 2005. — с. 93-105.

- Хаханов В. И. Проектирование и верификация цифровых систем на кристаллах. Verilog & System Verilog / В. И. Хаханов, И. В. Хаханова, Е. И. Литвинова, О. А. Гузь. — Харьков: ХНУРЭ. — 2010. — 528 с.

- Астахов Е. А. Разработка и исследование метода верификации FPGA проектов по методологии ведомого зонда на базе технологии Boundary Scan [Электронный ресурс]. — Режим доступа: http://masters.donntu.ru/2009/fvti/astahov/diss/index.htm.

- Ковтун Д. О. Разработка и исследование методов тестирования FPGA-устройства с использованием технологии Boundary-Scan [Электронный ресурс]. — Режим доступа: http://masters.donntu.ru/2010/fknt/kovtun/index.htm.

- Мирошников А. С. Разработка алгоритмов тестирования FPGA-устройств по технологии периферийного сканирования [Электронный ресурс]. — Режим доступа: http://masters.donntu.ru/2002/fvti/miroshnikov/diss/index.htm.

- Свистунов С. В. Исследование и разработка на FPGA SPP-архитектуры поста контроля цифровых устройств [Электронный ресурс]. — Режим доступа: http://masters.donntu.ru/2008/fvti/svistunov/diss/index.html.

- Мяделец А. А. Разработка и исследование метода синтеза тестов для типовых элементов замены (ТЭЗ) [Электронный ресурс]. — Режим доступа: http://masters.donntu.ru/2006/fvti/myadelets/diss/index.htm.

- Ритов А. С. Розробка діагностичної моделі FPGA-пристроїв та синтез тестів на її базі [Электронный ресурс]. — Режим доступа: http://masters.donntu.ru/2002/fvti/rytov/dissert.htm.

- Блинов Ю. Е. Разработка и исследование методов и структур аппаратной генерации тестов и анализа тестовых реакций на базе FPGA [Электронный ресурс]. — Режим доступа: http://masters.donntu.ru/2010/fknt/blinov/index.htm.

- Chong-Min Kyung Current Status and Challenges of SoC Verification for Embedded Systems Market — IEEE International SoC Conference [Электронный ресурс]. — Режим доступа: http://www.docstoc.com/docs/55759007/Current−Status−and−Challenges−of−SoC−Verification−for−Embedded.

- Верификация FPGA-проектов [Электронный ресурс]. — Режим доступа: https://sites.google.com/site/electricgorokhov/home.