Реферат по теме выпускной работы

Содержание

- Введение

- 1. Актуальность темы

- 2. Цель и задачи исследования, запланированные результаты

- 3. Обзор исследований и разработок

- 3.1 Обзор международных источников

- 3.2 Обзор национальных источников

- 3.3 Обзор локальных источников

- 4. Виртуальная модель системы реального времени

- 5. Анализ результатов имитационных исследований

- 6. Разработка системы сбора и анализа данных на базе платы FPGA Xilinx Spartan-3E

- Выводы

- Список источников

Введение

Система реального времени – это аппаратно-программный комплекс, реагирующий за предопределенное время на непредсказуемый поток внешних событий. СРВ должна успеть отреагировать на событие, возникшее на объекте, в течение времени, критического для этого события, величина которого определяется объектом и самим событием, и, естественно, может быть разной, но время реакции системы должно быть предопределено при создании системы. Отсутствие реакции в предусмотренное время считается ошибкой для систем реального времени, система должна успевать реагировать на события, происходящие одновременно. Даже если два или более внешних события протекают одновременно, система должна успеть среагировать на каждое из них в течение интервалов времени, критических для этих событий.

LabVIEW (англ. Laboratory Virtual Instrumentation Engineering Workbench) – это среда разработки и платформа для выполнения программ, созданных на графическом языке программирования G фирмы National Instruments (США). Первая версия LabVIEW была выпущена в 1986 году для Apple Macintosh, в настоящее время существуют версии для UNIX, Linux, Mac OS, а наиболее развитыми и популярными являются версии для Microsoft Windows.

Исходные тексты переносные, а программы будут выглядеть одинаково во всех системах. Код, сгенерированный LabVIEW также может быть выполнен на Windows Mobile или PalmOS (на данный момент поддержка PalmOS прекращена). Этот язык может с успехом использоваться для создания больших систем, для обработки текстов, изображений и работы с базами данных. Инженеры и ученые используют NI LabVIEW для разработки измерительных систем, испытательных стендов и систем управления. Кроме самой возможности программирования среда LabVIEW предоставляет в распоряжение пользователя широкий спектр инструментов и библиотек от интерактивных мастеров настройки и пользовательских интерфейсов до встроенных компилятора, компоновщика и средств отладки.

1. Актуальность

Системы реального времени – чрезвычайно важное направление современных технологий. Достаточно сказать, что все автоматизированные комплексы, от которых зависят жизнь и здоровье людей, являются системами реального времени. Роль таких систем постоянно растет, поскольку все больше технических процессов изучается с достаточной для автоматизации глубиной.

Однако разработка таких систем является, как правило, трудоемкой задачей, требующей значительных затрат времени и материальных затрат. К тому же разработанная система является, как правило, крайне негибкой и предназначена для решения узкого круга задач без возможности в кратчайшие сроки перестроить систему под новые технические требования.

2. Цель и задачи исследования, ожидаемые результаты

Целью данной магистерской работы является разработка методики автоматизации, а соответственно – ускорение разработки различных по назначению систем реального времени и сокращение затрат на их реализацию. С этой целью в работе предлагается использование ПЛИС и специализированной среды разработки LabVIEW, которые в тандеме открывают широкие инженерные возможности.

С одной стороны с помощью языка программирования G можно явно задавать аппаратную структуру разрабатываемой системы, потоковое программирование предполагает легкость реализации параллельно выполняемых блоков операций, а богатая библиотека встроенных операторов позволяет сконцентрироваться на реализации именно проблемной задачи. Все это обусловливает большую, чем при использовании классических методов разработки подобных систем (VHDL, С, Assembler, Matlab и др.), скорость разработки программно-аппаратного продукта.

Использование ПЛИС для реализации системы реального времени или системы, приближенной к реальному времени, открывает возможность использовать только одно физическое устройство для многих практических, научно-исследовательских целей, а перепрограммирование ПЛИС под новую задачу при наличии готового решения реализации занимает считанные секунды.

Пакет средств LabVIEW поддерживает различные цифровые и аналоговые устройства для организации взаимодействия персонального компьютера и исследуемого объекта. Однако, в список FPGA-плат, поддерживаемых средой, входят только фирменные продукты National Instruments как, например, платы CompactRIO, имеющие множество преимуществ, среди которых: значительное количество логических вентилей, наличие встроенных контроллеров реального времени, высокая надежность и качество исполнения продукта – но все это обуславливает высокую стоимость плат линейки CompactRIO. Поэтому компания National Instruments добавила поддержку плат Xilinx Spartan-3e, которая и используется в данной работе.

Таким образом, можно выделить следующие задачи исследования в рамках данной темы:

- Анализ и исследование методов программирования на потоковом языке G в среде LabVIEW;

- Разработка многопоточной модели системы реального времени и ее элементов;

- Исследование инструментов работы в среде LabVIEW с ПЛИС;

- Исследование различных конфигураций систем реального времени;

- Разработка методики использования пакета средств LabVIEW для конфигурирования FPGA-плат;

- Апробация разработанных решений в условиях лабораторного практикума и в условиях, приближенных к производственным.

Ожидаемыми результатами работы является разработанная виртуальная модель системы реального времени и комплексная система сбора и анализа данных в составе FPGA и хоста с графическим интерфейсом в виде обычного персонального компьютера, связанные между собой по интерфейсу USB.

3. Обзор исследований и разработок

Поскольку в наше время в индустриальной и научной сферах почти не осталось технических процессов, не имеющих средств автоматизации, вопросы разработки систем автоматизации, включая системы сбора и анализа данных довольно часто рассматривается в научных работах и промышленных проектах во многих странах мира. Разработка же таких систем, ориентированных на исполнение на FPGA-решениях, является еще более перспективным направлением, поскольку аппаратная часть систем реального времени, ориентированных на сбор и обработку информации из внешних источников, обычно имеет низкую гибкость использования, высокую стоимость и значительный срок разработки. Использование же в качестве главного аппаратного ядра таких систем FPGA-платы, позволяет не только значительно сократить сроки разработки систем, но и при надобности реконфигурировать такое решение в другой, ранее разработанный проект за несколько секунд.

3.1 Обзор международных источников

Главным источником информации по технике программирования LabVIEW, разработки виртуальных приборов, ориентированных на выполнение на FPGA-решениях National Instruments и Xilinx Spartan-3E, является раздел Developer's Zone главного интернет-ресурса National Instruments [1], на котором можно не только найти указания к разработке и учебный материал, но и примеры готовых проектов по различным тематикам.

Также источником информации о введенных в эксплуатацию научных и промышленных проектов в данной тематике являются буклеты международных конференций «NI Days», которые размещены в свободном доступе на ресурсах National Instruments. На конференциях «NI Days» рассматриваются новейшие разработки лидеров отрасли тестирования и верификации устройств, разработки систем автоматизирования, медиасистем и проч., которые реализованы с помощью программной и аппаратной продукции National Instruments. Например, на конференции «NI Days» в Великобритании 2008 года [2], две статьи посвящены именно разработке систем сбора и анализа данных на базе FPGA плат NI CompactRIO, которые уже введены в эксплуатацию и показывают высокие результаты в коммерческих проектах военно-промышленного комплекса США и автоиндустрии.

Значительное количество учебных пособий англоязычных авторов, таких как «Advanced Programming Techniques, Second Edition» авторов Rick Bitter, Taqi Mohiuddin, Matt Nawrocki [3], «LabVIEW Digital Signal Processing and Digital Communications» автора Cory L. Clark [4], «Analog Electronics with LabVIEW» автора Kenneth L. Ashley [5] и другие, являются массивным источником знаний для эффективной разработки различных LabVIEW-продуктов, содержащих множество особенностей LabVIEW-проектирования.

Конференции National Instruments проводятся и в России. На них также представлены современные разработки в данной сфере [6]. Вообще же в России движение использования LabVIEW значительно более развито, чем в Украине. В связи с этим фактом, имеется значительное количество учебников, пособий и статей по данной тематике. Такие учебники как «Автоматизация измерений, контроля и испытаний» авторов Мищенко С.В., Дивина, и др. [7], «Автоматизация физических исследований и эксперимента – компьютерные измерения и виртуальные приборы на основе LabVIEW 7» Бутырина П.А. [8], «Логическое управление. Методы аппаратной и программной реализации» Шалыто А.А. [9], «Цифровая обработка сигналов в LabVIEW» под ред. В. П. Федосова [10], «Цифровая обработка сигналов с помощью платы АЦП и программного комплекса LabView» С.Д. Мещерякова [11] и другие являются источником опыта исследований и разработок компетентных авторов LabVIEW-продуктов.

3.2 Обзор национальных источников

К сожалению, в пределах Украины использование LabVIEW для разработки систем реального времени, а также конфигурирования FPGA-плат не очень распространено, вследствие чего количество информации по этой тематике ограниченно и, как правило, только дублирует иностранные материалы. Однако полезными в рамках данной темы являются статьи Тесленко В.А. [12] Денисенко В.В. и Халявко А.Н. [13] по применению разнотипных датчиков в системах сбора данных и управления. Также следует упомянуть о курсе лекций по программированию в среде LabVIEW на ресурсе picad.com.ua [14].

3.3 Обзор локальных источников

Среди магистров ДонНТУ еще никто не занимался данной темой, и в целом использование LabVIEW для решения практических задач является нераспространенным в вузах Украины.

Однако следует упомянуть о работе по разработке системы реального времени на FPGA-плате с использованием VHDL и средств фирмы-производителя целевых плат Xilinx. Так, в статье «Разработка системы реального времени на базе Xilinx XC3S500E Spartan-3E FPGA» Волошина Д.Н [15] рассматриваются вопросы верификации встраиваемых систем-на-кристалле (СнК) на базе FPGA на маршруте их проектирования. Проводится обзорный анализ существующих методов верификации систем-на-кристалле и цифровых устройств в целом. На основании обзора формируется перечень актуальных проблем при верификации СнК и возможных путей их преодоления с целью создания качественно нового подхода к верификации FPGA-проектов.

4. Виртуальная модель системы реального времени

Разработкой виртуальной модели достигаются несколько важных задач: во-первых, в ходе работы над моделью были усвоены основные приемы и изучена специфика работы в среде LabVIEW; во-вторых, в ходе разработки модели исследована работа супервизора системы, обработчиков задач, обработчика прерываний и др., а также алгоритмы их работы; в-третьих, она включает в себя интерфейс системы, выполняющий стандартные функции, которые пригодятся при разработке хоста реальной системы, кроме того, система имеет структурные элементы, которые могут быть реализованы аппаратно с помощью модуля LabVIEW FPGA на плате (супервизор, обработчик прерываний и проч.). Таким образом, модель является основой для реализации системы реального времени на ПЛИС и хоста с интерфейсом пользователя на персональном компьютере.

Главную роль многозадачной системы реального времени играет супервизор. Для выполнения своих функций он обрабатывает параметры задач с частотой работы, которая задается системным таймером. Поскольку за превышение максимального времени выполнения задаче присваивается штрафная санкция, и ее работа принудительно завершается, супервизор должен передавать управление задаче из очереди на выполнение в момент снятия текущей задачи, а не через такт. Поэтому супервизор должен работать с частотой, превышающей частоту выполнения задач. В разрабатываемой системе, Δtсист составляет 1с, поскольку модель носит тестовый характер и реализуется в операционной системе MacOS, в основе которой лежит ядро-UNIX, которая не является операционной системой реального времени. Супервизор же срабатывает с интервалом в 0.1 с, чем обеспечивается выполнение вышеупомянутой функции.

В соответствии с функциональными возможностями, можно выделить три логических блока функций супервизора, которые и реализуют эти возможности:

- блок реакции на внешние флаги;

- блок управления состояниями задач в соответствии с текущим состоянием и планового времени вызова на выполнение;

- блок контроля продолжительности сеанса работы задачи и присвоения штрафных санкций.

Супервизор не реагирует на внешние события непосредственно. Поэтому необходимым компонентом СПЗ кроме супервизора, является блок первичных обработчиков событий. Первичные обработчики идентифицируют события от внешних устройств системы (работу которых симулируют клавиатура и мышь – с помощью них пользователь в любой случайный момент времени вызывает соответствующие прерывания) и формируют соответствующие флаги в области флагов, которые и обрабатываются диспетчером задач.

Как уже упоминалось ранее, имитационная модель СРВ выполнена с использованием платформы LabVIEW. Программа, написанная в среде LabVIEW, называется виртуальным прибором (ВП или Virtual Instrument – VI). ВП состоит из четырех частей: лицевой панели, блок-диаграммы, иконки и соединительной панели.

В LabVIEW интерфейс – лицевая панель, создается с помощью элементов управления (кнопки, переключатели и др.) и отображения (графики, светодиоды и др.). После этого на блок-диаграмме ВП осуществляется программирование с использованием графических реализаций функций для управления объектами на лицевой панели.

LabVIEW используется для программирования различных DAQ-устройств, систем контроля изображения и движения, аппаратных средств, имеющих интерфейсы типа GPIB, VXI, PXI, RS-232 и RS-485. LabVIEW имеет встроенные возможности для работы в компьютерных сетях Интернет, используя LabVIEW Web Server и программные стандарты TCP /IP и Active X.

Если предполагается использование ВП внутри другого ВП, ВП в составе другого ВП называется виртуальным подприбором (subVI). Для использования виртуального подприбором часто необходимо определить входные и выходные терминалы для ввода исходной информации и вывода обработанных данных в основной ВП. Для конфигурирования терминалов используется соединительная панель, на которой вводится соответствие конкретных элементов управления с входными терминалами и элементов отображения с выходными терминалами.

В рамках основного ВП виртуальный подприбор отражается согласно созданной для него иконки, которая создается при сохранении ВП.

Все блоки выполняются параллельно в разных потоках. Структурно супервизор состоит из ряда алгоритмических кадров:

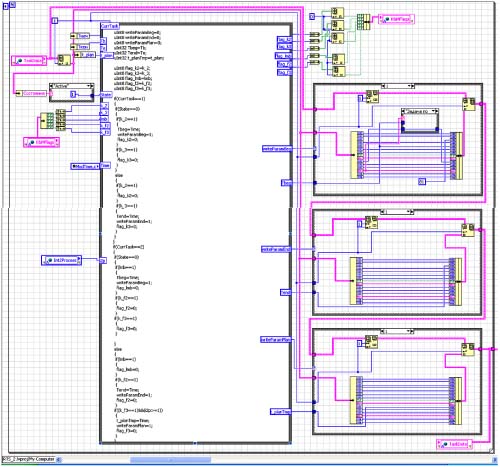

- Выполнение анализа флагов внешних событий от клавиатуры и мыши, по которым устанавливаются соответствующие параметры задач. Блок-диаграмма первого кадра изображена на рис.1.

Рисунок 1 – Блок-диаграмма первого кадра супервизора

- Анализ завершения интервала активности задач и флагов завершения

работы задач, формирование массива параметров задач, упорядоченного по приоритетам задач.

Рисунок 2 – Блок-диаграмма второго кадра супервизора

-

Анализ параметров РВ и флагов: формирование состояний задач, планового

времени вызова, запись фактического времени вызова, определение необходимости наложения штрафа за превышение времени выполнения задачи, заполнение полей информационной структуры выполняемой задачи, определение наличия необработанных прерываний и уменьшение значения счетчика необработанных прерываний в случае завершения работы задачи по прерыванию (задачи №3) . Блок-диаграмма третьего кадра изображена на рис. 3

Рисунок 3 – Блок-диаграмма третьего кадра супервизора

Разработанную LabVIEW-программу можно разделить на три функциональных блока: основной блок, блок первичной обработки внешних событий, блок имитации задач.

Основной блок представляет собой временной цикл с продолжительностью итерации 0.1 с, в котором выполняется отсчет времени моделирования, вызов супервизора и управления элементами интерфейса программы.

Блок имитации задач содержит четыре временных цикла с продолжительностью итерации 1 с, каждый из которых имитирует работу прикладных задач реального времени. Все задачи являются независимыми друг от друга и выполняется параллельно в разных потоках.

В блоке первичной обработки внешних событий производится фиксация событий с внешних устройств – мыши и клавиатуры.

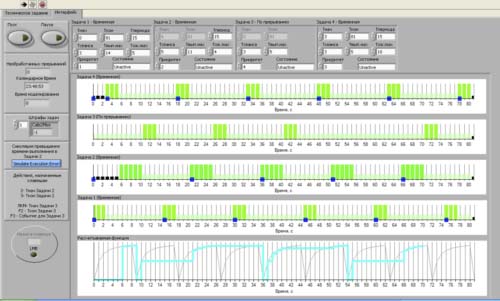

5. Анализ результатов имитационных исследований

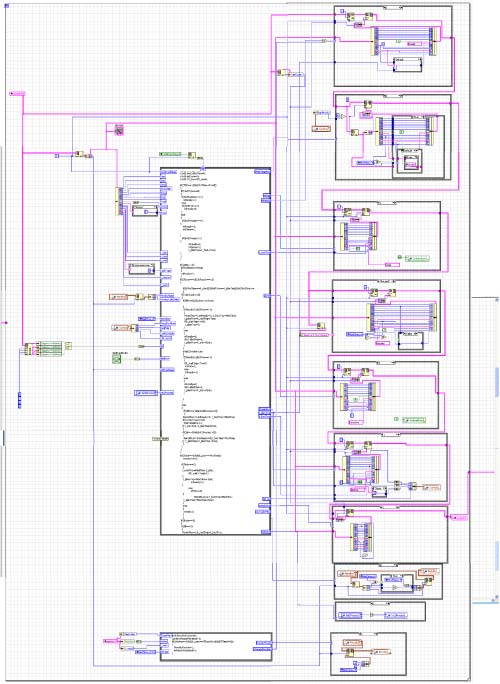

Первое исследование моделирует ситуацию, когда задачи выполняются в плановом режиме, не перекрывая плановые времена вызова других задач.

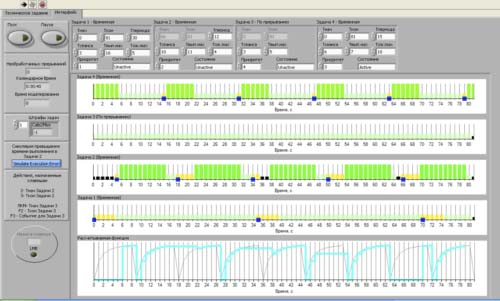

На рис. 4 изображены результаты моделирования №1.

Рисунок 4 – Результаты моделирования №1

Как видно, плановые времена вызова задач по времени вычисляются верно. В рассчитанные относительно фактического времени вызова значения планового времени вызова задачи получают управление и завершают свою работу через Тсеанса секунд после фактического времени начала работы. Интервал активности задачи №2 начат нажатием клавиши «2», интервал активности задачи №3 – нажатием левой кнопки мыши. На восемьдесят первой секунде моделирования интервалы активности задач были завершены по значению Ткон. Задача №2 успешно выполнялась и выводила на лицевую панель расчеты заданной функции в моменты своей работы. В моменты времени 11, 26, 41, 71 в систему поступали прерывания, инициализирующие начало выполнения задачи №3.

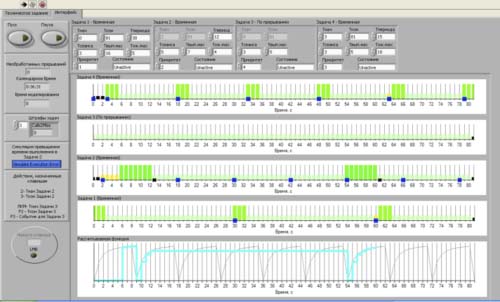

На рис. 5 изображены результаты моделирования №2.

Рисунок 5 – Результаты моделирования №2

В данном моделировании распространенной была ситуация, когда задачи не получали управления из-за того, что система была занята в момент времени, который соответствовал их плановым временам исполнения. Поэтому задачи переходили в состояние ожидания выполнения. Распространены также ситуации, когда несколько задач являются претендентами на запуск в одинаковый момент времени (1 и 2 задачи в момент времени 0, 1 и 2 в момент времени 44, 4 и 2 в момент времени 63). В такой ситуации задача с высшим приоритетом начинает выполнение, а задача с меньшим остается в состоянии ожидания. Расчет планового времени запуска выполняется относительно фактического времени запуска задачи на выполнение.

Работа режима ожидания задачи (рис. 5). Задачи 1 и 2 получают Тнач одновременно в момент 1 сек. На исполнение поступает задача 2, а первая получает состояние «Ожидание выполнения». После освобождения процессорного ресурса (момент времени 5 сек) задача 1 получает управление.

На рис. 6 изображены результаты моделирования №3.

Рисунок 6 – Результаты моделирования №3

В данном моделировании задача 1 ни разу не получила управления из-за того, что все три раза в момент Тплан выполнялась другая задача, или начинала выполнение задача с высшим приоритетом, и во всех случаях она превышала время максимального ожидания, и супервизор снимал ее из очереди на выполнение.

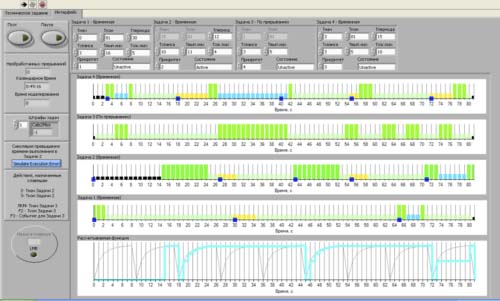

В следующем моделировании рассматривается ситуация превышения времени выполнения задачей 2. В процессе моделирования пользователь нажал клавишу симуляции ошибки превышения времени выполнения в задаче 2, из-за чего она не заканчивала свою работу, пока продолжительность ее работы не превысила максимального времени работы. Тогда супервизор налагает на задачу штраф, который выражается в трехкратном блокировании ее вызова инициирующей событием (время моделирования равно значению Тплан), что и отражено на интерфейсе. На рис. 7 изображены результаты моделирования №4.

Рисунок 7 – Результаты моделирования №4

На рисунке 8 приведены результаты моделирования №5.

Рисунок 8 – Результаты моделирования №5

В предыдущих моделированиях прерывания поступали лишь в то время, когда система была свободна. В моделировании №5 прерывания поступает в момент выполнения другой задачи. Поскольку обработка прерываний в разработанной системе немедленная, то выполняемая задача приостанавливается на время обработки всех необработанных прерываний. То время, что задача находится в паузе, нельзя считать временем ожидания и задача, приостановленная на долгое время, НЕ штрафуется супервизором. Когда прерывания обработаны, приостановленная задача возобновляет свою работу и работает отведенное ей время. Если следующий плановый вызов приходится на время, когда задача приостановлена, плановое время вызова перевычисляется добавлением к предыдущему значению Тпериода задачи. То же самое происходит, если Тплан задачи приходится на момент, когда задача дорабатывает время, оставшееся ей после приостановки.

6. Разработка системы сбора и анализа данных на базе платы FPGA Xilinx Spartan-3E

На следующем этапе магистерской работы предполагается аппаратная реализация системы реального времени на базе FPGA-решения с помощью тулкита LabVIEW FPGA.

Главным достоинством систем сбора и анализа данных, ,построенных на решениях FPGA, является возможность реконфигурирования системы, поскольку гибкость платформы позволяет охватить широкий круг задач, от сбора и хранения данных и сложных алгоритмов анализа до высокоскоростного управления в масштабе наносекунд.

На основе CompactRIO могут быть созданы встраиваемые системы для таких задач, как бортовой сбор данных, шумовой и виброакустический анализ, управление оборудованием. Автономность такой системы оказывается востребованной во многих научных и промышленных проектах:

– Сборка/обработка – высокоскоростное управление перемещениями, управление периодическими процессами, дискретное управление.

– Управление тяжелыми станками – обработка сигналов в реальном времени и управление силовой электроникой и гидравлическими системами.

– Полупроводниковая и биомедицинская промышленность – специфичное управление перемещениями и обработка изображений, контроль подачи сырья.

– Мониторинг состояния оборудования – анализ износа, контроль охлаждение наличия смазки, отсутствия возгорания и т.д.

– Мобильные/портативные системы шумового и виброакустического анализа – анализ шумов, вибраций, динамический анализ сигналов.

– Распределенный сбор данных – центральный контроллер с распределенными узлами ввода-вывода, подключенными по проводным или беспроводным сетям.

Такая система, как правило имеет архитектуру, состоящую из трех процессоров: на компьютере с ОС Windows, на контроллере реального времена и ядро ПЛИС. Учитывая высокую стоимость решений National Instruments, в работе используется плата Xilinx Spartan-3E, которая рекомендована National Instruments для выполнения некоммерческих проектов в учебных заведениях. Поскольку платы Spartan-3E, в отличие от плат серии CompactRIO, не имеют бортового контроллера реального времени, предполагаемая структура разрабатываемой системы включает лишь процессор хост-станции и ядро ПЛИС.

Логика, функции ввода-вывода, тактирование, триггеринг и синхронизация реализуются в ПЛИС на аппаратном уровне и полностью определяются пользователем при конфигурировании. Ядро ПЛИС напрямую соединено с модулями ввода-вывода, что обеспечивает точность и гибкость тактирования, триггеринга и синхронизации. Модули ввода-вывода содержат встроенные средства предварительной обработки сигналов, преобразователи ЦАП или АЦП, иногда контуры изоляции. Данные между ПЛИС и модулями передаются в цифровом виде.

Предполагается, что аппаратный модуль на ПЛИС принимает и накапливает информацию из датчиков с заданной частотой, периодически посылая пакеты информации по USB-интерфейсу на хост-программу на персональном компьютере, которая визуализирует получаемые данные, сохраняет их в лог-файл и обеспечивает информационное взаимодействие пользователя с платой через графический интерфейс.

Таким образом, предполагается разработка системы, упрощенная иллюстрация работы которой приведена на рис. 9

Рисунок 9 – Иллюстрация работы системы (анимация)

При написании данного реферата магистерская работа еще не завершена. Окончательное завершение: декабрь 2013 года. Полный текст работы и материалы по теме могут быть получены у автора или его руководителя после указанной даты.

Список источников

- National Instruments – Developer's Zone [Электронный ресурс]. – Режим доступа: http://zone.ni.com/dzhp/app/main.

- NIDays08 – Worldwide Graphical System Design Conference [Электронный ресурс]. – Режим доступа: ftp://ftp.ni.com/pub/branches/uk/nidays2008/NIDaysBooklet.pdf – pp. 31-34, 41-42, 46-47.

- Rick Bitter, Taqi Mohiuddin, Matt Nawrocki. Advanced Programming Techniques, Second Edition – Boca Raton: CRC Press, 2006. – 500 p.

- Cory L. Clark. LabVIEW Digital Signal Processing and Digital Communications – New York: McGraw-Hill, 2005. – 205 p.

- Kenneth L. Ashley. Analog Electronics with LabVIEW – Upper Saddle River, NJ: Prentice Hall, 2003. – 432 p.

- Деcятая международная научно-практическая конференция. Инженерные, научные и образовательные приложения на базе технологий National Instruments 2011 [Электронный ресурс]. – Режим доступа: http://www.labview.ru/Conference2011/Sbornik%20trudov%20konferencii%202011%20electr.pdf – pp. 245-246, 268-273.

- Мищенко С.В., Дивин А.Г., Жилкин В.М., Пономарев С.В., Свириденко А.Д. Автоматизация измерений, контроля и испытаний – Т.: издательство ТГТУ, 2007. – 116 с.

- Бутырин П.А. Автоматизация физических исследований и эксперимента: компьютерные измерения и виртуальные приборы на основе LabVIEW 7 – М.: ДМК Пресс, 2005. – 264 с.

- Шалыто А.А. Логическое управление. Методы аппаратной и программной реализации – СПб.: Наука, 2000. – 780 с.

- Федосов В.П., Нестеренко А.К. Цифровая обработка сигналов в LabVIEW – М.: ДМК Пресс, 2007. – 456 с.

- Мещеряков С.Д. Цифровая обработка сигналов с помощью платы АЦП и программного комплекса LabView – М.: Московский государственный университет им. М. В. Ломоносова, 2004. – 44 с.

- Тесленко В.А. Подключение датчиков к ПК. Учебный практикум – К.: НТУУ "КПИ", 2004. – 7 с.

- Денисенко В.В., Халявко А.Н.Термометры сопротивления, Термисторы и Термопары. Учебный практикум – Таганрог: НИЛ АП, 2004. – 5 с.

- Уроки по LabVIEW [Электронный ресурс]. – Режим доступа: http://www.picad.com.ua/lesson.htm.

- Волошин Д.Н. Разработка системы реального времени на базе Xilinx XC3S500E Spartan-3E FPGA. – Інформатика і комп’ютерні технології (ІКТ-2011) / Матерiали VII мiжнародної науково-технiчної конференцiї студентiв, аспiрантiв та молодих вчених – Донецьк, ДонНТУ – 2011, с. 44-47.