Реферат за темою випускної роботи

Зміст

- Вступ

- 1. Актуальність теми

- 2. Мета і задачі дослідження та заплановані результати

- 3. Огляд досліджень та розробок

- 3.1 Огляд міжнародних джерел

- 3.2 Огляд локальних джерел

- 4. Аналіз областей використання мережевих процесорів

- 5. Експериментальні дослідження на моделі мережі масового обслуговування

- Висновки

- Перелік посилань

Вступ

Мережеві процесори (МП) призначені для забезпечення продуктивності та гнучкості за рахунок архітектури, яка є паралельною та програмується. Ця архітектура дає їм перевагу перед процесорами загального призначення в продуктивності та апаратними рішеннями в гнучкості. Але використання МП також призводить до нових труднощів. Важливо вивчити обмеження архітектури МП, щоб можна було в повній мірі використовувати переваги блоків МП для досягнення необхідної продуктивності для певної програми [1].

Продуктивність - обсяг інформації, яка оброблюється системою в одиницю часу. Продуктивність програмного забезпечення істотно залежить від кількості ресурсів, які споживаються програмою в процесі виконання.

Аналіз продуктивності програмного забезпечення характеризується складністю визначення та завдання параметрів споживання ресурсів, що характеризують навантаження компонентів моделі програми для розрахунку за ними показників продуктивності.

Під час модифікації програмного забезпечення відбуваються значні зміни параметрів продуктивності, що бажано моделювати і прогнозувати заздалегідь. Це обумовлює необхідність аналізу ПЗ на стадії проектування, а відсутність досить простих і широко застосовних моделей і методів аналізу аналітичного або імітаційного характеру робить задачу створення моделей і методів аналізу продуктивності програм досить актуальною.

1. Актуальність теми

Постійне збільшення трафіка в комп'ютерних мережах робить актуальною проблему створення високопродуктивних спеціалізованих мережевих процесорів і їх програмного забезпечення (ПЗ) для обробки потоків даних на різних рівнях стека протоколів. Тому велике значення має створення програм, які будуть забезпечувати максимальну продуктивність мережевих процесорів.

Більшість існуючих моделей дозволяють оцінити продуктивність ПЗ тільки після отримання готового продукту. У сучасній ситуації задача реалізації кількох проектів з подальшим їх порівнянням є дуже трудомісткою, тому гостро стоїть питання про створення методів та підходів аналізу продуктивності ПЗ на стадії проектування, без необхідності реалізації проекту.

2. Мета і задачі дослідження та заплановані результати

Метою даного дослідження є аналіз аналітичних моделей і методів оцінки продуктивності програмного забезпечення мережевих процесорів, розробка програмного забезпечення, що реалізує математичні моделі мережевих процесорів.

Основні задачі дослідження:

- Аналіз областей використання мережевих процесорів.

- Аналіз архітектури та програмного забезпечення мережевих процесорів.

- Розробка математичних моделей для дослідження продуктивності системного та прикладного програмного забезпечення мережевих процесорів.

- Розробка програмного забезпечення для реалізації математичних моделей.

- Проведення експериментів на моделях.

Планується отримання таких наукових і практичних результатів:

- Математичні моделі для дослідження продуктивності системного та програмного забезпечення мережевих процесорів.

- Програмне забезпечення для моделювання мережевих процесорів.

- Рекомендації з приводу вибору ефективних параметрів системного і прикладного програмного забезпечення мережевих процесорів.

3. Огляд досліджень і розробок за темою

Аналіз ефективності структур мережевих процесорів є важливою науковою задачею, яка розглядається кількома дослідницькими групами в усьому світі [3].

3.1 Огляд міжнародних джерел

Детально стан проблеми моделювання та аналіз методик моделювання мережевих процесорів розглянуті в статтях [3 - 6].

Існує три основні підходи до дослідження архітектури мережевих процесорів: імітаційні моделі [10], аналітичні моделі, засновані на кривих прибуття і обслуговування [11] і комплексна методика моделювання мережевих процесорів (КМСП)[12].

Методика аналізу ефективності виконання мережевих програм на багатоядерних структурах була розглянута в роботах [7, 8]. Запропонована методика складається з двох основних етапів: імітаційне моделювання роботи програми на еталонному обчислювальному ядрі та розрахунок характеристик роботи цієї програми на багатоядерному мережевому процесорі. Недоліком використовуваної аналітичної моделі є неможливість дослідження конвеєрних структур і можливостей виконання декількох програм на різних обчислювальних ядрах.

У роботі [9] запропоновано модель структури МП, заснована на теорії масового обслуговування. Модель дозволяє досліджувати роботу багатоядерного мережевого процесора, в якому всі ядра працюють паралельно. Процесор має одне головне обчислювальне ядро, яке обробляє потік пакетів і, за зміною навантаження, підключає або відключає додаткові обчислювальні ядра. Однак, запропонована модель не дозволяє досліджувати конвеєрні структури МП, які є потужним інструментом підвищення продуктивності мережевого процесора.

3.2 Огляд локальних джерел

Національні та локальні дослідження проблем моделювання та аналізу характеристик мережевих процесорів представлені роботами доцента кафедри прикладної математики та інформатики Донецького національного технічного університету Ю.В. Ладиженського і його аспірантів В.І. Грищенко і М. Юніса [3 - 6, 13 - 20].

У роботах [13 - 14] описані особливості та функції мережевих процесорів, аналіз сучасних МП, їх технічних характеристик і функціональних можливостей, а також перспективи розвитку сучасних мережевих процесорів. У статті [15] запропонована узагальнена структура МП, яка відображає перспективні тенденції в розробці мережевих процесорів.

Роботи [3, 6] присвячені моделюванню мережевих процесорів і маршрутизаторів на багатоядерних мережевих процесорах. В [16, 17] описується комплексна методика моделювання мережевих процесорів, а також питання програмування пакетних мережевих процесорів.

В [5] представлена модель МП з роздільною пам'яттю для коду та даних і проведене порівняння ефективності мережевих процесорів зі спільною та роздільною пам'яттю.

Роботи [4, 18 - 20] присвячені опису аналітичної моделі мережевих процесорів пакетної обробки даних, запропонована методика дослідження впливу архітектури кешу на продуктивність МП.

4. Аналіз областей використання мережевих процесорів

Мережеві процесори використовуються у виробництві різних типів мережевого обладнання:

- маршрутизаторів і комутаторів;

- мережевих екранів;

- прикордонних контролерів сесій;

- пристроїв виявлення вторгнень;

- пристроїв запобігання вторгнень;

- систем моніторингу мережі.

В [2] розглянуто розвиток мережевих процесорів з плином часу.

Із збільшенням кількості областей застосування мережевих процесорів, ринок почав сегментуватися на три основні області мережевого обладнання: основні пристрої, прикордонні та пристрої доступу. Кожен з цих напрямків має різні області застосування цільових і робочих характеристик. Основні пристрої знаходяться в середині мережі. У результаті вони є найбільш залежними від продуктивності і найменш чутливими до гнучкості. Прикладами таких пристроїв є гігабітні та терабітні маршрутизатори.

Прикордонні пристрої розташовані між ядром мережі (основними пристроями) і пристроями доступу. Прикладами прикордонних пристроїв є URL-балансувальникі навантаження і брандмауери. Вони орієнтовані на середні та високі швидкості передачі даних і обробку більш високого рівня, тому потрібен певний запас гнучкості.

Обладнання доступу представлено різними пристроями доступу до мережі. Більшість з них займається агрегуванням і передачею по мережі величезної кількості потоків трафіку. Прикладами таких пристроїв є кабельний модем і точка бездротового доступу.

Кожному рівню мережі потрібні різні комбінації продуктивності обробки, функціональності та вартості. Для ефективного задоволення цих потреб мережеві процесори повинні бути оптимізовані не тільки під конкретні вимоги, які пред'являються обладнанням, а й для послуг, що надаються в кожному сегменті інфраструктури мережі.

Мережеві процесори застосовуються для задач представлених нижче.

- Завдання рівня управління:

- контроль і управління роботою пристрою;

- завдання менш критичні за часом.

- Завдання рівня даних:

- операції які відбуваються у реальному часі «на шляху пакету»;

- основні операції пристрої (одержання, обробка та передача пакетів).

У даній роботі увага приділяється комутаторам четвертого і сьомого рівня, а також комбінованим комутаторам (працюючим на обох рівнях) на основі багатоядерних мережевих процесорів, які описані в [21].

Комутатори четвертого рівня виконують маршрутизацію, незалежну від контенту, на рівні TCP. Він визначає цільовий сервер, коли клієнт запитує TCP з'єднання за допомогою пакету TCP SYN. Потім він асоціює пакети що належать цьому з'єднанню з тим же сервером. Цей механізм є ефективним для пакетів, які не проходять через рівень програм.

Комутатор сьомого рівня (контентозалежний) працює на рівні програм. Він забезпечує управління трафіком програм за допомогою глибокого аналізу пакетів. Комутатор сьомого рівня виконують стандартну процедуру «рукостискання» з клієнтами на їх стороні, без будь-якої участі сервера. З боку сервера, комутатор підтримує постійне з'єднання з кожним окремим сервером, що дозволяє знизити накладні витрати на встановлення з'єднання.

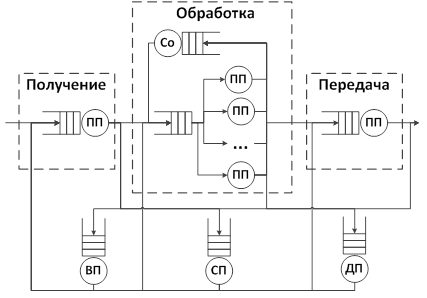

На малюнку 1 представлені операції на контентозалежному комутаторі.

Рисунок 1 – Операції на комутаторі 7 рівня

(анімація: 10 кадрів, 5 циклів повторення, 160 кілобайт)

Для комутаторів сьомого та четвертого рівня розроблено багато алгоритмів. Вони діляться на статичні, залежні від стану сервера, що залежать від стану клієнта, що залежать від станів клієнта і сервера. Описи цих алгоритмів можна знайти в оглядовій статті [22].

5. Експериментальні дослідження на моделі мережі масового обслуговування

Для моделі, представленої на малюнку 2, розглянутої більш детально в [1], був розроблений програмний продукт на мові С # з використанням середовища розробки MS Visual Studio 2012.

Рисунок 2 – Модель мережі масового обслуговування

На даній моделі були проведені експериментальні дослідження. За допомогою аналізу псевдокоду можна отримати приблизні витрати на обслуговування для модулів. За допомогою програми були отримані витрати на обслуговування для всіх ресурсів, максимальні витрати на обслуговування, які визначають максимальну продуктивність, а також максимальна продуктивність для даних умов, яка досягається при кількості пакетів J і середній час відгуку.

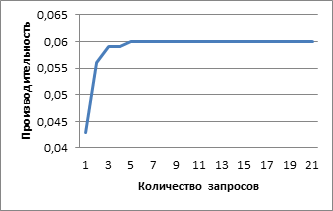

За цими результатами розрахунків на малюнку 3 показана залежність продуктивності від кількості запитів. Як видно з графіка, при кількості в 5 запитів досягається межа продуктивності.

Рисунок 3 – Результати експериментальних досліджень: залежність продуктивності від кількості запитів

Було відмічено, що додавання додаткових пакетних процесорів не призводить до істотного поліпшення продуктивності, тому що вузьким місцем програми є доступ до статичної пам’яті.

Висновки

Дослідження продуктивності програм для мережевих процесорів на стадії проектування є важливою задачею для зниження трудомісткості порівняння проектів по параметру виконання вимог до продуктивності.

Магістерська робота присвячена дослідженню методів і побудови моделей для оцінки продуктивності ПЗ для МП, а також розробці програми для проведення експериментів на даних моделях. У рамках проведених досліджень виконано:

- Аналіз областей використання мережевих процесорів.

- Аналіз архітектури та програмного забезпечення мережевих процесорів.

- Розбір математичних моделей для дослідження продуктивності програмного забезпечення мережевих процесорів.

- Реалізована велика частина програми для аналізу характеристик програмного забезпечення.

- Проведені деякі експерименти на моделі.

Надалі планується:

- Доробка програми для роботи з різними моделями.

- Розробка паралельної версії обчислювальних модулів.

- Проведення експериментів на моделях для подальшого отримання рекомендацій з приводу вибору ефективних параметрів системного і прикладного програмного забезпечення мережевих процесорів.

Перелік посилань

- Jie Lu, Jie Wang, "Analytical Performance Analysis of Network-Processor-Based Application Designs", Computer Communications and Networks, 2006. ICCCN 2006. Proceedings.15th International Conference on, October 2006

- Network processors of the past, present and future. White Paper. GlobalLogic. 2010.

- Ладыженський Ю.В. Моделирование сетевых процессоров пакетной обработки данных / Ю.В. Ладыженский, В.И. Грищенко // Матеріали міжнародної науково-практичної конференції «Інтернет – Освіта – Наука – 2006», м. Вінниця, 10 – 14 жовтня р. – 2006. – Т. 2. С. 417-422.

- В.И. Грищенко, Ю.В. Ладыженский, Моатаз Юнис. Влияние выделенного кэша команд на производительность сетевого процессора.// Наукові праці Донецького національного технічного університету, серія «Інформатика, кібернетика та обчислювальна техніка»,вып. 13 (185), Донецк, ДонНТУ, 2011. – С. 85-91.

- В.И. Грищенко, Ю.В. Ладыженский. Исследование влияния раздельной памяти на производительность многоядерного сетевого процессора. // Наукові праці Донецького національного технічного університету. Серiя «Проблеми моделювання та автоматизації проектування» (МАП-2011). Випуск: 9 (179) - Донецьк: ДонНТУ. - 2011. – 356 с.

- Моделирование маршрутизаторов на многоядерных сетевых процесорах / Грищенко В.И., Ладыженский Ю.В.//Научные труды ДонНТУ. Серия «Информатика, кибернетика и вычислительная техника».– 2010.– Вып. 12(165).– С.169-176

- Ning Weng and Tilman Wolf, “Pipelining vs. multiprocessors – choosing the right network processor system topology,” in Proc. of Advanced Networking and Communications Hardware Workshop (ANCHOR 2004) in conjunction with The 31st Annual International Symposium on Computer Architecture (ISCA 2004), Munich, Germany, June 2004.

- Tilman Wolf, Mark A. Franklin, "Performance Models for Network Processor Design," IEEE Transactions on Parallel and Distributed Systems, vol. 17, no. 6, pp. 548-561, Jun., 2006.

- Ahmadi M., Wong S. A Performance Model for Network Processor Architectures in Packet Processing Systems, Proceedings of the 19th International Conference on Parallel and Distributed Computing and Systems (PDCS 2007), pp. 176-181, Cambridge, Massachusetts, USA, November 2007.

- G. Memik and W. H. Mangione-Smith. NEPAL: A framework for efficiently structuring applications for network processors. InProc. Of Network Processor Workshop in conjunction with Ninth International Symposium on High Performance Computer Architecture (HPCA-9), Feb. 2003.

- Lothar Thiele, Samarjit Chakraborty, Matthias Gries, and Simon Kunzli, “Design space exploration of network processor architectures,” in Proc. of First Network Processor Workshop (NP-1) in conjunction with Eighth International Symposium on High Performance Computer Architecture (HPCA-8), Cambridge, MA, Feb. 2002, pp. 30–41.

- Tilman Wolf, Mark A. Franklin, "Performance Models for Network Processor Design," IEEE Transactions on Parallel and Distributed Systems, vol. 17, no. 6, pp. 548-561, Jun., 2006.

- Грищенко В.И., Ладыженский Ю.В., Юнис М. Перспективные архитектуры и тенденции развития современных сетевых процессоров / В.И. Грищенко, Ю.В. Ладыженский, М. Юнис // Материалы IV международной научно-технической конференции «Моделирование и компьютерная графика – 2011». – Донецк, 2011. – С. 93-97.

- Грищенко В.И., Ладыженский Ю.В., Юнис М. Основные направления развития современных сетевых процессоров / В.И. Грищенко, Ю.В. Ладыженский, М. Юнис // Наукові праці ДонНТУ. – Донецк, 2011. – (Серия «Інформатика, кібернетика та обчислювальна техніка»). – № 14 (188). – С. 123-127.

- Юнис М., Грищенко В.И., Ладыженский Ю.В. Обобщенная структура сетевых процессоров / М. Юнис, В.И. Грищенко, Ю.В. Ладыженский // Материалы VII международной научно-технической конференции студентов, аспирантов и молодых ученых «Информатика и компьютерные технологии – 2011». – Донецк, 2011. – С. 386-391.

- Ладыженский Ю.В., Грищенко В.И. Программирование процессоров обработки пакетов в компьютерных сетях / Ю.В. Ладыженский, В.И. Грищенко // Матеріали міжнародної науково-практичної конференції «Сучасні проблеми і досягнення в галузі радіотехніки, телекомунікацій та інформаційних технологій». – Запорожье, 2006. – C. 159-161.

- Грищенко В.И., Ладыженский Ю.В. Моделирование работы приложений на сетевых процессорах / В.И. Грищенко, Ю.В. Ладыженский // Материалы международной научно-практической конференции «Моделирование и компьютерная графика – 2007». – Донецк, 2007. – С. 167-173.

- Грищенко В.И., Ладыженский Ю.В. Исследование архитектуры кэша сетевых процессоров / В.И. Грищенко, Ю.В. Ладыженский // Науково-технічний журнал «Радіоелектронні і комп’ютерні системи». – № 6 (25). – С. 186-192.

- Ладиженский Ю.В., Грищенко В.И. Влияние политики замещения записей в кэше на производительность сетевого процессора / Ю.В. Ладыженский, В.И. Грищенко // Наукові праці ДонНТУ. – Донецк, 2007. – (Серия «Обчислювальна техніка та автоматизація»). – № 12 (118). – С. 114-119.

- Грищенко В.И., Ладыженский Ю.В. Оптимизация методики моделирования кэша сетевых процессоров / В.И. Грищенко, Ю.В. Ладыженский // Материалы III международной научно-технической конференции «Моделирование и компьютерная графика – 2009». – Донецк, 2009. – C. 249-254.

- J. Lu and J. Wang, "Performance Modeling and Analysis of Web Switch". in Proc. Int. CMG Conference, 2005, pp.665-672.

- V. Cardellini, E. Casalicchio, M. Colajanni, and P. S. Yu. The state of the art in locally distributed web-server systems. ACM Computing Surveys, 34(2):263-311, 2002.