Вавринюк Игорь Олегович

Факультет компьютерных наук и технологий

Кафедра cистем искусственного интеллекта

Специальность «Системы искусственного интеллекта»

Разработка и исследование модели кэширования информации в устройствах управления интелектуальных систем

Научный руководитель: к.т.н., доц. Бабаков Роман Маркович

Реферат по теме выпускной работы

Введение

1. Постановка проблемы.

2. Анализ литературы.

3. Цель исследования

4. Постановка задачи исследования.

5. Решение задачи и результаты исследований.

6. Принцип работы

Выводы

Список литературы

Введение

Одним из немаловажных факторов повышающих производительность процессора, является наличие кэш-памяти, а точнее её объём, скорость доступа и распределение по уровням.

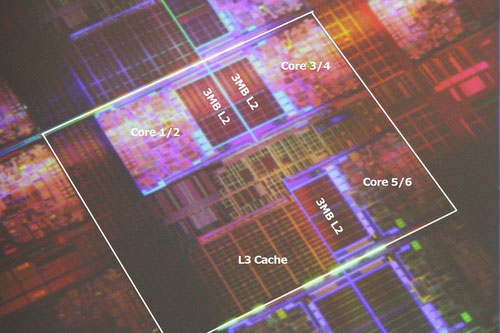

Рисунок 1 – Представление Кеш памяти

Уже достаточно давно практически все процессоры оснащаются данным типом памяти, что ещё раз доказывает полезность её наличия. В данной статье, мы поговорим о структуре, уровнях и практическом назначении кэш-памяти, как об очень немаловажной характеристике процессора.Кэш-память – это сверхбыстрая память используемая процессором, для временного хранения данных, которые наиболее часто используются. Вот так, вкратце, можно описать данный тип памяти. Она построена на триггерах, которые, в свою очередь, состоят из транзисторов. Группа транзисторов занимает гораздо больше места, нежели те же самые конденсаторы, из которых состоит оперативная память. Это тянет за собой множество трудностей в производстве, а также ограничения в объёмах. Именно поэтому кэш память является очень дорогой памятью, при этом обладая ничтожными объёмами. Но из такой структуры, вытекает главное преимущество такой памяти – скорость. Так как триггеры не нуждаются в регенерации, а время задержки вентиля, на которых они собраны, невелико, то время переключения триггера из одного состояния в другое происходит очень быстро. Это и позволяет кэш-памяти работать на таких же частотах, что и современные процессоры.Также, немаловажным фактором является размещение кэш-памяти. Размещена она, на самом кристалле процессора, что значительно уменьшает время доступа к ней. Ранее, кэш память некоторых уровней, размещалась за пределами кристалла процессора, на специальной микросхеме SRAM где-то на просторах материнской платы. Сейчас же, практически у всех процессоров, кэш-память размещена на кристалле процессора.

Рисунок 2 – Размещение Кеш памяти практически у всех современных процессоров

1. Постановка проблемы

Алгоритмы работы кэш-памяти в современных цифровых интеллектуальных системах достаточно сложны. В то же время к эффективности работы кэш-памяти выдвигаются достаточно высокие требования, что обусловлено ее относительно высокой стоимостью в составе цифрового устройства. Возможность модификации параметров модуля кэш-памяти позволяет подобрать такие их значения, при которых кэш-память будет обладать максимальной эффективностью для заданной микропрограммы. Подобная оптимизация характеристик модуля кэш-памяти даст возможность улучшить характеристики цифрового устройства управления и расширить потенциальную область его применения.

2. Анализ литературы

В работе [1] рассмотрены вопросы организации и функционирования цифрового устройства управления на базе композиционного микропрограммного устройства управления, для которого в работах [2-5] предложена методика увеличения быстродействия за счет использования модуля кэш-памяти микрокоманд, а также рассмотрены вопросы архитектурной организации модуля кэш-памяти. В работак [6-8] разработан эвристический алгоритм повышения эффективности использования модуля кэш-памяти в композиционном микропрограммном устройстве управления с разделением кодов, основанный на специальной адресации операторных линейных цепей. Предложен ряд стратегий объединения нескольких операторных цепей в одном блоке памяти, позволяющий в общем случае увеличить значение вероятности кэш-попаданий для граф-схемы реализуемого алгоритма управления.Рассмотрен пример использования предложенного эвристического алгоритма. Так же в работе [9] представлен метод синтеза базовой структуры композиционного микропрограммного устройства управления с разделением кодов и кэшированием микрокоманд. В основе метода лежит эвристическое распределение операторных линейных цепей в адресном пространстве управляющей памяти, обеспечивающее максимальное для реализуемого алгоритма управления значение вероятности кэш-попаданий. В источниках [10-11] рассматривается архитектура систем на базе процессоров Intel® Xeon® серии 5600 и их производительность. Как и в случае процессоров серии 5500, архитектура процессоров серии 5600 создает заказ-чикам определенные трудности вследствие высокой гибкости и широкого выбора конфигураций, предлагае-мых этой новой платформой. Анализ производительности в этом обзоре охватывает такие параметры, как задержки основной памяти, пропускная способность основной памяти и производительность приложений. Затем в обзоре рассматриваются аналитические результаты из предшествующих технических обзоров для серии 5500 и новые аналитические результаты, а также проблемы производительности, связанные с частотой памяти и заполнением разъемов памяти в конкретной системе. Кроме того, в этом техническом обзоре анализируются оптимальные конфигурации памяти, а также излагаются наилучшие типовые методики и рекомендации по конфи- гурированию соответствующих платформ IBM.

3. Цель исследования

Сформулировать требования к разработке компьютерной имитационно-аналитической модели кэш-памяти микрокоманд в составе цифрового устройства управления интеллектуальной системы.

4. Постановка задачи исследования

В данной работе решается научная задача построения компьютерной имитационно-аналитической модели модуля кэш-памяти, позволяющей определить эффективность работы кэш-памяти при заданных параметрах. Для решения данной задачи необходимо выполнить следующее:

- определить перечень параметров модуля кэш-памяти, влияющих на величину эффективности;

- получить аналитические выражения для определения эффективности;

- сформулировать основные требования к программной модели.

5. Решение задачи и результаты исследований

Кэш-память используется для хранения последовательностей микрокоманд, которые могут формироваться композиционным микропрограммным устройством управления (КМУУ) в ближайшее время. Статистический анализ работы современных компьютеров показывает, что около 90% всех данных, запрашиваемых вычислительным устройством, обычно находятся в кэш-памяти. Эта величина называется коэффициентом или вероятностью кэш-попадания.

Поскольку кэш-память работает быстрее, чем управляющая память, строящаяся в элементном базисе ПЗУ, можно определить среднее время ожидания всей системы памяти (среднее время доступа к памяти относительно комбинационной части КМУУ).

Введем следующие обозначения:

— Ph – вероятность кэш-попаданий;

— tУП – время доступа к управляющей памяти;

— tc – время поиска в кэш-памяти и выбор требуемых данных в случае кэш-попадания;

— tm – время доступа к данным в случае кэш-промаха; при этом tm=tУП+tп, где tп – так называемое время потерь при кэш-промахе, затрачиваемое на поиск запрашиваемых данных в кэш-памяти и помещение данных из управляющей памяти в кэш.

Тогда среднее время tE ожидания системы памяти, включающей в себя кэш-память, определяется как:Тe=Р*t+(1-P)*tm

Из выражения следует, что для достижения высокой скорости доступа, близкой к скорости доступа кэш-памяти, потребуется частота попаданий порядка 90%.

Другой способ оценки эффективности использования кэш-памяти состоит в определении того, насколько кэш-память повышает скорость доступа к системе памяти. Полагая, что в общем случае tc < tУП < tm, эффективность использования кэш-памяти E (выигрыш в скорости доступа к данным в системе с кэш-памятью по сравнению с системой без кэш-памяти).

Выражение (3) наглядно показывает, что при tУП=tm значение E>1 при любом Ph>0, то есть имеется постоянный выигрыш в быстродействии. Поскольку tm=tУП+tп, то очевидным является стремление уменьшить tп с целью максимального приближения tm к tУП.

Если tУП>>tc, то при Ph >0,9 имеем многократный выигрыш E. Например, при tУП=200 нс, tc=10 нс и Ph=0.9 выигрыш составит 6.9, то есть почти 700%.

На основании вышесказанного можно сделать вывод, что увеличению выигрыша в быстродействии в системе с кэш-памятью по сравнению с системой без кэш-памяти способствуют:

— увеличение вероятности кэш-попаданий Ph;

— снижение времени потерь при кэш-промахе tп;

— уменьшение времени доступа к кэш-памяти tc.

В выражении величины tс и tп определяются элементной базой и функциональной организацией аппаратуры. Конкретные значения этих величин можно определить, зная времена и порядок срабатывания электронных компонентов схем кэш-памяти и кэш-контроллера.

Наиболее сложно определить значение вероятности кэш-попаданий Ph, поскольку эта величина зависит как от выбранных характеристик кэш-памяти, так и от реализуемого КМУУ алгоритма управления. При этом величина Ph может изменяться на всем диапазоне вероятности – от 0 до 1 – и тем самым существенно влиять на эффективность использования кэш-памяти в КМУУ.

Если для величин tс и tm можно легко получить точные значения, то даже приблизительное определение значения Ph является затруднительным, поскольку ситуации кэш-попаданий и кэш-промахов не являются очевидными из заданной микропрограммы и характеристик кэш-памяти.

Для определения вероятности кэш-попаданий для заданной граф-схемы алгоритма управления и характеристик модуля кэш-памяти предлагается выполнить компьютерное имитационно-аналитическое моделирования структуры КМУУ с кэш-памятью для различных параметров и архитектурных типов модуля кэш-памяти. Модель должна реализовывать процесс функционирования КМУУ и модуля кэш-памяти, осуществляя сбор статистической информации о ситуациях кэш-попаданий и кэш-промахов. При этом обязательным является реализация алгоритмов замещения данных в модулях кэш-памяти.

Исходными данными для определения вероятности кэш-попаданий Ph будем считать:

— граф-схему алгоритма управления, интерпретируемого схемой КМУУ;

— вероятности переходов по логическим условиям, анализируемым в ГСА;

— адресацию микрокоманд, определяющую расположение микрокоманд в адресном пространстве управляющей памяти;

— число строк и слов в кэш-памяти.

Граф-схему алгоритма будем считать преобразованной для реализации схемой устройства управления с естественной адресацией микрокоманд. Также будем считать, что первой и последней вершинами в ГСА всегда являются операторные вершины (при их отсутствии они должны быть добавлены искусственно). Это условие необходимо для установления точек начала и конца выполнения алгоритма управления.

Вероятности переходов логических условий мы считаем известными потому, что эти значения могут зависеть не только от результатов выполнения микрокоманд, но и от внешних факторов (например, от датчиков). Эти значения не могут быть получены аналитически, а лишь опытным путем в процессе функционирования КМУУ, реализующего рассматриваемый алгоритм, в реальных условиях.

Адреса микрокоманд и размеры кэш-памяти являются теми факторами, изменение которых может привести к увеличению или уменьшению вероятности кэш-попаданий для заданного алгоритма. Начальное задание адресов микрокоманд может быть вызвано различными причинами, например, заранее отлаженным алгоритмом со сложными микропрограммными переходами или реализованным автоматом с «жесткой» логикой.

Содержимое операционных микрокоманд на этапе определения вероятности кэш-попаданий не имеет значения. Действия, выполняемые в них, либо никак не влияют на процесс выполнения алгоритма, либо влияют на вероятности переходов ЛУ, которые уже считаются заданными. Поэтому анализируемый алгоритм управления принимает абстрактный характер.

Таким образом, сформулируем основные требования к разрабатываемой модели:

1. Использование в качестве исходных данных значений следующей информации:

— микропрограмма, соответствующая заданному алгоритму управления;

— значения вероятностей логических условий;

— параметры модуля кэш-памяти (архитектурная организация, количество строк и столбцов в блоке данных).

2. Моделирование процесса функционирования КМУУ с кэш-памятью со сбором статистической информации о ситуациях кэш-попаданий и кэш-промахов.

3. Аналитическое определение эффективности различных архитектур кэш-памяти для заданного алгоритма управления.

Конечной задачей проектировщика цифровых систем на базе КМУУ с кэш-памятью является выбор архитектуры модуля кэш-памяти, приемлемого для разрабатываемого проекта. При этом одним из критериев выбора является быстродействие работы схемы устройства управления, в значительной степени определяемое значением вероятности кэш-попаданий. Таким образом, последовательное решение поставленных в настоящей работе задач позволяет решить проблему выбора характеристик и типа архитектуры кэш-памяти для заданной микропрограммы.

6.Принцип работы

Данный раздел описывает типичный кэш данных и некоторые виды кэшей инструкций; TLB может быть устроен сложнее, а кэш инструкций — проще. На диаграмме справа изображены основная и кэш память. Каждая строка — группа ячеек памяти содержит данные, организованные в кэш-линии. Размер каждой кэш-линии может различаться в разных процессорах, но для большинства x86-процессоров он составляет 64 байта. Размер кэш-линии обычно больше размера данных, к которому возможен доступ из одной машинной команды (типичные размеры от 1 до 16 байт). Каждая группа данных в памяти размером в 1 кэш-линию имеет порядковый номер. Для основной памяти этот номер является адресом памяти с отброшенными младшими битами. В кэше каждой кэш-линии дополнительно ставится в соответствие тег, который является адресом продублированных в этой кэш-линии данных в основной памяти.

При доступе процессора в память сначала производится проверка, хранит ли кэш запрашиваемые из памяти данные. Для этого производится сравнение адреса запроса со значениями всех тегов кэша, в которых эти данные могут храниться. Случай совпадения с тегом какой-либо кэш-линии называется попаданием в кэш (англ. cache hit), обратный же случай называется кэш-промахом (англ. cache miss). Попадание в кэш позволяет процессору немедленно произвести чтение или запись данных в кэш-линии с совпавшим тегом. Отношение количества попаданий в кэш к общему количеству запросов к памяти называют рейтингом попаданий (англ. hit rate), оно является мерой эффективности кэша для выбранного алгоритма или программы.

В случае промаха, в кэше выделяется новая запись, в тег которой записывается адрес текущего запроса, а в саму кэш-линию — данные из памяти после их прочтения либо данные для записи в память. Промахи по чтению задерживают исполнение, поскольку они требуют запроса данных в более медленной основной памяти. Промахи по записи могут не давать задержку, поскольку записываемые данные сразу могут быть сохранены в кэше, а запись их в основную память можно произвести в фоновом режиме. Работа кэшей инструкций во многом похожа на вышеприведенный алгоритм работы кэша данных, но для инструкций выполняются только запросы на чтение. Кэши инструкций и данных могут быть разделены для увеличения производительности (принцип, используемый в Гарвардской архитектуре) или объединены для упрощения аппаратной реализации.

Для добавления данных в кэш после кэш-промаха может потребоваться вытеснение (англ. evict) ранее записанных данных. Для выбора замещаемой линейки используется эвристика, называемая политика замещения (англ. replacement policy). Основной проблемой алгоритма является предсказание, какая линейка вероятнее всего не потребуется для последующих операций. Качественные предсказания сложны, и аппаратные кэши используют простые правила, такие как LRU. Пометка некоторых областей памяти как некэшируемых (англ. non cacheable) улучшает производительность за счет запрета кэширования редко используемых данных. Промахи для такой памяти не создают копию данных в кэше.

Рисунок 3 – Работа Кеш памяти

(анимация: 9 кадров, 15 циклов повторения, 107 Кб)

Представление онтологий в виде конечного автомата без выходов позволяет ввести операции на онтологиях. Операции на автоматах означают операции на регулярных языках, которые акцептируются этими автоматами.

При записи данных в кэш должен существовать определенный момент времени, когда они будут записаны в основную память. Это время контролируется политикой записи (англ. write policy). Для кэшей со сквозной записью (англ. write-through), любая запись в кэш приводит к немедленной записи в память. Другой тип кэшей, обратная запись англ. write-back (иногда также называемый copy-back) откладывает запись на более позднее время. В таких кэшах отслеживается состояние кэш линеек еще не сброшенных в память (пометка битом «грязный» англ. dirty). Запись в память производится при вытеснении подобной линейки из кэша. Таким образом, промах в кэше, использующем политику обратной записи, может потребовать двух операций доступа в память, один для сброса состояния старой линейки и другой — для чтения новых данных.Существуют также смешанные политики. Кэш может быть со сквозной записью (англ. write-through), но для уменьшения количества транзакций на шине записи могут временно помещаться в очередь и объединяться друг с другом.

Данные в основной памяти могут изменяться не только процессором, но и периферией, использующей прямой доступ к памяти, или другими процессорами в многопроцессорной системе. Изменение данных приводит к устареванию их копии в кэше (состояние stale). В другой реализации, когда один процессор изменяет данные в кэше, копии этих данных в кэшах других процессоров будут помечены как stale. Для поддержания содержимого нескольких кэшей в актуальном состоянии используется специальный протокол кэш когерентности.

Выводы

Предложен подход к определению наиболее оптимальных характеристик модуля кэш-памяти микрокоманд, обеспечивающих максимальную эффективность его работы в составе устройства управления интеллектуальной системы, на основе компьютерного моделирования. Получены аналитические выражения для определения эффективности модуля кэш-памяти. Сформулированы основные требования к компьютерной имитационно-аналитической модели устройства управления с кэш-памятью. В качестве дальнейших исследований в данном направлении предполагается непосредственная разработка модели и разработка методологии проведения с ее помощью экспериментальных исследований.

Список литературы

1. Баркалов А.А. Синтез устройств управления на программируемых логических устройствах / А.А. Баркалов. — Донецк: ДонНТУ, 2002. — 262 с.

2. Бабаков Р.М. Применение принципов кэширования в композиционных микропрограммных устройствах управления / А.А. Баркалов, С.А. Ковалев, Р.М. Бабаков // Управляющие системы и машины. — 2001. — № 5. — С. 26-33.

3. Бабаков Р.М. Организация композиционных микропрограммных устройств управления с кэш-памятью / С.А. Ковалев, Р.М. Бабаков // Вісник східноукраїнського національного університету ім. Володимира Даля. — 2002. — №8. — С. 123-126.

4. Бабаков Р.М. Кэш-память микрокоманд в композиционных микропрограммных устройствах управления / А.А. Баркалов, С.А. Ковалев, Р.М. Бабаков // Зб. наукових праць ДНТУ. Серія “Інформатика, кібернетика та обчислювальна техніка”. Вип. 70. — Донецьк: ДонДТУ, 2003. — С. 90-97.

5. Бабаков Р.М. Эвристический подход к оптимизации работы кэш-памяти в композиционном микропрограммном устройстве управления / С.А. Ковалев, И.И. Агаркова, Р.М. Бабаков, Д.В. Николаенко // Сборник трудов XVIII международной научно-технической конференции «Машиностроение и техносфера XXI века», г. Севастополь, 12-17 сентября 2011 г. В 4-х томах. — Донецк: ДонНТУ, 2011. Т. 2. — С. 57-61.

6. Агеев М.С. Извлечение значимой информации из web-страниц для индексирования / М.С. Агеев, И.В. Вершинников, Б.В. Добров // «Интернет-Математика-2005»: семинар в рамках Всеросс. науч. конф. RCDL'2005. — 2005. — С. 283-301.

7. Булгаков С.В. Использование кеш памяти для построения инновационных цепочек в системе поддержки инновационной деятельности в регионе / С.В. Булгаков, Ю.А. Загорулько // Труды VI-й Междунар. конференции «Проблемы управления и моделирования в сложных системах». — Самара: Самарский Научный Центр РАН, 2004 — С. 328-333.

8. Овдей О.М. Обзор инструментов инженерии кеш памяти / О.М. Овдей, Г.Ю. Проскудина // Журнал ЭБ. — 2004 — С. 25-26.

9. Бениаминов Е.М. Алгебраические методы в теории баз данных и представлении знаний / Е.М. Бениаминов. — М.: Научный мир, 2003 — 184 с.

10. Бевзов А.Н. Разработка методов автоматического индексирования текстов на естественном языке для информационно-поисковых систем / А.Н. Бевзов // Труды X Всеросс. науч. конф. Электронные библиотеки: перспективные методы и технологии, электронные коллекции — RCDL'2008 — С. 401-404.

11. Королев А.Н. Лингвистическое обеспечение информационно-поисковой системы Excalibur RetrievalWare: Аналитический аспект / А.Н. Королев // материалы конференции «Корпоративные Информационные Системы», 1999. — С.44-47.

Важное замечание

При написании данного реферата магистерская работа еще не завершена. Окончательное завершение: декабрь 2013 год. Полный текст работы и материалы по теме могут быть получены у автора или его руководителя после указанной даты.