Вавринюк Ігор Олегович

Факультет компьютерних наук та технологій

Кафедра систем штучного інтелекту

Спеціальність «Cистеми штучного інтелекту»

Розробка та дослідження моделі хешування інформації в пристроях управління інтелектуальних систем

Науковий керівник: к.т.н., доц. Бабаков Роман Маркович

Реферат з теми випускної роботи

Введення

1. Постановка проблеми.

2. Аналіз літератури.

3. Мета дослідження

4. Постановка завдання дослідження.

5. Рішення завдання і результати досліджень.

6. Принцип роботи.

Висновки

Список літератури

Введення

Одним з важливих чинників що підвищують продуктивність процесора, є наявність кеш-пам'яті, а точніше її обсяг, швидкість доступу і розподіл за рівнями.

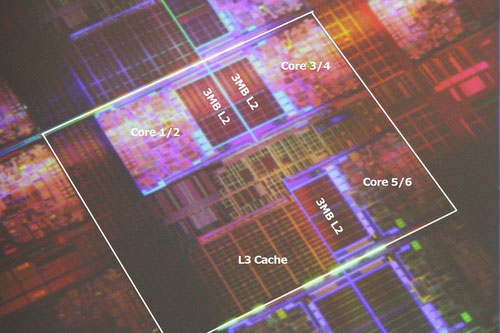

Рис. 1 – Представлення Кеш пам'яти

Вже досить давно практично всі процесори оснащуються даним типом пам'яті, що ще раз доводить корисність її наявності. У даній статті, ми поговоримо про структуру, рівнях і практичному призначенні кеш-пам'яті, як про дуже важливою характеристиці процессора.Кеш-пам'ять - це надшвидка пам'ять використовувана процесором, для тимчасового зберігання даних, які найбільш часто використовуються. Ось так, коротко, можна описати даний тип пам'яті. Вона побудована на тригерах, які, у свою чергу, складаються з транзисторів. Група транзисторів займає набагато більше місця, ніж ті ж самі конденсатори, з яких складається оперативна пам'ять. Це тягне за собою безліч труднощів у виробництві, а також обмеження в обсягах. Саме тому кеш пам'ять є дуже дорогою пам'яттю, при цьому маючи нікчемними обсягами. Але з такої структури, випливає головна перевага такої пам'яті - швидкість. Так як тригери не потребують регенерації, а час затримки вентиля, на яких вони зібрані, невелика, то час перемикання тригера з одного стану в інший відбувається дуже швидко. Це і дозволяє кеш-пам'яті працювати на таких же частотах, що й сучасні процессори.Также, важливим фактором є розміщення кеш-пам'яті. Розміщена вона, на самому кристалі процесора, що значно зменшує час доступу до неї. Раніше, кеш пам'ять деяких рівнів, розміщувалася за межами кристала процесора, на спеціальній мікросхемі SRAM десь на просторах материнської плати. Зараз же, практично у всіх процесорів, кеш-пам'ять розміщена на кристалі процесора.

Рис.2 – Розміщення кеш пам’яті майже в усіх процесорів

1. Постановка проблеми

Алгоритми роботи кеш-пам'яті в сучасних цифрових інтелектуальних системах досить складні. У той же час до ефективності роботи кеш-пам'яті висуваються досить високі вимоги, що обумовлено її відносно високою вартістю у складі цифрового пристрою. Можливість модифікації параметрів модуля кеш-пам'яті дозволяє підібрати такі їх значення, при яких кеш-пам'ять буде володіти максимальною ефективністю для заданої мікропрограми. Подібна оптимізація характеристик модуля кеш-пам'яті дасть можливість поліпшити характеристики цифрового пристрою управління та розширити потенційну область його застосування.

2. Аналіз літератури

У роботі [1] розглянуто питання організації і функціонування цифрового пристрою управління на базі композиційного мікропрограмного пристрою управління, для якого в роботах [2-5] запропоновано методику збільшення швидкодії за рахунок використання модуля кеш-пам'яті мікрокоманд, а також розглянуті питання архітектурної організації модуля кеш -пам'яті. У работак [6-8] розроблено евристичний алгоритм підвищення ефективності використання модуля кеш-пам'яті в композиційному мікропрограмному пристрої керування з розділенням кодів, заснований на спеціальній адресації операторних лінійних ланцюгів. Запропоновано ряд стратегій об'єднання декількох операторних ланцюгів в одному блоці пам'яті, що дозволяє в загальному випадку збільшитизначення ймовірності кеш-попадань для граф-схеми реалізованого алгоритму управленія.Рассмотрен приклад використання запропонованого евристичного алгоритму. Так само в роботі [9] представлений метод синтезу базової структури композиційного мікропрограмного пристрою керування з розділенням кодів і кешуванням мікрокоманд. В основі методу лежить евристичне розподілення операторних лінійних ланцюгів в адресному просторі керуючої пам'яті, що забезпечує максимальне для реалізованого алгоритму керування значення ймовірності кеш-влучень. У джерелах [10-11] розглядається архітектура систем на базі процесорів Intel ® Xeon ® серії 5600 і їх продуктивність. Як і у випадку процесорів серії 5500, архітектура процесорів серії 5600 створює замовлення-чікам певні труднощі внаслідок високої гнучкості і широкого вибору конфігурацій, предлагае-мих цієї нової платформою. Аналіз продуктивності в цьому огляді охоплює такі параметри, як затримки основної пам'яті, пропускна здатність основної пам'яті і продуктивність додатків. Потім в огляді розглядаються аналітичні результати зпопередніх технічних оглядів для серії 5500 і нові аналітичні результати, а також проблеми продуктивності, пов'язані з частотою пам'яті і заповненням роз'ємів пам'яті в конкретній системі. Крім того, в цьому технічному огляді аналізуються оптимальні конфігурації пам'яті, а також викладаються найкращі типові методики та рекомендації щодо конфі-гурірованію відповідних платформ IBM.

3. Мета дослідження

Сформулювати вимоги до розробки комп'ютерної імітаційно-аналітичної моделі кеш-пам'яті мікрокоманд у складі цифрового пристрою управління інтелектуальної системи.

4. Постановка завдання дослідження

У даній роботі вирішується наукова задача побудови комп'ютерної імітаційно-аналітичної моделі модуля кеш-пам'яті, що дозволяє визначити ефективність роботи кеш-пам'яті при заданих параметрах. Для вирішення даної задачі необхідно виконати наступне:

- визначити перелік параметрів модуля кеш-пам'яті, що впливають на величину ефективності;

- отримати аналітичні вирази для визначення ефективності;

- сформулювати основні вимоги до програмної моделі.

5. Рішення завдання і результати досліджень

Кеш-пам'ять використовується для зберігання послідовностей мікрокоманд, які можуть формуватися композиційним мікропрограмним пристроєм управління (КМУУ) найближчим часом. Статистичний аналіз роботи сучасних комп'ютерів показує, що близько 90% всіх даних, запитуваних обчислювальним пристроєм, зазвичай знаходяться в кеш-пам'яті. Ця величина називається коефіцієнтом або ймовірністю кеш-попадання.

Оскільки кеш-пам'ять працює швидше, ніж керуюча пам'ять, яка будується в елементному базисі ПЗУ, можна визначити середній час очікування всієї системи пам'яті (середній час доступу до пам'яті відносно комбінаційної частини КМУУ).

Введемо наступні позначення:

- Ph – ймовірність кеш-влучень;

- tп – час доступу до керуючої пам'яті;

- tc – час пошуку в кеш-пам'яті і вибір необхідних даних у випадку кеш-попадання;

- tm – час доступу до даних у випадку кеш-промаху; при цьому tm = tУП + tп, де tп - так званий час втрат при кеш-промаху, що витрачається на пошук потрібних даних в кеш-пам'яті і приміщення даних з керуючої пам'яті в кеш.

Тоді середній час tе очікування системи пам'яті, що включає в себе кеш-пам'ять, визначається як: Т e = Р * t + (1-P) * tm

З виразу випливає, що для досягнення високої швидкості доступу, близькою до швидкості доступу кеш-пам'яті, буде потрібно частота влучень порядку 90%.

Інший спосіб оцінки ефективності використання кеш-пам'яті складається у визначенні того, наскільки кеш-пам'ять підвищує швидкість доступу до системи пам'яті. Вважаючи, що в загальному випадку tc Вираз наочно показує, що при tУП = tm значення E> 1 при будь-якому Ph> 0, тобто мається постійний виграш у швидкодії. Оскільки tm = tУП + tп, то очевидним є прагнення зменшити tп з метою максимального наближення tm до tУП. Якщо tп >> tc, то при Ph> 0,9 маємо багаторазовий виграш E. Наприклад, при tУП = 200 нс, tc = 10 нс і Ph = 0.9 виграш складе 6.9, тобто майже 700%. На підставі вищесказаного можна зробити висновок, що збільшення виграшу у швидкодії в системі з кеш-пам'яттю в порівнянні з системою без кеш-пам'яті сприяють: - збільшення ймовірності кеш-попадань Ph; - зниження часу втрат при кеш-промаху tп; - зменшення часу доступу до кеш-пам'яті tc.

У виразі величини tс і tп визначаються елементної базою і функціональною організацією апаратури. Конкретні значення цих величин можна визначити, знаючи часи і порядок спрацьовування електронних компонентів схем кеш-пам'яті і кеш-контролера. Найбільш складно визначити значення ймовірності кеш-попадань Ph, оскільки ця величина залежить як від обраних характеристик кеш-пам'яті, так і від реалізованого КМУУ алгоритму управління. При цьому величина Ph може змінюватися на всьому діапазоні ймовірності - від 0 до 1 - і тим самим істотно впливати на ефективність використання кеш-пам'яті в КМПК. Якщо для величин t ¬ с і tm можна легко отримати точні значення, то навіть приблизне визначення значення Ph є скрутним, оскільки ситуації кеш-влучень і кеш-промахів не є очевидними із заданої мікропрограми та характеристик кеш-пам'яті. Для визначення ймовірності кеш-попадань для заданої граф-схеми алгоритму керування і характеристик модуля кеш-пам'яті пропонується виконати комп'ютерне імітаційно-аналітичне моделювання структури КМПК з кеш-пам'яттю для різних параметрів і архітектурних типів модуля кеш-пам'яті. Модель повинна реалізовувати процес функціонування КМУУ і модуля кеш-пам'яті, здійснюючи збір статистичної інформації про ситуації кеш-влучень і кеш-промахів. При цьому обов'язковим є реалізація алгоритмів заміщення даних в модулях кеш-пам'яті. Вихідними даними для визначення ймовірності кеш-попадань Ph будемо вважати: - граф-схему алгоритму управління, інтерпретується схемою КМУУ; - ймовірності переходів по логічним умовам, аналізованих у ДСА; - адресацію мікрокоманд, визначальну розташування мікрокоманд в адресному просторі керуючої пам'яті; - число рядків і слів в кеш-пам'яті. Граф-схему алгоритму будемо вважати перетвореної для реалізації схемою пристрою управління з природною адресацією мікрокоманд. Також будемо вважати, що першою і останньою вершинами в ДСА завжди є операторні вершини (за їх відсутності вони повинні бути додані штучно). Ця умова необхідно для встановлення точок початку і кінця виконання алгоритму управління. Ймовірності переходів логічних умов ми вважаємо відомими тому, що ці значення можуть залежати не тільки від результатів виконання мікрокоманд, а й від зовнішніх факторів (наприклад, від датчиків). Ці значення не можуть бути отримані аналітично, а лише досвідченим шляхом у процесі функціонування КМУУ, що реалізує розглянутий алгоритм, в реальних умовах. Адреси мікрокоманд і розміри кеш-пам'яті є тими факторами, зміна яких може призвести до збільшення або зменшення ймовірності кеш-попадань для заданого алгоритму. Початковий завдання адрес мікрокоманд може бути викликано різними причинами, наприклад, заздалегідь налагодженим алгоритмом зі складними мікропрограмні переходами або реалізованим автоматом з «жорсткою» логікою. Вміст операційних мікрокоманд на етапі визначення ймовірності кеш-попадань не має значення. Дії, що виконуються в них, або ніяк не впливають на процес виконання алгоритму, або впливають на вірогідність переходів ЛУ, які вже вважаються заданими. Тому аналізований алгоритм управління приймає абстрактний характер. Таким чином, сформулюємо основні вимоги до розроблюваної моделі: 1. Використання в якості вихідних даних значень наступної інформації: - мікропрограма, відповідна заданому алгоритму управління; - значення ймовірностей логічних умов; - параметри модуля кеш-пам'яті (архітектурна організація, кількість рядків і стовпців у блоці даних). 2. Моделювання процесу функціонування КМПК з кеш-пам'яттю зі збором статистичної інформації про ситуації кеш-влучень і кеш-промахів. 3. Аналітичне визначення ефективності різних архітектур кеш-пам'яті для заданого алгоритму керування. Кінцевою завданням проектувальника цифрових систем на базі КМПК з кеш-пам'яттю є вибір архітектури модуля кеш-пам'яті, прийнятного для розроблюваного проекту. При цьому одним із критеріїв вибору є швидкодія роботи схеми пристрою керування, в значній мірі визначається значенням ймовірності кеш-влучень. Таким чином, послідовне вирішення поставлених у цій роботі завдань дозволяє вирішити проблему вибору характеристик і типу архітектури кеш-пам'яті для заданої мікропрограми. Даний розділ описує типовий кеш даних і деякі види кешей інструкцій; TLB може бути влаштований складніше, а кеш інструкцій - простіше. На діаграмі справа зображені основна і кеш пам'ять. Кожен рядок - група комірок пам'яті містить дані, організовані в кеш-лінії. Розмір кожної кеш-лінії може відрізнятися в різних процесорах, але для більшості x86-процесорів він становить 64 байти. Розмір кеш-лінії зазвичай більше розміру даних, до якого можливий доступ з однієї машинної команди (типові розміри від 1 до 16 байт). Кожна група даних у пам'яті розміром в 1 кеш-лінію має порядковий номер. Для основної пам'яті цей номер є адресою пам'яті з відкинутими молодшими бітами. У кеші кожної кеш-лінії додатково ставиться у відповідність тег, який є адресою продубльованих в цій кеш-лінії даних в основній пам'яті. При доступі процесора в пам'ять спочатку здійснюється перевірка, чи зберігає кеш запитувані з пам'яті дані. Для цього проводиться порівняння адреси запиту зі значеннями всіх тегів кешу, в яких ці дані можуть зберігатися. Випадок збігу з тегом небудь кеш-лінії називається попаданням в кеш (англ. cache hit), зворотний ж випадок називається кеш-промахом (англ. cache miss). Попадання в кеш дозволяє процесору негайно провести читання або запис даних у кеш-лінії з співпало тегом. Відношення кількості влучень в кеш до загальної кількості запитів до пам'яті називають рейтингом влучень (англ. hit rate), воно є мірою ефективності кешу для обраного алгоритму або програми. У разі промаху, в кеші виділяється нова запис, в тег якій записується адреса поточного запиту, а в саму кеш-лінію - дані з пам'яті після їх прочитання або дані для запису в пам'ять. Промахи з читання затримують виконання, оскільки вони вимагають запиту даних в більш повільною основної пам'яті. Промахи по запису можуть не давати затримку, оскільки записувані дані відразу можуть бути збережені в кеші, а запис їх в основну пам'ять можна справити у фоновому режимі. Робота кешей інструкцій в чому схожа на вищенаведений алгоритм роботи кеша даних, але для інструкцій виконуються тільки запити на читання. Кеші інструкцій і даних можуть бути розділені для збільшення продуктивності (принцип, використовуваний у Гарвардській архітектурі) або об'єднані для спрощення апаратної реалізації. Для додавання даних в кеш після кеш-промаху може знадобитися витіснення (англ. evict) раніше записаних даних. Для вибору замещаемой лінійки використовується евристика, звана політика заміщення (англ. replacement policy). Основною проблемою алгоритму є передбачення, яка лінійка найімовірніше не буде потрібно для подальших операцій. Якісні передбачення складні, і апаратні кеші використовують прості правила, такі як LRU. Позначка деяких областей пам'яті як некешіруемих (англ. non cacheable) покращує продуктивність за рахунок заборони кешування рідко використовуваних даних. Промахи для такої пам'яті не створюють копію даних в кеші. Рисунок 3 - Робота Кеш пам'яті Представлення онтологій у вигляді кінцевого автомата без виходів дозволяє ввести операції на онтологіях. Операції на автоматах означають операції на регулярних мовах, які акцептуються цими автоматами. При запису даних у кеш повинен існувати певний момент часу, коли вони будуть записані в основну пам'ять. Це час контролюється політикою запису (англ. write policy). Для кешей з наскрізною записом (англ. write-through), будь-який запис в кеш призводить до негайної запису в пам'ять. Інший тип кешей, зворотній запис англ. write-back (іноді також званий copy-back) відкладає запис на пізніший час. У таких кешах відстежується стан кеш лінійок ще скинутих в пам'ять (позначка бітом «брудний» англ. Dirty). Запис в пам'ять проводиться при витіснення подібної лінійки з кеша. Таким чином, промах в кеші, использующем політику зворотного запису, може зажадати двох операцій доступу в пам'ять, один для скидання стану старої лінійки і інший - для читання нових данних.Существуют також змішані політики. Кеш може бути з наскрізною записом (англ. write-through), але для зменшення кількості транзакцій на шині записи можуть тимчасово міститися в чергу і об'єднуватися один з одним. Дані в основній пам'яті можуть змінюватися не тільки процесором, але і периферією, що використовує прямий доступ до пам'яті, або іншими процесорами в багатопроцесорної системі. Зміна даних приводить до старіння їх копії в кеші (стан stale). В іншій реалізації, коли один процесор змінює дані в кеші, копії цих даних в кешах інших процесорів будуть позначені як stale. Для підтримки вмісту декількох кешей в актуальному стані використовується спеціальний протокол кеш когерентності. Запропоновано підхід до визначення найбільш оптимальних характеристик модуля кеш-пам'яті мікрокоманд, що забезпечують максимальну ефективність його роботи у складі пристрою управління інтелектуальної системи, на основі комп'ютерного моделювання. Отримано аналітичні вирази для визначення ефективності модуля кеш-пам'яті. Сформульовано основні вимоги до комп'ютерної імітаційно-аналітичної моделі пристрою керування з кеш-пам'яттю. В якості подальших досліджень у даному напрямку передбачається безпосередня розробка моделі і розробка методології проведення з її допомогою експериментальних досліджень. 1. Баркалов А.А. Синтез устройств управления на программируемых логических устройствах / А.А. Баркалов. — Донецк: ДонНТУ, 2002. — 262 с. 2. Бабаков Р.М. Применение принципов кэширования в композиционных микропрограммных устройствах управления / А.А. Баркалов, С.А. Ковалев, Р.М. Бабаков // Управляющие системы и машины. — 2001. — № 5. — С. 26-33. 3. Бабаков Р.М. Организация композиционных микропрограммных устройств управления с кэш-памятью / С.А. Ковалев, Р.М. Бабаков // Вісник східноукраїнського національного університету ім. Володимира Даля. — 2002. — №8. — С. 123-126. 4. Бабаков Р.М. Кэш-память микрокоманд в композиционных микропрограммных устройствах управления / А.А. Баркалов, С.А. Ковалев, Р.М. Бабаков // Зб. наукових праць ДНТУ. Серія “Інформатика, кібернетика та обчислювальна техніка”. Вип. 70. — Донецьк: ДонДТУ, 2003. — С. 90-97. 5. Бабаков Р.М. Эвристический подход к оптимизации работы кэш-памяти в композиционном микропрограммном устройстве управления / С.А. Ковалев, И.И. Агаркова, Р.М. Бабаков, Д.В. Николаенко // Сборник трудов XVIII международной научно-технической конференции «Машиностроение и техносфера XXI века», г. Севастополь, 12-17 сентября 2011 г. В 4-х томах. — Донецк: ДонНТУ, 2011. Т. 2. — С. 57-61. 6. Агеев М.С. Извлечение значимой информации из web-страниц для индексирования / М.С. Агеев, И.В. Вершинников, Б.В. Добров // «Интернет-Математика-2005»: семинар в рамках Всеросс. науч. конф. RCDL'2005. — 2005. — С. 283-301. 7. Булгаков С.В. Использование кеш памяти для построения инновационных цепочек в системе поддержки инновационной деятельности в регионе / С.В. Булгаков, Ю.А. Загорулько // Труды VI-й Междунар. конференции «Проблемы управления и моделирования в сложных системах». — Самара: Самарский Научный Центр РАН, 2004 — С. 328-333. 8. Овдей О.М. Обзор инструментов инженерии кеш памяти / О.М. Овдей, Г.Ю. Проскудина // Журнал ЭБ. — 2004 — С. 25-26. 9. Бениаминов Е.М. Алгебраические методы в теории баз данных и представлении знаний / Е.М. Бениаминов. — М.: Научный мир, 2003 — 184 с. 10. Бевзов А.Н. Разработка методов автоматического индексирования текстов на естественном языке для информационно-поисковых систем / А.Н. Бевзов // Труды X Всеросс. науч. конф. Электронные библиотеки: перспективные методы и технологии, электронные коллекции — RCDL'2008 — С. 401-404. 11. Королев А.Н. Лингвистическое обеспечение информационно-поисковой системы Excalibur RetrievalWare: Аналитический аспект / А.Н. Королев // материалы конференции «Корпоративные Информационные Системы», 1999. — С.44-47. Важливе зауваження При написанні даного реферату магістерська робота ще не завершена. Остаточне завершення: грудень 2013 рік. Повний текст роботи та матеріали по темі можуть бути отримані у автора або його керівника після вказаної дати.6.Принцип роботи

(анімація: 9 кадрів, 15 циклів повторення, 107 Кб) Висновки

Список літератури