Специальность: Системный программист

Тема магистерской работы:

"Разработка и исследование методов тестирования FPGA-устройства с использованием технологии Boundary-Scan"

Научный руководитель: Зинченко Юрий Евгениевич

Реферат по теме

"Разработка и исследование методов тестирования FPGA-устройства с использованием технологии Boundary-Scan"

Введение

Со времён появления интегральных схем (ИС) в США 1959г. возникла проблема их диагностики не только в процессе эксплуатации, но и на этапе непосредственно разработки. При том, как ИС постоянно совершенствовались и усложнялись, они требовали к себе большевнимания со стороны поиска в них неисправностей. С появлением БИС и СБИС схемы с тысячами логических элементов стали размещаться на одном кристалле, поэтому доступа к схемам для контактной диагностики становилось меньше.

Актуальность темы

В диагностике существует множество методов контактного тестирования ИС, но ни один из них не позволяет диагностировать ИС, которые скрыты от зрения разработчика. Технология безконтактного сканирования boundary-scan позволяет тестировать ИС недоступные физически, достигая при этом высокого тестового покрытия, при условии, что тестируемая ИС будет тестопригодной, т.е. удовлетворять стандарту IEEE 1149.

Практическая новизна

Рассмотрен механизм Boundary-Scan, который соответствует цифровому стандарту IEEE 1149.1 для тестирования БИС и СБИС. Представлен краткий обзор программно-аппаратых комплексов некоторых фирм, предназначенных для тестирования интегральных схем, поддерживающих технологию Boundary-Scan.

Основное содержание работы

Функциональное тестирование появилось самым первым. На заре электронной промышленности большинство систем просто собиралось, а затем подключалось питание. Тест осуществлялся путем проверки работоспособности изделия. Постоянное увеличение сложности изделий делают процесс подготовки функционального теста бесконечно долгим. Диагностирование неисправностей, обнаруженных в процессе функционального тестирования, может быть достаточно сложным, требующим привлечения квалифицированных специалистов. Поэтому перед тестом системы в целом часто осуществляется тестирование на уровне отдельных плат. Тест плат может быть осуществлен и на функциональном уровне, но разделение делает диагностирование неисправностей и подготовку тестов более гибкими. Быстро растущая сложность интегральных микросхем вызывает похожие проблемы с функциональным тестированием на уровне плат, так же как и в системном тестировании — долгое время подготовки тестов, неточное тестовое покрытие, слабая диагностика.

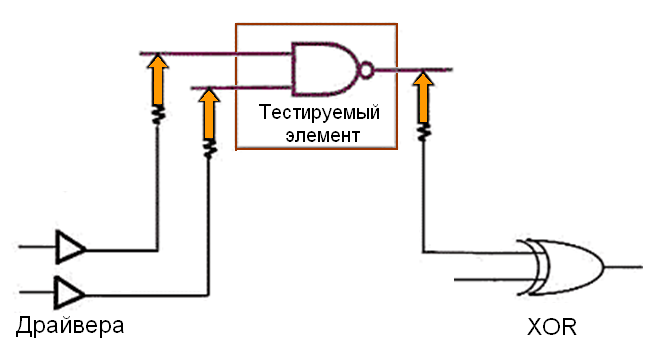

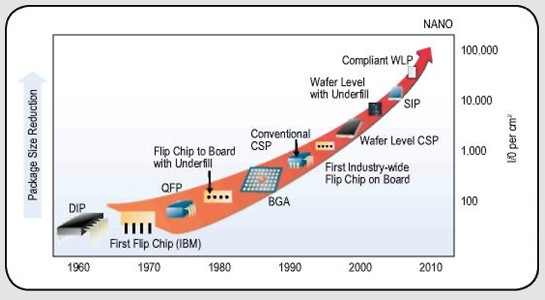

Следующий широко распространенный метод тестирования — это внутрисхемное тестирование (In-Circuit Test, ICT). Этот метод позволяет находить дефекты и ошибки монтажа путем обеспечения прямого электрического доступа к компонентам на плате через адаптер игольчатого типа (рисунок 1). Внутрисхемное тестирование идеально подходило для DIP-компонентов и технологии штыревого монтажа. Но в связи с появлением многослойных печатных плат и более сложных корпусов микросхем, таких как QFP, BGA, CSP и т.д., тестовый доступ стал сильно ограничен. Технология внутрисхемного тестирования не может развиваться также быстро, как миниатюризация размеров компонентов и изделий.

Рисунок 1 – пример внутрисхемного тестирования

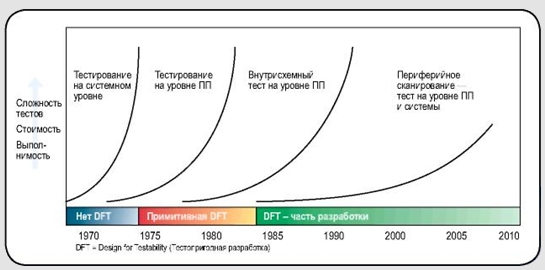

Электронная индустрия предвидела эти проблемы заранее, поэтому был разработан метод периферийного сканирования, закрепленный стандартом IEEE 1149.1, который описывает порт тестового доступа (TAP — Test Access Port) и архитектуру периферийного сканирования. Целью создания данного стандарта было преодоление недостатков других методов тестирования (рисунок 2).

Рисунок 2 – Возрастание важности стратегии тестопригодной разработки изделий

Глядя на эволюцию тестовых методов (рисунок 3) можно сделать следующие наблюдения:

-

Разработка тестопригодных изделий (Design-For-Test, DFT) становится все более

и более необходимым дополнением функционального тестирования, позволяя

сделать контроль более полным и информативным. Для того чтобы производить и тестировать современные передовые разработки, тестопригодность необходима. -

Изначально, тестирование было производной процесса отладки новой разработки и поиска дефектов монтажа. Из-за роста сложности схем устройств управляемость этими процессами могла быть повышена только при раздельном их проведении. Обнаружение и исправление производственных дефектов на стадии отладки опытных образцов стало необходимостью.

-

С ростом сложности продукции многие производители начали применять многоступенчатую стратегию тестирования, целью применения которой является как можно более раннее обнаружение и исправление ошибок производственного процесса.

Рисунок 3 – Эволюция ИС

Первая версия стандарта тестирования устройств с ограниченным доступом к выводам интегральной схемы - Boundary-Scan, появилась вначале 1990 года, и получила имя, которое сохранилось и сегодня - IEEE 1149.1. Стандарт этой технология также называется Test Access Port and Boundary-Scan Architecture (порт тестового доступа и архитектура граничного сканирования). Проект был разработан международной группой экспертов, которая носила название JTAG (Joint Test Action Group — объединенная группа разработки методов тестирования), поэтому стандарт технологии граничного сканирования более известен под названием этой аббревиатуры[4].

Сама архитектура цифрового стандарт Boundary-Scan не отличается особой сложностью, в отличии от своих возможностей. Согласно стандарту IEEE 1149.1, так называемая Boundary-Scan-ИС, должна быть оснащена четырьмя обязательными элементами:

- TAP-портом, который составляют четыре обязательных сигналов, и пятый по усмотрению разработчиков непосредственно самой платы (TCK – контакт синхронизации работы механизма Boundary-Scan; TMS – контакт выбора тестового режима; TDI – контакт ввода тестовых данных; TDO – контакт вывода тестовых данных (находится в постоянно в третьем состоянии, кроме режима сдвига) ; /TRST – контакт асинхронного сброса состояния TAP-контроллера (может совсем не пресутствовать)).

- TAP-контроллер выступает одним из важных элементов управления всей работы технологии Boundary-Scan;

- IR (Instruktion Register от анг. – Регистр Команд) – первая группа регистров, в которой обязательным по стандарту должен присутствовать хотя бы один Регистр Команд (РК);

- DR (Data Registers от анг. – Регистры Данных) – вторая группа регистров, согласно стандарту обязана в себя включать как минимум два регистра: Регистр Обхода (РО, также его иногда называют Шунт-Регистр), Регистр Boundary-Scan.

Такой минимальный комплект элементов требует стандарт IEEE 1149.1. Остальные регистры, которые могут дополнить группу, как IR, так DR по усмотрению разработчиков плат, также допускаются созданным стандартом[2][3].

Для того, чтобы получить хорошее тестовое покрытие, нет необходимости в том, чтобы все компоненты на плате имели JTAG-интерфейс. Например, много блоков, состоящих из не сканируемых компонентов (кластера), могут тестироваться, несмотря на отсутствие прямого доступа для периферийного сканирования. В действительности, существуют практические примеры, когда осуществляется контроль и детальное тестирование абсолютно всей платы (включая память) при помощи одного или двух компонентов, поддерживающих периферийное сканирование.

На рисунке 4 изображена архитектура Boundary-Scan. На TAP-контроллер подаются 2(3) сигнала, при помощи которых контроллер устанавливает соответствующий режим работы схемы. Сам TAP-контроллер представляет собой автомат с конечным количеством вершин. В этой статье его работа не будет подробно рассматриваться.

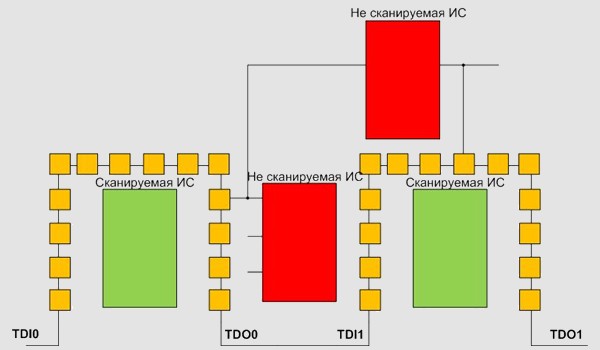

Основной принцип работы Boundary-Scan заключается в том, что вокруг ИС на этапе разработки располагаются ячейки Boundary-Scan, из которых состоит один из обязательных регистров данных – Регистр Boundary-Scan. Ячейки Boundary-Scan расположены непосредственно между внешними выводами и функциональным ядром ИС. ИС, окружённые такой конструкцией называют соответствующими стандарту IEEE 1149.1 и подлежат тестированию с помощью технологии Boundary-Scan. Также необходимо, чтобы каждый предыдущий тестовый выход TDO соединялся со следующим тестовым входом TDI, т.о. цепочка Регистров Boundary-Scan всех сканируемых ИС будет непрерывной. Идеальным вариантом является то, когда все ИС, расположенные на плате, поддерживают этот стандарт. Но если это так, то приходится прибегать к внутрисхемному тестированию для тестирования, так называемых, не сканируемых ИС.

Рисунок 4 – Анимация (15 кадров, 7 циклов повторения, 309 Кб). Архитектура технологии Boundary-Scan

Одним из распространённых подходов тестирования подобных рассмотренным платам (рисунок 5) является принцип «Разделяй и властвуй». [1] Т.е. все компоненты, расположенные на плате, разделяются на отдельные островки, которые будут отдельно друг от друга тестироваться. Не сканируемые ИС, внешние выводы которых соединены со сканируемыми, условно отделяются и называются кластерами. Сам же процесс сканирования начинается проверки целостности самого пути сканирования, далее одним из этапов тестирования может быть тестирование соединений между ИС и соединений с памятью, затем тестируются кластера, на которые подаются тесты, а с их выходов фиксируется реакция.

Рисунок 5 – Плата с не сканируемыми ИС

Для максимального использования всех привилегий Boundary-Scan требуется надёжная разработка программного обеспечения, а также вспомогательное аппаратное обеспечение.

Сегодня на мировом рынке в этой области лидируют четыре представителя США и Европы, которые поставляют программно-аппаратные комплексы (ASSET InterTech Inc. и CORELIS Inc – США; GOEPEL Electronic – Германия; JTAG Technologies – Нидерланды). Такие разработки называются BS-тестеры.[1]

Вот ряд программно-аппаратных комплексов, которые заслуживают доверие своих пользователей:

- ScanWorks фирмы Asset InterTech

- ScanExpress фирмы Corelis

- ProVision фирмы JTAG Technologies

- onTAP фирмы Flynn Systems

- XJTAG фирмы XJTAG

- SourceWizard и ScanMaster фирмы Acculogic

Различия между системами относятся в средствах разработки тестов и их отладки, удобству и эффективности поиска дефектов по результатам получаемой диагностики неисправностей, средствами анализа уровня тестопригодности и полноты покрытия неисправностей:

- автоматизация разработки тестов;

- способы интегрированности графического интерфейса пользователя;

- совместимость интерфейса прикладного программирования с различными языками программирования (С/С++, Tcl/Tk, Perl, Visual Basic, J#);

- поддержка расположенных в интернете библиотек тестовых модулей.

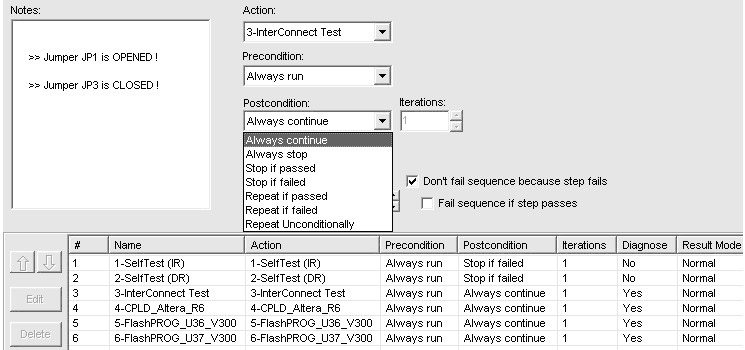

Программно-аппаратная система ScanWorks техасской фирмы Asset InterTech завоевала себе огромную популярность, в наибольшей степени — в США и на Дальнем Востоке. Эта система имеет единый, интегрированный GUI, посредством которого осуществляется конфигурирование ее характеристик, выбор ограничений и параметров тестов, выбор BS-команд контроллера ТАР, поиск и адаптация применяемых моделей кластеров, ЗУ, флэш-памяти. Все, что требуется тест-инженеру в процессе разработки теста, его отладки, прогона, получения диагностической информации и поиска дефектов достижимо посредством связанных между собой окон GUI.

Рисунок 6 – секвенсер ScanWorks

Программно-аппаратный комплекс поддержки BoundaryScan ScanExpress калифорнийской фирмы Corelis широко известна и применяется при тестировании электронных плат в США, Европе, Израиле, Индии и на Дальнем Востоке. Конфигурирование основных характеристик системы, выбор ограничений и параметров тестов, выбор BS-команд контроллеров ТАР, поиск и адаптация применяемых моделей кластеров, ЗУ осуществляется как с использованием GUI, так и редактированием соответствующих текстовых файлов. GUI системы интегрирован частично.

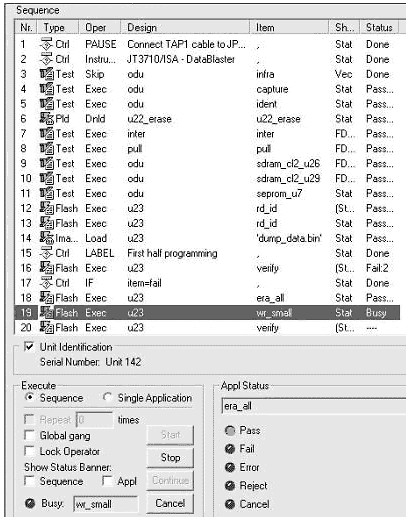

Программно-аппаратная система ProVision голландской фирмы JTAGTechnologies представляет собой интегрированный GUI, сопровождающий проект от загрузки списка линий тестируемой платы и файлов BSDL до генерации загружаемых в AEX Manager файлов APL для запуска результирующей тестовой последовательности. Стандартный тест инфраструктуры BS-цепочки генерируется автоматически при генерации аппликаций для тестов межэлементных связей, а также тестов подтягивающих резисторов и резисторов, подключенных «на массу». В дополнение к этому, ProVision обеспечивает генерацию аппликаций для тестирования библиотечных кластеров ЗУ и кластеров, определяемых пользователем, а также генерацию программ прожига ИС флэш-памяти и процедур внутрисхемного программирования на основе файлов внутрисхемного программирования, импортированных из других систем

Рисунок 7 – секвенсер AEX Manager

Система onTAP фирмы Flynn Systems за короткий промежуток вырвалась на рынок гигантов и заняла своё место наравне с ними. Эта система обладает отличной совместимостью с другими средствами для тестирования, благодаря тому, что выходной формат любого теста, выходящего из неё, имеет повсеместно используемый формат SVF.

Система onTAP имеет удобный графический интерфейс пользователя. Навигация происходит с помощью пяти кнопок управления (рисунок 8).

Рисунок 8 – Пять основных кнопок управления

BS-тестер onTAP включает в себя все необходимые средства для граничного сканирования, начиная от разработки тестов до прогона тестов на производственной линии:

- система генерации тестов (Developer);

- секвенсер тестовых этапов (Тest);

- браузер линий схемы и контактов элементов (Nets);

- окно отладки теста (Waveforms);

- окно прогона тестов на производственной линии (Mfg Test).

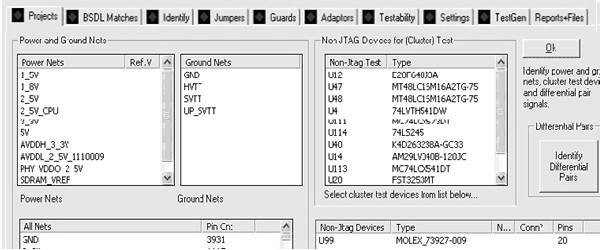

При нажатии на кнопку D(Developer) пользователю открывается окно разработки теста (рисунок 9). Система onTAP для разработки теста предлагает создать проект, к которому потребуется только добавить некоторые файлы с информацией о тестируемой плате, и самое основное, что требуется от разработчика теста – это хорошее знание в области логики работы самого тестируемого устройства.

Рисунок 9 – Диалоговое окно разработки теста

Перелистывая поочерёдно вкладки, происходит поэтапная разработка теста, если очередной этап правильно завершён, то кранная иконка вверху рядом с названием подокна подсвечивается зелёным цветом. Т.о. система помогает избежать множество ошибок. Среди этих вкладок присутствует браузер внутренних связей, который позволяет объявлять линии схемы питания и земли. Это приводит к автоматической сортировке резисторов на подтягивающие резисторы и резисторы, подключенные «на массу», а также на BS-прозрачные резисторы. Кроме того, этот браузер позволяет отобрать компоненты не относящиеся к граничному сканированию, предназначенные для кластерного. В этом же окне выбираются ИС ЗУ, предназначенные для тестирования, а также ИС флэш-памяти и ЭСППЗУ.

В браузере Jumpers выполняется сшивка указываемых нескольких линий схемы в одну для случаев, не отраженных в списке линий тестируемой платы.[2]

Браузер ограничений Guards — это весьма дружественный интерфейс выбора внутрисхемных ограничений и условий при разработке тестов. [2]

Компоненты, предназначенные для кластерного тестирования, а также ИС ЗУ, флэш-памяти и ЭСППЗУ ставятся в соответствие своим моделям на последней странице генерации теста граничного сканирования.

Отличительной особенностью системы onTAP является наличие в ней детально структурированного языка тестового программирования DTS (Digital Test Syntax). Этот С-образный язык программирования позволяет манипулировать переменными, функциями и конструкциями из групп контактов с целью разработки библиотечных моделей для кластерного BS-тестирования компонент, а также тестирования ИС ЗУ и прожига ИС флэш-памяти и ЭСППЗУ. Библиотечные DTS-модели наиболее применимых компонент доступны через интернет и могут быть модифицированы в соответствии со спецификой тестируемой платы.[3]

Выводы

Boundary-Scan было изобретено для того, чтобы преодолеть проблемы с ограниченным доступом, возникающие при использовании внутрисхемного тестирования плат, изготовленных с применением технологии поверхностного монтажа.

Технология Boundary-Scan цифрового стандарта IEEE 1149.1 легко завоевала своё место в мире, продолжая при этом активно развиться. Для современных больших интегральных схем пока не найдено способа диагностирования с более высоким тестовым покрытием. Представленный в статье анализ и сравнения программно-аппаратных комплексов для создания тестов, их отладки и непосредственно тестирования плат через интерфейс JTAG, даёт возможность ценить основные преимущества и недостатки приведенного программного обеспечения.

Обзор набора инструментов в данной статье знакомит с понятиями, терминами и возможностями работы механизма бесконтактного тестирования плат соответствующих цифровому стандарту IEEE 1149.1.

Промышленное тестирование не является единственным применением последовательной шины сканирования и TAP-порта. Из-за простоты доступа в целях тестирования и легкости разработки тестов Boundary-Scan часто и вполне успешно используется для тестирования опытных образцов и выявления производственных дефектов.

В дополнение к тестированию, JTAG-инфраструктура может использоваться также для программирования флэш-памяти и ПЛИС уже после сборки платы. Успешное программирование флэш требует доступ к шинам адреса и данных, а также контрольным выводам микросхемы памяти через ячейки периферийного сканирования.

Поскольку Boundary-Scan не нуждается в сложном подходе к себе и при наличии платы, соответствующей JTAG-стандарту, применение этой технологии не вызывает затруднений, то её не составит труда внедрить, как для изучения студентами на кафедре университета, так и для отладки и тестирования проектов, разрабатываемых самим университетом.

Литература

1. В. Рустинов, А. Городецкий «"РАЗДЕЛЯЙ И ВЛАСТВУЙ" – принцип граничного сканирования»

2. Городецкий A., Курилан Л. «Системы поддержки граничного сканирования ProVision и onTAP», «Производство электроники» 2008, № 3.

3. Городецкий A., Курилан Л. «Введению в технологию граничного сканирования», «Производство электроники» 2007, № 5.

4. Угрюмов Е.П. Цифровая схемотехника. — СПб.: БХВ – Санкт-Петербург. — 2000. — 528 с.: ил.