1. Вступ

2. Загальні поняття

3. Класифікація оперативної пам'яті

3.1 Статичні оперативні запам'ятовуючі пристрої

3.2 Динамічні оперативні запам'ятовуючі пристрої

4. Організація основної пам'яті

4.1 Організація ОП на основі блокової схеми

4.2 Організація ОП на основі блокової схеми з чергуванням

адрес за циклічною схемою

4.3 Організація ОП на основі блокової схеми з

блочно-циклічною схемою розшарування

Висновки

Література

Важливе зауваження

1. Вступ

Обчислювальний напрямок застосування комп'ютерів завжди залишався основним двигуном прогресу

в комп'ютерних технологіях. В якості основної характеристики

комп'ютерів використовується такий показник, як продуктивність — величина, що показує,

яка кількість арифметичних операцій він може виконати за одиницю часу.

Саме продуктивність з найбільшою очевидністю демонструє масштаби прогресу,

досягнутого в комп'ютерних технологіях.

У будь-якій обчислювальній машині (ОМ), незалежно від її архітектури, програми і дані

зберігаються в пам'яті.

Функції пам'яті забезпечуються запам'ятовуючими пристроями (ЗП), призначеними для фіксації,

зберігання та видачі інформації в процесі роботи ОМ.

Тема аналізу функціонування основної пам'яті з блочно-циклічною схемою розшарування

є актуальною в наш час, адже блочна побудова пам'яті володіє такими важливими

перевагами, як скорочення часу доступу до інформації та податливість до нарощування ємності.

Це можливо завдяки потенційному паралелізму,

властивому блоковій організації. Більшої швидкості доступу можна досягти за рахунок одночасного

доступу до багатьох банків пам'яті.

Мета роботи полягає в аналізі функціонування основної пам'яті з

блочно-циклічною схемою розшарування.

Можна виділити наступні завдання магістерської роботи:

- Огляд методів аналізу функціонування основної пам'яті

- Побудова і реалізація марковських моделей основної пам'яті з блочно-циклічною схемою розшарування

- Проведення аналізу основної пам'яті на основі блокової схеми

- Аналіз основної пам'яті з чергуванням адрес за циклічною схемою

- Аналіз основної пам'яті з блочно-циклічною схемою розшарування

Плановані практичні результати полягають у виробленні рекомендацій щодо організації

обсягів банків і блоків у залежності від критеріїв надійності або швидкості.

Наукова новизна полягає у розробці та реалізації марковських моделей основної пам'яті

з блочно-циклічною схемою розшарування.

2. Загальні поняття

Основна пам'ять (ОП) — це єдиний вид пам'яті, до якої може безпосередньо

звертатися ЦП (за винятком регістрів центрального процесора). Після того, як інформація, що

зберігається на зовнішніх ЗУ, буде переписана в основну пам'ять, вона стає доступною процесору.

ОП складається з запам'ятовуючих пристроїв з довільним доступом. Такі пристрої

організуються як масив комірок. Кожна комірка має унікальну адресу і містить фіксоване

число запам'ятовуючих елементів. Унікальна адреса дозволяє розрізняти комірки при зверненні до

них для виконання операцій зчитування та запису.

Звернення до будь-якої комірки займає однакову кількість часу та може виконуватися в довільній

послідовності ("довільний доступ").

3. Класифікація оперативної пам'яті

Основна пам'ять може включати в себе два типи пристроїв:

• постійні запам'ятовуючі пристрої (ПЗП)

• оперативні запам'ятовуючі пристрої (ОЗП)

1) Постійні запам'ятовуючі пристрої (ПЗП)

Меншу частку основної пам'яті утворюють ПЗП (ROM — Read-Only Memory).

На відміну від ОЗП, вони забезпечують зчитування інформації, але не допускають

її зміни (існує ряд випадків, коли інформація в ПЗП може бути змінена,

але цей процес відрізняється від прочитування і вимагає значно більшого часу).

Мікросхеми ПЗП є енергонезалежними.

2) Оперативні запам'ятовуючі пристрої (ОЗП)

Велику частину основної пам'яті утворюють ОЗП (RAM — Random Access Memory, пам'ять з

довільним доступом), звані оперативними, тому що допускають однотипне,

вироблене практично з однією і тією ж швидкістю, виконання операцій запису і

зчитування інформації (за допомогою електричних сигналів).

Але слід враховувати, що мікросхема ОЗП може використовуватися тільки як тимчасова пам'ять,

тому що повинна бути постійно підключена до джерела живлення.

Існує два основних типи пам'яті з довільним доступом:

• статична (SRAM — Static RAM)

• динамічна (DRAM — Dynamic RAM)

Розглянемо їх докладніше.

3.1 Статичні оперативні запам'ятовуючі пристрої

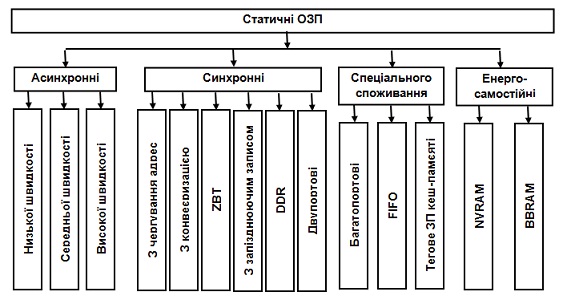

Статичні ОЗП — це найбільш швидкий, правда, і найбільш дорогий вид оперативної пам'яті. Виділяється безліч різних варіантів реалізації SRAM, що відрізняються за технологією, способами організації та сферою застосування (рис. 1).

Рисунок 1 — Види статичних ОЗП

Асинхронні статичні ОЗП.

Асинхронні статичні ОЗП застосовувалися в кеш-пам'яті другого рівня протягом багатьох років

(з моменту появи мікропроцесора i80386). Для таких ІМС час доступу становило 12-20 нс,

що не дозволяло кеш-пам'яті другого рівня працювати в темпі процесора.

Синхронні статичні ОЗП.

У рамках даної групи статичних ОЗП виділяють ІМС типу SSRAM і РМ SRAM (більш досконалі).

У порівнянні з асинхронними статичними ОЗП, значно кращі показники досягнуті в

синхронних SRAM (SSRAM). Всі події в SSRAM відбуваються з надходженням зовнішніх тактових імпульсів.

Відмінною особливістю SSRAM є вхідні регістри, де фіксується вхідна інформація.

Останні модифікації мікропроцесорів Pentium, починаючи з Pentium II,

оснащуються статичною оперативною пам'яттю з пакетним конвеєрним доступом

(РВ SRAM — Pipelined Burst SRAM), замсість SSRAM. За рахунок внутрішньої конвеєризації у РВ SRAM,

швидкість обміну пакетами даних зростає приблизно вдвічі. Пам'ять даного типу добре працює

при підвищених частотах системної шини. Час доступу до РВ SRAM складає від 4,5 до 8 нс.

3.2 Динамічні оперативні запам'ятовуючі пристрої

Саме DRAM використовується в якості основної пам'яті ОМ, отже, динамічної пам'яті в

обчислювальної машині значно більше, ніж статичної.

Як і SRAM, динамічна пам'ять складається з ядра (масиву ЗЕ) і інтерфейсної логіки

(буферних регістрів, підсилювачів читання даних, схеми регенерації та ін.) Кількість видів

DRAM вже перевищила два десятки, проте ядро в них організовано практично однаково, головні

відмінності пов'язані з інтерфейсною логікою (також, вони зумовлені і областю застосування мікросхем).

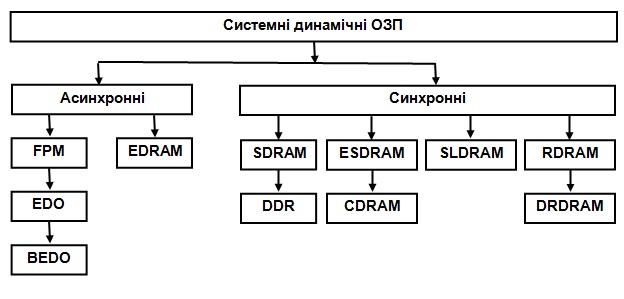

Класифікацію мікросхем динамічної пам'яті показано на рис. 2.

Рисунок 2 — Класифікація динамічних ОЗП. Мікросхеми для основної пам'яті

4. Організація основної пам'яті

Для реалізації основної пам'яті використовують об'єднання декількох інтегральних мікросхем (ІМС, ICs — Integrated Circuits).

Причиною об'єднання є велика ємність ОП та перевищення розрядності слів ОМ

розрядності осередків мікросхеми ЗП.

Збільшення розрядності ЗП реалізується за рахунок об'єднання адресних входів ІМС ЗП, що об'єднуються.

Інформаційні входи і виходи мікросхем є входами і виходами модуля ЗП збільшеної розрядності (рис. 3).

Сукупність мікросхем називають модулем пам'яті. Один або декілька модулів утворюють банк пам'яті.

Рисунок 3 — Збільшення розрядності пам'яті (анімація: об'єм — 40.8 КБ, кількість кадрів — 6, кількість повторiв — 7, розмір — 559 х 280)

Для отримання необхідної ємності ЗП необхідно певним чином об'єднати кілька банків

пам'яті меншої ємності. У загальному випадку основна пам'ять ОМ практично завжди має блочну структуру

(містить кілька банків).

При використанні блочної пам'яті, яка складається з В банків, адреса комірки А перетворюється в

пару (b, w), де b — номер банку, w — адреса комірки усередині банку.

Схеми розподілу розрядів адреси А між b і w:

• блокова (номер банку b визначає старші розряди адреси);

• циклічна (b=A mod В; w = A div В);

• блочно-циклічна (комбінація двох попередніх схем).

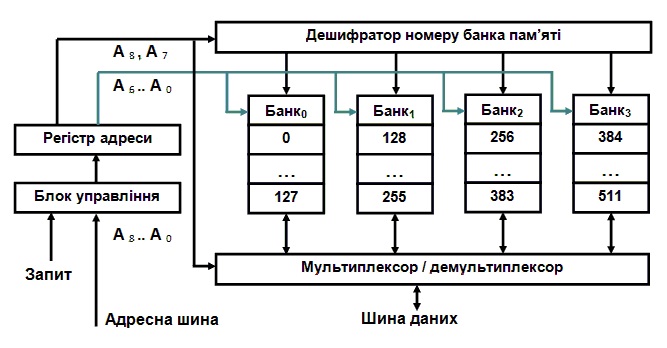

4.1 Організація ОП на основі блокової схеми

Розгляд основних структур блокової ОП проведемо на прикладі пам'яті ємністю 512 слів, побудованої з чотирьох банків з 128 слів в кожному. Структура пам'яті, організована відповідно до розглянутої структури, що показана на рис. 4.

Рисунок 4 — Структура основної пам'яті на основі блокової схеми

Адресний простір пам'яті розбивається на групи адрес (послідовних),

кожна така група забезпечується окремим банком пам'яті.

Для звернення до ОП використовується 9-розрядна адреса. Сім молодших розрядів (А6-А0)

надходять паралельно на всі банки пам'яті та обирають в кожному з них одну клітинку.

Два старших розряди адреси (А8, А7) містять номер банку.

Вибір банку забезпечується або шляхом мультиплексування інформації, або з

допомогою дешифратора номера банку.

У функціональному відношенні, така ОП може розглядатися як єдине ЗП,

ємність якого дорівнює сумарній місткості складових, а швидкодія - швидкодії окремого банку [1].

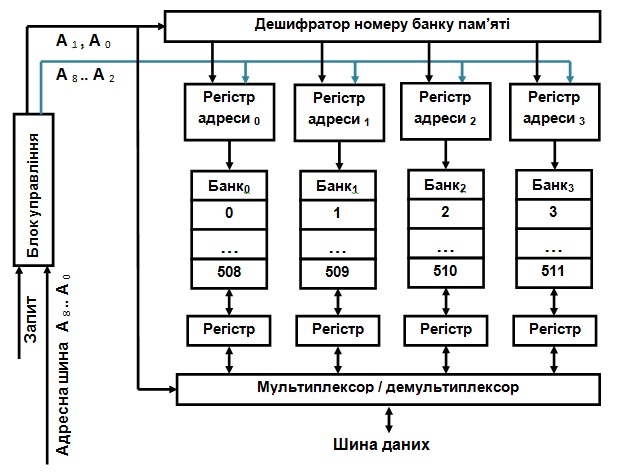

4.2 Організація ОП на основі блокової схеми з чергуванням адрес за циклічною схемою

До переваг блокової пам'яті можна віднести нарощування ємності і скорочення часу

доступу до інформації завдяки потенційному паралелізму.

Швидкість доступу збільшується за рахунок одночасного доступу до багатьох банків пам'яті.

Одна з використовуваних для цього методик називається розшаруванням пам'яті. В її основі лежить так

зване чергування адрес (address interleaving), що полягає у зміні системи

розподілу адрес між банками пам'яті.

Чергування адрес забезпечується за рахунок циклічного розбиття адреси.

У наведеному прикладі (рис. 5) для вибору банку використовуються два молодших розрядів адреси

(A1, A0), а для вибору клітинки в банку — 7 старших розрядів (A8-A2).

Рисунок 5 — Блокова пам'ять з чергуванням адрес за циклічною схемою

Послідовний доступ в пам'ять зазвичай проводиться до комірок, що мають суміжні адреси.

Можна досягти в В (В — кількість банків) раз більшої швидкості, обміну з, пам'яттю в цілому,

ніж у окремого її банку, якщо забезпечити одночасне послідовне звернення до

даних в кожному з банків.

Якщо запити до одного й того ж банку слідують один за одним, кожен наступний запит

повинен очікувати завершення обслуговування попереднього. Така ситуація називається конфліктом з доступу.

При частому виникненні конфліктів з доступу метод стає неефективним.

4.3 Організація ОП на основі блокової схеми з блочно-циклічною схемою розшарування

За блочно-циклічною схемою розшарування пам'яті кожен банк складається з декількох модулів, адресованих за круговою схемою. Адреси між банками розподілені за блоковою схемою. Адреса комірки розбита на три частини. Старші біти визначають номер банку, наступна група розрядів адреси вказує на клітинку в модулі, а молодші біти адреси обирають модуль в банку (рис. 6).

Рисунок 6 — Блочно-циклічна схема розшарування пам'яті

Висновки

Наведені способи розшарування пам'яті добре працюють при вирішенні однієї задачі, для якої

характерна властивість локальності. У багатопроцесорних системах із загальною пам'яттю, де запити на

доступ до пам'яті достатньо незалежні, розглядається розвиток ідеї розшарування пам'яті. Для цього

в систему включають декілька контролерів пам'яті, що дозволяє окремим банкам працювати

абсолютно автономно. Ефективність даного прийому залежить від частоти незалежних звернень

до різних банків.

Чим більша кількість банків, тим менша ймовірність послідовних звернень до

одного й того ж банку пам'яті.

Література

- Цилькер Б.Я. Организация ЭВМ и систем [Текст]: — М : ПИТЕР, 2004. — 668 с.

- Столингс У. Структурная организация и архитектура компьютерных систем [Текст]: — М. : Вильямс, 2002. — 893 с.

- Оперативная память [Электронный ресурс]. — Режим доступа: http://ru.wikipedia.org/wiki/Оперативная память

- Шпаковский Г.И. Организация параллельных ЭВМ и суперскалярных процессоров [Текст]: — Мн.: Белгосуниверситет, 1996. — 296 с.: ил.

- Халабия Р.Ф. Организация вычислительных систем и сетей [Текст]: — М. : МГАПИ-Москва, 2000. — 141 с.

- Фельдман Л.П., Михайлова Т.В. Вероятностная модель блочной памяти // Искусственный интеллект.— Донецк: ІПШІ МОН і НАН України “Наука і освіта”, 2010.

- Мюллер C. Модернизация и ремонт ПК, 18-е издание [Текст]: пер. с англ. — : ООО «И.Д. Вильямс», 2009. — 1280 с.

- Алиев Т.И. Основы моделирования дискретных систем [Текст]: — СПб. : СПбГУ ИТМО, 2009. — 363 с.

- Букатов А. А., Дацюк В. Н., Жегуло А. И. Программирование многопроцессорных вычислительных систем [Текст]: — Ростов-на-Дону : ООО «ЦВВР», 2003. — 208 с.

- Архитектура компьютера [Электронный ресурс]. — Режим доступа: http://itblock.ru/

Важливе зауваження

Підчас написання даного автореферату магістерська робота ще не була завершена. Остаточне завершення: грудень 2011 р. Повний текст роботи та матеріали за даною темою можуть бути отримані у автора або його керівника після вказаної дати.