Мой опыт проектирования встраиваемых систем в инструментальной среде Quartus Qsys

Содержание

- Причины выбора темы

- Quartus Qsys как новейшее средство для проектирования СнК

- Мой опыт работы с Quartus Qsys

- Возможности использования Quartus Qsys в сфере Internet-технологий

- Выводы и рекомендации

- Список использованной литературы

Причины выбора темы

Благодаря современным тенденциям роста степени интеграции интегральных схем все большее применение находит использование встраиваемых систем типа система-на-кристалле(СнК). Современные технологии позволяют погрузить в кристалл проект практически любой сложности. Несомненными преимуществами использования СнК является их миниатюрность (в кристалле помещается как вычислительное устройство и память, так и набор специальных контроллеров), относительно низкая потребляемая мощность и возможность автоматизации проектирования.

Относительно долго единственным средством проектирования СнК на базе FPGA фирмы Altera был инструмент SOPC Builder, входящий в состав САПР Quartus. Но в начале 2011 года фирма Altera представила новый инструмент для проектирования СнК под названием Qsys, пришедший на смену SOPC Builder, который был интегрирован в последний релиз САПР Quartus. Стала необходимой задача освоения новой среды проектирования для реализации текущих проектов в ногу со временем. Актуальность перехода на новое средство проектирования послужила поводом для освещения данной проблематики с учетом собственного опыта.

Quartus Qsys как новейшее средство для проектирования СнК

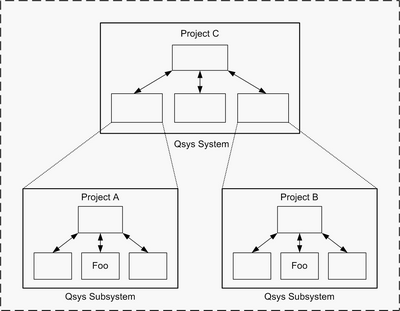

Даже при краткосрочном знакомстве с новым инструментарием становится ясно, что разработчики сделали ставку на качественно новое отличие, по сравнению с SOPC Builder — поддержку иерархической структуры, которая подразумевает использование спроектированных в Qsys систем в качестве подсистем для последующих Qsys-проектов. Данное нововведение позволяет сделать систему более масштабируемой, за счет использования уже спроектированных модулей. Таким образом, не только облегчается процесс проектирования, но и делается более удобным в использовании графический пользовательский интерфейс. Уровень абстракции системы был повышен — если в SOPC Builder наибольшим звеном было IP-ядро, то в Qsys таким звеном является подсистема. Пример иерархической структуры изображен на рис. 1.

Рисунок 1 — Пример иерархической структуры проекта

Наряду с появлением иерархической структуры было заявлено повышение производительности систем по сравнению с SOPC Builder до двух раз, благодаря использованию новой системы межсоединений, основанной на FPGA-оптимизированной технологии Network-on-Chip [1].

Помимо этого, повышена эффективность передачи информации по шине данных (от master к slave), что обеспечивает повышение пропускной способности соединений.

Для большей универсальности спроектированных систем добавлена возможность использования интерфейсов промышленных стандартов, что подразумевает возможность соединения IP-ядер, которые используют различные интерфейсы [2].

В завершение к упомянутым нововведениям стоит добавить возможность автоматической генерации testbench, а также наличие специального средства ускоренной верификации с использованием транзакций на чтение/запись при отладке проекта на чипе в реальном времени.

Мой опыт работы с Quartus Qsys

Первым делом для ознакоммления с новой средой разработки я принялся к изучению вводного примера [3] по разработке, который реализовывал простую систему тестирования модуля памяти SDRAM. Предполагалось собрать СнК, которая включает в себя процессор, контроллер памяти и собственно подсистему тестирования модуля памяти. Подсистема тестирования памяти состояла из генератора тестов, контроллера тестов и устройства проверки тестовых реакций. Таким образом уже на таком простом примере проявилось нововведение Qsys — возросший от ядра до подсистемы уровень иерархии. Полученный опыт по сборке простейшей СнК обеспечил возможность разработки более серьезных проектов.

Полученные знания по работе в Quartus Qsys в дальнейшем были расширены и закреплены в ходе работы над курсовым проектом в рамках курса FPGA & HDL технологии проектирования КС

, в рамках которого мне необходимо было разработать подсистему опроса датчиков в составе СРВ на базе FPGA фирмы Altera.

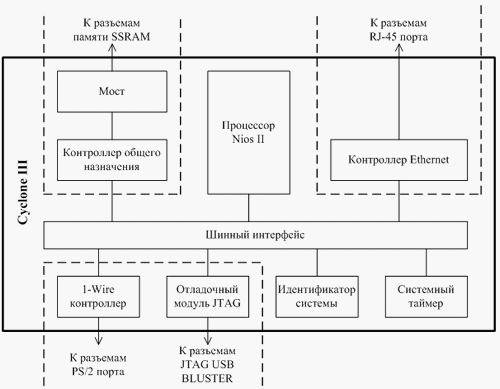

Для выполнения поставленных к подсистеме требований была разработана структура СнК с учетом особенностей платформы NEEK [4], которая представлена на рис. 2.

Рисунок 2 — Структура СнК

С учетом обозначенной структуры и особенностей проектирования в состав СнК вошли следующие модули:

- Делитель частоты pll, обеспечивающий отдельную схему синхронизации процессора и памяти.

- Выходные мосты для синхронизации памяти и остальных системных узлов ssram_clock_bridge и system_clock_bridge соответственно.

- Идентификатор системы sys_id.

- Контроллер JTAG, необходимый для прошивки платформы и отладки проекта.

- Интерфейсы подключения памяти (ssram_controller, ssram_bridge_pin_sharer, ssram_bridge).

- Процессор NIOS II (cpu).

- Системный таймер sys_timer.

- Контроллер 1-Wire интерфейса для подключения датчика температуры sockit_owm_inst.

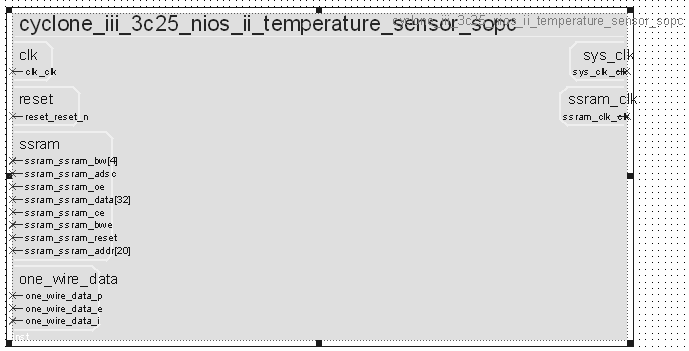

Результатом сборки компонентов СнК стала синтезированная блоковая схема, представленная на рис. 3.

Рисунок 3 — Блоковая схема СнК

Возможности использования Quartus Qsys в сфере Internet-технологий

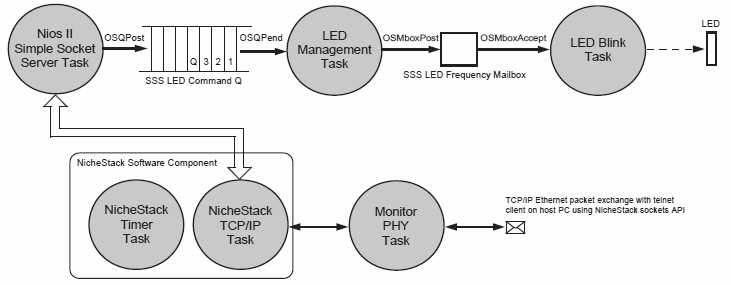

Применение Quartus Qsys в сфере Internet-технологий возможно благодаря включению в состав СнК контроллера Ethernet, реализующего функции стека протоколов TCP/IP. Примером такого использования является демонстрационный проект NIOS II Simple Socket Server [5]. Этот пример демонстрирует проект сокет сервера, использующего NicheStack TCP/IP под NIOS II, работающий под управлением MicroC/OS-II. Сервер реализует простые команды управления светодиодами платформы через отдельную задачу ОС MicroC/OS-II. Этот пример не является полной реализацией сервера Telnet, а использует интерфейс сокетов. Принцип работы проекта показан на рис. 4.

Рисунок 4 — Принцип работы проекта

Выводы и рекомендации

Таким образом, инструментальная среда Quartus Qsys позволяет собирать иерархические и легко масштабируемые СнК с использованием большого набора стандартных компоментов, будь то периферийные контроллеры или контроллер Ethernet. Qsys можно рекомендовать для проектирования встраиваемых систем для самых различных областей применения.

Список использованной литературы

- Qsys - Altera’s System Integration Tool [Электронный ресурс]. Режим доступа: http://www.altera.com/products/software/quartus-ii/subscription−edition/qsys/qts−qsys.html

- Reasons to Switch from SOPC Builder to Qsys [Электронный ресурс]. Режим доступа: http://www.altera.com/education/webcasts/all/source−files/wc−2011−reasons−switch−qsys/player.html

- Qsys system design tutorial [Электронный ресурс]. Режим доступа: http://www.altera.com/literature/tt/tt_qsys_intro.pdf

- Cyclone III Device Handbook, Volume 1. [Электронный ресурс]. Режим доступа: http://www.altera.com/literature/hb/cyc3/cyc3_ciii5v1.pdf

- Using the NicheStack TCP/IP Stack - Nios II Edition Tutorial. [Электронный ресурс]. Режим доступа: http://www.altera.com/literature/tt/tt_nios2_tcpip.pdf