Компьютерные системы и сети

Программируемая логическая интегральная схема (ПЛИС, англ. Programmable logic device, PLD [15] [16]) – электронный компонент, используемый для создания цифровых интегральных схем. В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования (проектирования). Для программирования используются программатор и IDE (отладочная среда), позволяющие задать желаемую структуру цифрового устройства в виде принципиальной электрической схемы или программы на специальных языках описания аппаратуры: Verilog, VHDL и др. [14] [17]

ПЛИС широко используются для построения различных по сложности и по возможностям цифровых устройств, например, устройств с большим количеством портов ввода-вывода, устройств, выполняющих цифровую обработку сигнала, устройств, выполняющих передачу данных на высокой скорости и т. д. [1]

ПЛИС является важной темой для изучения в области компьютерной инженерии. Но стоимость оборудования создает большое препятствие для получения практического опыта студентами. Финансирование ВУЗов также не позволяет приобрести достаточное количество отладочных плат, чтобы студенты могли индивидуально выполнять свои проекты на практических занятиях. Выходом из этого положения может служить создание виртуальной лаборатории с доступом к ней через сеть Интернет. Это позволит студентам отлаживать свои проекты независимо от своего местоположения и беспрепятственно получать практический опыт в проектировании устройств на ПЛИС.

Общей целью магистерской работы является создание виртуальной FPGA [18] [19] лаборатории с удаленным доступом через Интернет. Организация удаленного доступа включает в себя загрузку прошивки проекта в ПЛИС микросхему, организация управления устройствами ввода отладочного стенда, визуализация вывода результатов, организация распределенного доступа к плате [20] [21].

Прошивка, загружаемая в плату, является разработанным проектом на VHDL или Verilog сгенерированным в bit файл специализированной средой разработки (например, ISE Design Studio). Загрузка прошивки будет происходить в следующей последовательности:

Визуализация выходных данных планируется при помощи видеокамеры, транслирующей в реальном времени изменение состояний отладочного стенда. Помимо этого, выходные данные можно будет получить через последовательный порт, подключенный к серверу.

Основной задачей проекта и магистерской работы в целом является предоставление пользователям тестирования периферийных устройств, подключенных к плате. Так как физически получить доступ к периферийному оборудованию через Интернет у пользователя возможности не будет, необходимо разработать метод эмуляции этого оборудования таким образом, чтобы, разрабатываемый, проект для эмулированного оборудования минимально отличался от проекта с реальными устройствами. В первую очередь, планируется разработать эмуляторы для компьютерной мыши и клавиатуры, подключаемых по протоколу PS/2.

Также при организации удаленного доступа к FPGA [22] [23] плате необходимо учесть распределенный доступ, который заключается в разграничении прав доступа к отладочному стенду и организации очереди работы с ним. Это необходимо сделать потому что в плату можно загрузить только один проект. Поэтому нужно организовать два типа доступа: глобальный и локальный. Глобальный тип доступа заключается в установлении администратором особых прав на доступ к плате, а локальный в организации очереди работы с платой, то есть работа с одной платой возможна только в рамках одной сессии. Как только пользователь завершает работу с платой, он ее освобождает, или система автоматически освобождает плату при длительной неактивности, и тогда следующий пользователь может начать новую сессию [24] [25].

На сегодняшний день доступ в Интернет можно получить практически с любой точки земного шара, поэтому создание виртуальной лаборатории является актуальной задачей. Организация доступа к лаборатории через веб-сайт обусловлена тем, что браузеры работают практически одинаково во всех популярных операционных системах, как для стационарных систем, так и мобильных.

Отчет о поиске по теме магистерской работы показал, что проектов по созданию виртуальных лабораторий с доступом к FPGA-комплексам единицы, а таких, которые включают в себя эмуляцию периферийного оборудования еще меньше. Один из них – это работа магистра нашей специальности Беседы Д. Г., который работал над такой же темой. К сожалению, конкретных результатов получить не удалось, поэтому данная тема остается актуальной. Его наработки и публикации по данной теме можно посмотреть на его магистерской странице [2]. Примеры научных работ по разработке виртуальных FPGA лабораторий также можно найти по ссылкам [3] [4] [5] [6].

Система удаленного управления платой структурно разделяется на три части: клиентская часть (веб-сайт), серверная часть и отладочный FPGA-комплекс (рисунок 1).

Веб-сайт должен состоять из страницы авторизации, регистрации и личного кабинета. У каждого пользователя могут быть права доступа:

После регистрации пользователю присваивается право доступа гость

, администратор может в личном кабинете установить ему необходимые права. Структурно личный кабинет пользователя

представлен на рисунке 2.

В правой части должен находится файловый менеджер личной директории пользователя. С помощью нее можно загружать файлы, создавать директории, удалять файлы и директории, и загружать прошивку в плату. В центральной части будет находится управляющая консоль, которая будет служить, в первую очередь, для ведения лога и вывода информации из отладочного стенда. Слева должен будет отображаться плеер с видеотрансляцией отладочного стенда. В нижней части находится панель управления, на которой будут находится вспомогательные настройки управления удаленной лабораторией.

Серверная часть представляет собой связующее звено между отладочным стендом и пользователем. На сервере должны быть установлены веб-сервер (IIS) для передачи информации пользователю, база данных (MySQL) и серверный язык программирования (PHP), генерирующий HTML-код и обрабатывающий данные, полученные от пользователя и отдаваемые ему. Также должно быть установлено программное обеспечение для работы с отладочным стендом (Xilinx ISE Design Studio) и программное обеспечение организующая видеотрансляцию (VLC). Для загрузки прошивки необходимо использовать JTAG интерфейс, а для приема и передачи данных предлагается использовать последовательный порт (COM-порт).

На сервере происходит обработка регистрационных данных пользователя, проверка прав доступа, организация доступа к плате, прием и передача данных от пользователя к стенду и наоборот. Также на сервере ведется видеотрансляция и передача видеопотока клиенту.

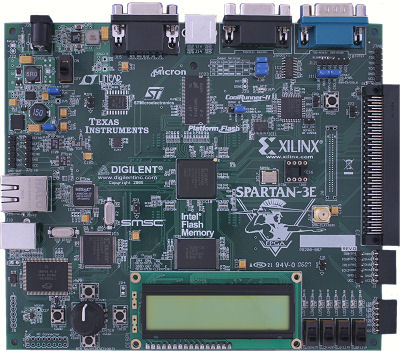

В качестве отладочного стенда будет использоваться FPGA плата фирмы Xilinx – Spartan 3E Starter Kit (рисунок 3). Плата Spartan-3E Starter Kit подчеркивает уникальные особенности FPGA плат семейства Spartan 3E и обеспечивает удобную платформу для разработки встраиваемых приложений. Плата имеет следующие особенности: параллельная NOR Flash конфигурация; множественная загрузка FPGA конфигураций из параллельной NOR Flash PROM; последовательная SPI Flash конфигурация; разработка встраиваемых систем: 32-х разрядный RISC процессор Microblaze, 8-ми разрядный контроллер PicoBlaze; DDR память [7].

Для тестирования периферийных устройств на отладочном стенде используется микропроцессорное ядро Microblaze. Microblaze – soft-процессорное ядро, разработанное компанией Xilinx для использования в FPGA. Microblaze реализуется с помощью стандартной логики и блоков памяти ПЛИС [8].

MicroBlaze имеет универсальные средства связи с периферией, обеспечивающих возможности его широкого применения во встраиваемых системах. Основная шина ввода/вывода – CoreConnect PLB – шина с возможностью работы в режимах master и slave. Большинство блоков подключаются непосредственно к PLB. Для доступа к внутренней памяти ПЛИС (BRAM), MicroBlaze использует специальную шину LMB, что снижает нагрузку на другие шины [9] [26] [27].

Для данной задачи интерес представляет шина PLB – Processor Local Bus. Это 128-битная шина для соединения произвольного числа периферийных устройств. Она состоит из модуля управления шиной, таймера, программных модулей чтения и записи данных, блока адресации и дополнительного DCL (Device Control Register) slave интерфейса для обеспечения доступа к регистру ошибок [10] [28] [29].

Прежде чем приступать к эмуляции периферийного оборудования, следует изучить принцип работы интерфейсов, с которыми оно работает. Клавиатура и компьютерная мышь чаще всего работает через интерфейс PS/2. PS/2 – двунаправленный интерфейс, организующий информационный обмен между двумя устройствами. В этом интерфейсе основными линиями являются Data и CLK. Каждый пакет имеет длину 11 бит:

0;

1.

Клавиатура передает по последовательному порту scan-коды клавиш, а мышь передает 3 или 4 байта данных, содержащих состояние нажатых кнопок и смещение мыши на плоскости. Четвертый байт может быть прокрутка колеса мыши, но для этого мышь необходимо специально инициализировать.

Хост устройство может посылать команды контроллеру клавиатуры и мыши. После приема каждой из команд мышь и клавиатура отвечает байтом 0xFA. Основными командами общими для мыши и клавиатуры являются:

При инициализации устройства передают байт 0xAA, при этом клавиатура после этого сразу может пересылать scan-коды клавиш, а мышь должна отправить следом байт 0x00 – это идентификатор мыши без использования колеса. Для инициализации мыши с колесом необходимо провести дополнительную инициализацию, подробней об этом можно почитать в официальной документации [11] [12] [13].

Структура пакета данных мыши показана на рисунке 4.

Первый байт имеет следующую структуру:

Второй байт – это смещение по оси Х, а третий байт – это смещение по оси Y. Смещение считается по оси Х слева направо, а Y снизу-вверх. Причем, если мышь движется вниз и вправо, то смещение отрицательное, а если вверх и влево, то положительное. Значения смещения находятся в диапазоне -255 – 255. Знак смещения хранится в первом байте, а если это значение превышено, то устанавливается бит переполнения [11].

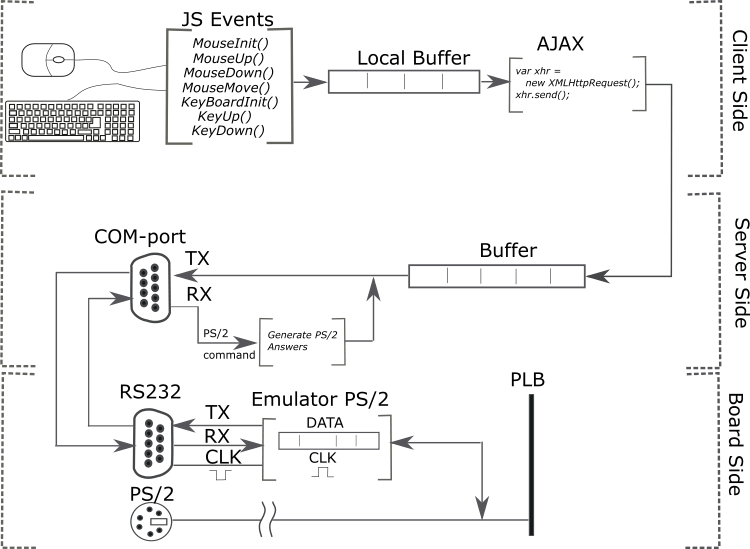

Эмулятор клавиатуры и мыши будет использовать все части проекта, а именно клиентскую, серверную и плату. На рисунке 5 показан механизм работы эмулятора интерфейса PS/2. На клиентской стороне с помощью JavaScript будут обрабатываться события клавиатуры и мыши, которые будут формировать необходимые пакеты кодов и отправлять их на сервер. Перед отправкой данных необходимо запустить инициализацию устройства. После чего обработчики событий от клавиатуры будут проверять код нажатых клавиш, подбирать необходимый код из таблицы scan-кодов, дополнять дополнительными кодами, в случае расширенных клавиш, а также дополнять отпускаемые клавиши специальным break-кодом (0xF0). Алгоритм инкапсуляции кодов клавиатуры показан на рисунке 6. Сформированные данные будут отправляться на сервер с помощью ajax-запросов. Чтобы избежать превышения количества запросов, и чтобы клиентское приложение не зависло, необходимо отправлять фиксированный объем данных, ждать ответа от сервера, и только потом отправлять следующий набор данных. Для того чтобы узнать состояние платы, требуется дополнительный асинхронный запрос, который будет повторятся с определенным интервалом времени.

Мышь на клиентской части работает аналогичным образом. Также инициализатор мыши формирует необходимые коды. Обработчики событий движения мыши, нажатия и отпуска кнопок формируют пакеты данных мыши и также, как и клавиатура отправляют эти данные на сервер. Формирование пакетов данных от мыши представлено на рисунке 7.

Сервер принимает данные от клиента, буферизирует их, и последовательно передает через COM-порт на плату. Если плата отправляет команду устройству, то эту команду перехватывает серверное приложение и отправляет соответствующий ответ.

Данные, переданные через COM-порт, принимаются платой и передаются эмулятору протокола PS/2, разработанному на языке VHDL. Цель этого эмулятора принять данные с последовательного интерфейса RS232, преобразовать эти данные в вид пакета PS/2 и передать на шину PLB, в обход физическому интерфейсу. Принятые данные с шины PLB, также следует преобразовать в вид подобный для интерфейса RS232 и передать их на сервер.

На момент создания данной страницы магистерская работа не является завершенной. На текущий момент выполнения магистерской работы можно отметить, что выбран вектор направления реализации проекта и основные методы реализации. В дальнейшем планируется разработка всех описанных модулей эмуляции периферийного оборудования [30] [31] [32].

Открытое образование. Статья: Универсальная учебная лаборатория междисциплинарного обучения автоматизированному проектированию цифровой аппаратуры, 2009 г. Авторы: Н.А. Дмитриев, Л.Д. Забродин, М.Н. Ёхин, Б.Н. Ковригин, М.Ю. Павлов. Режим доступа: www.e-joe.rusub[PDF] (Дата обращения 22 мая 2016г.)

Навигационная система на базе FPGA-технологий с возможностью самотестирования/ Збірка матеріалів сьомої міжнародної наук. техн. конф. студентів, аспірантів та молодих науковців

Інформатика та комп'ютерні технології — 2011. – Донецьк: ДонНТУ - 2011.

Информатика и компьютерные технологии, 22-23 ноября 2011 г., Донецк: ДонНТУ. - 2011. В 2-х томах, Т. 2. - С. 44-48.

Информатика и компьютерные технологии, сборник трудов VII международной научно-технической конференции студентов, аспирантов и молодых учёных - 22-23 ноября 2011 г., Донецк, ДонНТУ. - 2011. В 2-х томах, Т. 1. - С. 72-76.

Информатика и компьютерные технологии, 22-23 ноября 2011 г., Донецк: ДонНТУ. - 2011. В 2-х томах, Т. 1. - С. 44-47.

Информатика и компьютерные технологии, 22-23 ноября 2011 г., Донецк: ДонНТУ. - 2011. В 2-х томах, Т. 1. - С. 61-63.

Информатика и компьютерные технологии, 22-23 ноября 2011 г., Донецк: ДонНТУ. - 2011. В 2-х томах, Т. 2. - С. 19-21. 2012

Информационные управляющие системы и компьютерный мониторинг, 16-18 апреля 2012 г., Донецк, ДонНТУ. - 2012. С. 667-669.

систем-на-кристаллена базе FPGA на разных этапах проектирования // Сборник трудов III Всеукраинской научно-технической конференции студентов, аспирантов и молодых учёных

Информационные управляющие системы и компьютерный мониторинг, 16-18 апреля 2012 г., г. Донецьк: ДонНТУ. – 2012. С. 591-594.

Сучасні комп'ютерні інформаційні технології. – Тернопіль: ТНЕУ, 2012. – С. 89-90.

Сучасні комп'ютерні інформаційні технології. – Тернопіль: ТНЕУ, 2012. – С. 97-98.

Сучасні комп‘ютерні інформаційні технології. – Тернопіль: ТНЕУ, 2013.

Інформаційні управляючі системи та комп'ютерний моніторинг (ІУС КМ-2014), 22-23 квітня 2014 р., м. Донецьк : – Донецьк: ДонНТУ, 2014 - т .1 - С. 157-162

Инновационные перспективы Донбассав рамках I-го Межд. научного форума

Донбасс-2015, 20-22 мая 2015. – Донецк: ДонНТУ. – 2015. – С 4.

Компьютерная и программная инженерия – 2015. – Донецк: ДонНТУ. – 2015. – С 5.

Компьютерная и программная инженерия – 2015. – Донецк: ДонНТУ. – 2015. – С 4.

Компьютерная и программная инженерия – 2015. – Донецк: ДонНТУ. – 2015. – С 5.

Современные информационные технологии и IТ-образование. - Москва: МГУ, 2011. - Т. 1. 787 С. 422-429