Комп'ютерні системи та мережі

Програмована логічна інтегральна схема (ПЛІС [14] [15], англ. Programmable logic device, PLD) – електронний компонент, який використовується для створення цифрових інтегральних схем. На відміну від звичайних цифрових мікросхем, логіка роботи ПЛІС не визначається при виготовленні, а задається за допомогою програмування (проектування). Для програмування використовуються програматор та IDE (середа відладки), що дозволяють задати бажану структуру цифрового пристрою у вигляді принципової електричної схеми або програми на спеціальних мовах опису апаратури: Verilog, VHDL та ін. [16] [17]

ПЛІС широко використовуються для побудови різних за складністю та можливостями цифрових пристроїв, наприклад, пристроїв з великою кількістю портів вводу-виводу, пристроїв, що виконують цифрову обробку сигналу, та передачу даних на високій швидкості тощо. [1]

ПЛІС є важливою темою для вивчення в сфері комп'ютерної інженерії. Але вартість обладнання створює велику перешкоду для отримання практичного досвіду студентами. Фінансування ВНЗ також не дозволяє придбати достатню кількість плат для налагодження, щоб студенти могли індивідуально виконувати свої проекти на практичних заняттях. Виходом з цього положення може служити створення віртуальної лабораторії з доступом через мережу Інтернет. Це дозволить студентам налагоджувати свої проекти незалежно від свого місця розташування і безперешкодно отримувати практичний досвід в проектуванні пристроїв на ПЛІС.

Загальною метою магістерської роботи є створення віртуальної FPGA [18] [19] лабораторії з видаленим доступом через Інтернет. Організація видаленого доступу включає в себе завантаження прошивки проекту до ПЛІС мікросхеми, організація управління пристроями вводу стенду налагодження, візуалізація виводу результатів, організація розподіленого доступу до плати [20] [21].

Прошивка, що завантажується до плати, є розробленим проектом на VHDL або Verilog згенерованих в bit файл в спеціалізованому середовищі розробки (наприклад, ISE Design Studio). Завантаження прошивки буде відбуватися в наступній послідовності:

Візуалізація вихідних даних планується за допомогою відеокамери, яка транслює в реальному часі зміну станів стенду налагодження. Крім цього, вихідні дані можна буде отримати через послідовний порт, підключений до сервера.

Основним завданням проекту і магістерської роботи в цілому є надання користувачам доступ до тестування периферійних пристроїв, підключених до плати. Так як фізично отримати доступ до периферійного устаткування через Інтернет у користувача можливості не буде, необхідно розробити метод емуляції цього обладнання таким чином, щоб, проект для емуляції обладнання мінімально відрізнявся від проекту з реальними пристроями. В першу чергу, планується розробити емулятори для комп'ютерної миші та клавіатури, що підключаються по протоколу PS/2.

Також при організації видаленого доступу до FPGA [22] [23] плати необхідно врахувати розподілений доступ, який полягає в розмежуванні прав доступу до стенду налагодження та організації черги роботи з ним. Це необхідно зробити тому що в плату можна завантажити тільки один проект. Тому потрібно організувати два типи доступу: глобальний і локальний. Глобальний тип доступу полягає у встановленні адміністратором особливих прав на доступ до плати, а локальний в організації черги роботи з платою, тобто робота з однією платою можлива тільки в рамках однієї сесії. Як тільки користувач завершує роботу з платою, він її звільняє, або система автоматично звільняє плату при тривалій не активності, і тоді наступний користувач може почати нову сесію [24] [25].

На сьогоднішній день доступ в інтернет можна отримати практично з будь-якої точки земного шару, тому створення віртуальної лабораторії є актуальним завданням. Організація доступу до лабораторії через веб-сайт обумовлена тим, що браузери працюють практично однаково в усіх популярних операційних системах, як для стаціонарних систем, так і для мобільних.

Звіт про пошук по темі магістерської роботи показав, що проектів зі створенням віртуальних лабораторій з доступом до FPGA-комплексам одиниці, а таких, які включають в себе емуляцію периферійного обладнання ще менше. Одна з них – це робота магістра нашої спеціальності Беседи Д. Г., який працював над такою ж темою. На жаль, конкретних результатів отримати не вдалося, тому дана тема залишається актуальною. Його напрацювання і публікації на цю тему можна подивитися на його магістерській сторінці [2]. Приклади наукових робіт з розробки віртуальних FPGA лабораторій також можна знайти за посиланнями [3] [4] [5] [6].

Система видаленого керування платою структурно поділяється на три частини: клієнтську (веб-сайт), серверну та FPGA-комплекс (рисунок 1).

Веб-сайт повинен складатися з сторінки авторизації, реєстрації та особистого кабінету користувача. У кожного користувача можуть бути права доступу:

Після реєстрації користувачеві привласнюється право доступу гість

, адміністратор може в особистому кабінеті встановити йому необхідні права. Структурно особистий кабінет користувача

представлено на рисунку 2.

У правій частині повинен знаходиться файловий менеджер особистої директорії користувача. За допомогою неї можна завантажувати файли, створювати директорії, видаляти файли і директорії та завантажувати прошивку до плати. У центральній частині буде знаходиться керуюча консоль, яка буде служити, в першу чергу, для ведення логу та виводу інформації з налагоджувального стенда. Зліва повинен відображатися плеєр з відеотрансляцією стенду налагодження. У нижній частині знаходиться панель керування на якій будуть знаходиться допоміжні настройки керування видаленою лабораторією.

Серверна частина являє собою сполучну ланку між налагоджувальним стендом та користувачем. На сервері повинні бути встановлені веб-сервер (IIS) для передачі інформації користувачу, база даних (MySQL) та серверний інтерпретатор коду програмування (PHP), що генерує HTML-код і обробляє дані, отримані від користувача, і віддає йому. Також має бути встановлено програмне забезпечення для роботи з налагоджувальним стендом (Xilinx ISE Design Studio) та програмне забезпечення організації відеотрансляції (VLC). Для завантаження прошивки необхідно використовувати JTAG інтерфейс, а для прийому й передачі даних пропонується використовувати послідовний порт (COM-порт).

На сервері відбувається обробка реєстраційних даних користувача, перевірка прав доступу, організація доступу до плати, прийом й передача даних від користувача до стенду і навпаки. Також на сервері ведеться відеотрансляція та передача відеопотоку клієнту.

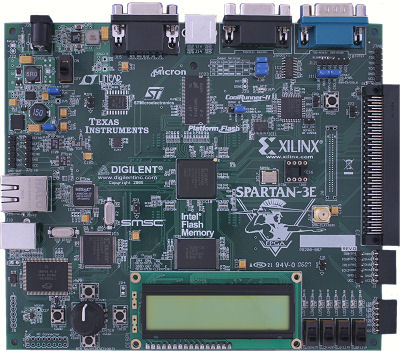

В якості стенду налагодження буде використовуватися FPGA плата фірми Xilinx – Spartan 3E Starter Kit (рисунок 3). Плата Spartan-3E Starter Kit підкреслює унікальні особливості FPGA плат сімейства Spartan 3E та забезпечує зручну платформу для розробки вбудованих додатків. Плата має такі особливості: паралельна NOR Flash конфігурація; множинна завантаження FPGA конфігурацій з паралельної NOR Flash PROM; послідовна SPI Flash конфігурація; розробка вбудованих систем: 32-х розрядний RISC процесор Microblaze, 8-ми розрядний контролер PicoBlaze; DDR пам'ять [7].

Для тестування периферійних пристроїв на стенді налагодження використовується мікропроцесорне ядро Microblaze. Microblaze – це soft-процесорне ядро, розроблене компанією Xilinx для використання у FPGA. Microblaze реалізується за допомогою стандартної логіки та блоків пам'яті ПЛІС [8].

MicroBlaze має універсальні засоби зв'язку з периферією, що забезпечують можливості його широкого застосування у вбудованих системах. Основна шина вводу / виводу – Core Connect PLB – шина з можливістю роботи в режимах master та slave. Більшість блоків підключаються безпосередньо до PLB. Для доступу до внутрішньої пам'яті ПЛІС (BRAM), MicroBlaze використовує спеціальну шину LMB, що знижує навантаження на інші шини [9] [26] [27].

Для даної задачі інтерес являє шина PLB – Processor Local Bus. Це 128-бітна шина для з'єднання довільного числа периферійних пристроїв. Вона складається з модуля керування шиною, таймера, програмних модулів читання й запису даних, блоку адресації і додаткового DCL (Device Control Register) slave інтерфейсу для забезпечення доступу до регістру помилок [10] [28] [29].

Перш ніж приступати до емуляції периферійного обладнання, слід вивчити принцип роботи інтерфейсів, з якими воно працює. Клавіатура і комп'ютерна миша найчастіше працюють через інтерфейс PS/2. PS/2 – двонаправлений інтерфейс, який організовує інформаційний обмін між двома пристроями. У цьому інтерфейсі основними лініями є Data й CLK. Кожен пакет має довжину 11 біт:

0;

1.

Клавіатура передає по послідовному порту scan-коди клавіш, а миша передає 3 або 4 байти даних, що містять стан натиснутих кнопок й зміщення миші на площині. Четвертий байт може бути прокрутка коліщатка миші, але для цього миш необхідно спеціально ініціювати.

Хост пристрій може посилати команди контролеру клавіатури й миші. Після прийому кожної з команд миш і клавіатура відповідають байтом 0xFA. Основними командами загальними для миші та клавіатури є:

При ініціалізації пристрої передають байт 0xAA, при цьому клавіатура після цього відразу може пересилати scan-коди клавіш, а миша повинна відправити слідом байт 0x00 – це ідентифікатор миші без використання коліщатка. Для ініціалізації миші з колесом необхідно провести додаткову ініціалізацію, докладніше про це можна почитати в офіційній документації [11] [12] [13].

Структура пакета даних миші показана на рисунку 4.

Первый байт имеет следующую структуру:

Другий байт – це зміщення по осі Х, а третій байт – це зміщення по осі Y. Зсув вважається по осі Х зліва направо, а Y знизу-вгору. Причому, якщо миш рухається вниз й вправо, то зміщення негативне, а якщо вгору й вліво, то позитивне. Значення зсуву знаходяться в діапазоні -255 – 255. Знак зміщення зберігається в першому байті, а якщо це значення перевищено, то встановлюється біт переповнення [11].

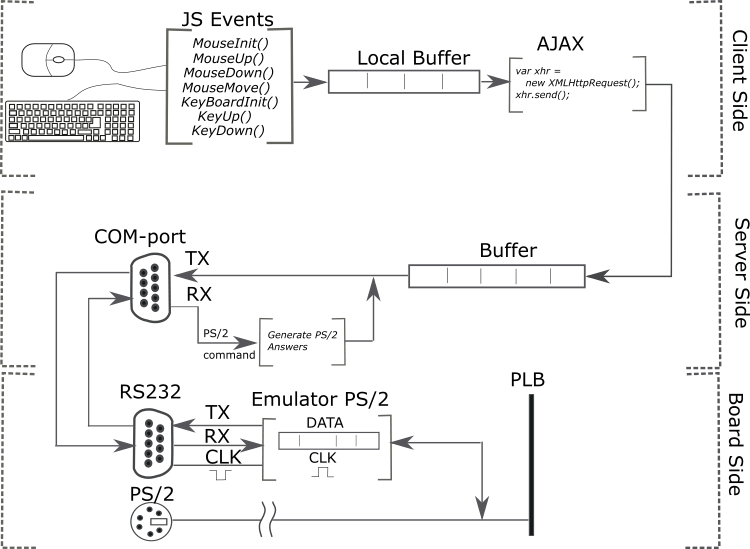

Емулятор клавіатури й миші буде використовувати всі частини проекту, а саме клієнтську, серверну та плату. На рисунку 5 показаний механізм роботи емулятора інтерфейсу PS/2. На стороні клієнта за допомогою JavaScript будуть оброблятися події клавіатури й миші, які будуть формувати необхідні пакети кодів і відправляти їх на сервер. Перед відправкою даних необхідно запустити ініціалізацію пристрої. Після чого обробники подій від клавіатури перевірятимуть код натиснутих клавіш, підбирати необхідний код з таблиці scan-кодів, доповнювати додатковими кодами, в разі розширених клавіш, а також відтиснуті клавіші спеціальним break-кодом (0xF0). Алгоритм інкапсуляції кодів клавіатури показаний на рисунку 6. Сформовані дані будуть відправлятися на сервер за допомогою ajax-запитів. Щоб уникнути перевищення кількості запитів, і щоб клієнтський додаток не перевантажився, необхідно відправляти фіксований обсяг даних, чекати відповіді від сервера, і тільки потім відправляти наступний набір даних. Для того щоб дізнатися про стан плати, є потреба у додатковому асинхронному запиті, який буде повторятися з певним інтервалом часу.

Миш на клієнтській частині працює аналогічним чином. Також ініціалізатор миші формує необхідні коди. Обробники подій руху миші, натискання і відпустки кнопок формують пакети даних миші і також, як і клавіатура відправляють ці дані на сервер. Формування пакетів даних від миші представлено на рисунку 7.

Сервер приймає дані від клієнта, буферезує їх, й послідовно передає через COM-порт на плату. Якщо плата відправляє команду пристрою, то цю команду перехоплює серверний додаток і відправляє відповідну відповідь.

Дані, передані через COM-порт, приймаються платою і передаються емулятору протоколу PS/2, розробленого на мові VHDL. Мета цього емулятора прийняти дані з послідовного інтерфейсу RS232, перетворити ці дані в вид пакета PS/2 і передати на шину PLB, в обхід фізичному інтерфейсу. Прийняті дані з шини PLB, також слід перетворити на вигляд подібний для інтерфейсу RS232 і передати їх на сервер.

На момент створення даної сторінки магістерська робота не є завершеною. На поточний момент виконання магістерської роботи можна відмітити, що обран вектор напрямку реалізації проекту і основні методи реалізації. Надалі планується розробка всіх описаних модулів емуляції периферійного обладнання [30] [31] [32]..

Відкрита освіта. Стаття: Універсальна навчальна лабораторія міждисциплінарного навчання автоматизованого проектування цифрової апаратури, 2009 р. Автори: Н.А. Дмитрієв, Л.Д. Забродін, М.Н. Ёхін, Б.Н. Ковригін, М.Ю.Павлов. Режим доступу: www.e-joe.rusub[PDF] (Дата звернення 22 травня 2016р.)

Інформатика та комп'ютерні технології — 2011. – Донецьк: ДонНТУ - 2011.

Информатика и компьютерные технологии, 22-23 ноября 2011 г., Донецк: ДонНТУ. - 2011. В 2-х томах, Т. 2. - С. 44-48.

Информатика и компьютерные технологии, сборник трудов VII международной научно-технической конференции студентов, аспирантов и молодых учёных - 22-23 ноября 2011 г., Донецк, ДонНТУ. - 2011. В 2-х томах, Т. 1. - С. 72-76.

Информатика и компьютерные технологии, 22-23 ноября 2011 г., Донецк: ДонНТУ. - 2011. В 2-х томах, Т. 1. - С. 44-47.

Информатика и компьютерные технологии, 22-23 ноября 2011 г., Донецк: ДонНТУ. - 2011. В 2-х томах, Т. 1. - С. 61-63.

Информатика и компьютерные технологии, 22-23 ноября 2011 г., Донецк: ДонНТУ. - 2011. В 2-х томах, Т. 2. - С. 19-21. 2012

Информационные управляющие системы и компьютерный мониторинг, 16-18 апреля 2012 г., Донецк, ДонНТУ. - 2012. С. 667-669.

систем-на-кристаллена базе FPGA на разных этапах проектирования // Сборник трудов III Всеукраинской научно-технической конференции студентов, аспирантов и молодых учёных

Информационные управляющие системы и компьютерный мониторинг, 16-18 апреля 2012 г., г. Донецьк: ДонНТУ. – 2012. С. 591-594.

Сучасні комп'ютерні інформаційні технології. – Тернопіль: ТНЕУ, 2012. – С. 89-90.

Сучасні комп'ютерні інформаційні технології. – Тернопіль: ТНЕУ, 2012. – С. 97-98.

Сучасні комп‘ютерні інформаційні технології. – Тернопіль: ТНЕУ, 2013.

Інформаційні управляючі системи та комп'ютерний моніторинг (ІУС КМ-2014), 22-23 квітня 2014 р., м. Донецьк : – Донецьк: ДонНТУ, 2014 - т .1 - С. 157-162

Инновационные перспективы Донбассав рамках I-го Межд. научного форума

Донбасс-2015, 20-22 мая 2015. – Донецк: ДонНТУ. – 2015. – С 4.

Компьютерная и программная инженерия – 2015. – Донецк: ДонНТУ. – 2015. – С 5.

Компьютерная и программная инженерия – 2015. – Донецк: ДонНТУ. – 2015. – С 4.

Компьютерная и программная инженерия – 2015. – Донецк: ДонНТУ. – 2015. – С 5.

Современные информационные технологии и IТ-образование. - Москва: МГУ, 2011. - Т. 1. 787 С. 422-429