по теме:

“Исследования управляющих автоматов с жесткой логикой на ПЛИС”

Содержание

Введение

Цель и задачи работы

Предполагаемая научная новизна и практическая ценность

Планируемая практическая ценность

Обзор существующих разработок по теме

Текущие и планируемые результаты

Заключение и выводы

Список источников

Введение

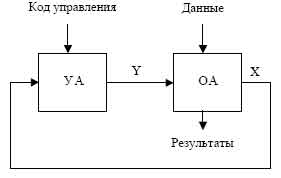

Современные цифровые устройства состоит из операционного автомата (ОА) и управляющего автомата (УА). Операционный автомат служит для выполнения заданных операций, а управляющий автомат требуется для стыковки, взаимодействия всех составных блоков устройства [1]. Изображение типового цифрового устройства представлено на рисунок 1.

Рисунок 1 – Структурная схема цифрового устройства.

На практике УА часто реализуют в виде автомата с "жесткой" логикой (автоматы Мили и Мура). Алгоритмы управления операционным устройством, являющиеся исходными данными для синтеза схемы УА, задаются, как правило, в виде граф-схем, которые отличаются большим количеством характеристик [1].

В настоящее время широко применяются три класса ПЛИС: простые ПЛИС (зарубежный термин SPLD - simple programmable logic device), комплексные ПЛИС (зарубежный термин CPLD - complex programmable logic device) и программируемые пользователем вентильные матрицы (зарубежный термин FPGA - field programmable gate array). В классе SPLD выделяют два подкласса: программируемые логические матрицы (ПЛМ, зарубежный термин PLAs - programmable logic arrays) и программируемые матрицы логики (ПМЛ, зарубежный термин PALs – programmable array logics). SPLD состоят из двух матриц: матрицы "И" и матрицы "ИЛИ". В ПЛМ обе матрицы программируемые, а в ПМЛ - матрица "ИЛИ" фиксированная. CPLD состоят из блоков логических вентилей, объединенных программируемой коммутационной матрицей. Современные CPLD, как правило, являются электрически перепрограммируемыми и сохраняют логическую структуру после отключения питания. FPGA состоят из большого числа конфигурируемых логических блоков (зарубежный термин LUT) и трассировочных ресурсов, обеспечивающих их межсоединения. Из современных ведущих разработчиков микросхем CPLD и FPGA следует отметить фирмы Xilinx, Altera, Atmel, Lattice Semiconductor, Cypress Semiconductor. [2]

В последнее время увеличение сложности разрабатываемых цифровых устройств привели к появлению принципиально новых средств проектирования - систем автоматизированного проектирования (САПР). Первоначально они имитировали ручную разработку аппаратных устройств инженером, позже с появлением микросхем класса FPGA и массовым выпуском ПЛИС появились первые языки описания аппаратуры и САПР с их поддержкой (80-е - 90-е годы XX века).

Цель и задачи работы

• разработка УА и метода синтеза, ориентированного на уменьшение аппаратурных затрат в логической схеме;

• оценка сложности реализации разрабатываемой структуры и исследование с целью определения областей ее эффективного применения;

• разработка программного обеспечения, поддерживающего реализацию заданного метода синтеза управляющих автоматов;

• оценка дальнейшего исследования синтезированного УА в различных средах САПР.

Предполагаемая научная новизна и практическая ценность

Научная новизна данной работы заключается в:

• исследовании структуры управляющих автоматов и методов синтеза, направленных на уменьшение аппаратурных затрат в логической схеме;

• установлении области эффективного применения разрабатываемой структуры;

• разработке САПР, поддерживающей реализацию заданного метода синтеза управляющих автоматов.

Планируемая практическая ценность

Предполагаемая практическая ценность состоит в разработке и исследовании управляющих автоматов с "жесткой" логикой, в логической схеме которой аппаратурные затраты уменьшены в сравнении с традиционными структурами. Разрабатываемое программное обеспечение по синтезу УА возможно будет использована в учебном процессе студентов.

Обзор существующих разработок по теме

В наше время для описания логической структуры цифровых устройств, как правило, используются высокоуровневые языки описания оборудования (Hardware Description Languages - HDL). Наиболее распространенными среди них являются языки VHDL и Verilog. Однако в состав многих зарубежных САПР включены специальные инструменты, которые позволяют упростить разработку управляющих автоматов, т.к. непосредственная реализация управляющих автоматов на языках высокого уровня является трудоемким процессом. Так в состав САПР Active - HDL фирмы Aldec включен модуль FSM. Он обладает многофункциональным графическим интерфейсом для описания управляющих автоматов, однако форма записи управляющего автомата требует знания языка HDL, также в этом модуле отсутствует какая-либо оптимизация структуры получившегося автомата.

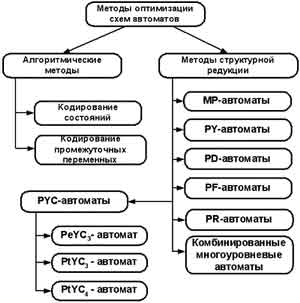

Классификация оптимизации структуры автоматов на ПЛИС [1] приведена на рисунке 2.

Рисунок 2 – Классификация методов оптимизации автоматов.

Однако в последнее время появление новых, более быстродействующих и содержащих большее количество логических ячеек на кристалле FPGA смещает приоритет при разработке устройств с минимизации аппаратурных затрат в полученной устройстве или максимизации быстродействия на обеспечение надежности работы полученного устройства при максимально коротком цикле разработки. Один из способов решения этой проблемы является использование средств, основанных на ранее разработанных средствах проектирования сложных систем для ПО, таких как управляемой моделями архитектуры (MDA – Model - Driven Architecture) и унифицированного языка моделирования (UML – Unified Modeling Language).

Текущие и планируемые результаты

На первом этапе работы над магистерской работой был исследован метод оптимизации структуры УА. В процессе синтеза автомата использованы несколько методов оптимизации в комплексе: структурная редукция, гетерогенная реализация, алгоритмические преобразования.

Научная новизна данной работы заключается в:

• формирование таблицы замены переменных;

• оптимальное кодирование состояний автомата;

• максимальное кодирование микроопераций;

• синтез логической схемы устройства.

В дальнейшем предполагается разработка программного продукта, которое позволит синтезировать заданный автомат. Процесс разработки сводиться к созданию пользователем текстового файла содержащего таблицу переходов, программа считывает данные из этого файла и переводит полученные данный в булевы формулы, после преобразования происходит процесс минимизации заданного ей управляющего автомата, выходным значением программы является файл формата HDL для дальнейшей его обработки, в таких пакетах как Active-HDL или в бесплатном VHDL компиляторов (например с VHDL Simili 3.0).

Структура разработанной системы приведена на рисунке 3.

Рисунок 3 – Общая структура программы.

Принцип работы системы: проектировщик (User), формирует текстовый файл (File.gsa) который содержит в себе таблицу переходов (ГСА), данные из этого файла используются программой (САПР) для преобразования и минимизации. Проанализировав и преобразовав полученную информацию, программа на выходе формирует файл (File.vhdl) формата HDL содержащий уже готовый синтезированный управляющий автомат, который можно в дальнейшем использовать в других средах.

Программа разработана на языке Visual С++, выбор языка программирования С++ был обусловлен тем, что в нем развиты средства проектирования графического интерфейса пользователя, возможность работать с текстовыми файлами [3], и способность для пошаговой алгоритмизации. Программный пакет реализован для платформа РС под операционную систему Windows.

Также в рамках данной магистерской работы предполагается на основе всех проделанных исследований сделать выводы о целесообразности применения заданной структуры УА для различных граф-схем алгоритмов.

Заключение и выводы

Результатом работы будет получение управляющих автоматов с "жесткой" логикой, в логической схеме которой аппаратурные затраты уменьшены в сравнении с традиционными структурами. Входными данными для САПР будет являться текстовый файл с основными характеристиками исследуемой граф-схемы алгоритма УА.

Список источников

[1] А.А. Баркалов Синтез устройств управления на программируемых логических устройствах. - Донецк. 2002.

[2] В.В. Соловьев. Проектирование цифровых систем на основе программируемых логических интегральных схем. - Москва. 2001.

[3] И.Я. Зеленева - "Методы синтеза многоуровневых структур управляющих автоматов на программируемых логических устройствах" - диссертационная работа.

При написании данного автореферата магистерская работа еще не завершена. Окончательное завершение: декабрь 2007 г.

|