Астахов Євген Олександрович

Факультет обчислювальної техніки та інформатики

Кафедра електронних обчислювальних машин

Специальність: Системне програмування

Тема випускної роботи:

Розробка та дослідження методів веріфікації FPGA проектів за методологією зонда, що керується, на основі технології Boundary Scan

Научний керівник: Зінченко Юрій Євгенович

Вступ

Як відомо, процес проектування обчислювальних пристроїв супроводиться відладкою (верифікацією) на всіх етапах проектування. Верифікація сучасних складних пристроїв за статистикою займає 75-80% від загального часу проектування і з тенденцією до погіршення цього параметра. Особливо гостро проблема верифікації стоїть на апаратному рівні (внутрішньосхемна верифікація). Тобто коли проект опускається до цільового пристрою (БІС, СБІС), тому тема роботи направлена на розробку методів і засобів верифікації проектів занурених в програмовано-логічну інтегральну схему (ПЛІС, FPGA), є актуальною. Фундаментальною технологічною основою для пропонованого способу верифікації є технологія «граничного сканування» (Boundary Scan — BS).

Розроблена спочатку з метою контролепригодного проектування і діагностики БІС, ця технологія знайшла також вживання при програмуванні і верифікації сучасних ПЛІС. В цілому технологія BS забезпечує доступ до внутрішніх крапок БІС через спеціально організований порт JTAG (Joint Test Advanced Group) проте вона не дає відповіді на те, як тестувати мікросхему або верифицировать проект, що знаходиться в ній. Для відповіді на це питання в даній роботі пропонується використовувати методологію зондової діагностики, вживану для традиційних цифрових пристроїв. Спільне використання технології BS і методології зондової діагностики (ЗД) цифрових пристроїв (ЦП) дозволяє забезпечити доступ з метою аналізу до внутрішніх контрольних крапок проекту в цільовій мікросхемі визначуваних алгоритмом зондування.

Зондова діагностика була дуже популярна в 80-х роках. У 90-і роки, із зростанням популярності ПЛІС на основі мікросхем в корпусах типу BGA, різко обмежився доступ до контактів мікросхем з огляду на те, що контакти мікросхем розташовані дуже близько один до одного що робить скрутним застосування традиційного методу зондової діагностики за допомогою щупа. Тому зондова діагностика стрімко втрачала свої позиції. У сьогодення час проекти опустилися в ПЛІС а технологія Boundary Scan забезпечує доступ до внутрішніх точок схеми що дозволяє повернутися до ідей зондової діагностики на якісно новому внутрішньосхемному рівні.

Дана робота направлена на розробку алгоритмів верифікації шляхом адаптації і вдосконалення алгоритмів і підходів зондової діагностики.

Предметом дослідження є алгоритми верифікації проектів занурених в ПЛІС на основі адаптації методів, ідей і підходів зондової діагностики.

Мета і завдання дослідження. Метою роботи є розробка ефективних алгоритмів верифікації проектів, що забезпечують швидкий спосіб пошуку можливих помилок з мінімальним часом пошуку і виправлення помилок з максимально можливим ступенем локалізації.

Для досягнення поставленої мети в роботі вирішуються наступні завдання:

1. Адаптація базового алгоритму SCAN пошуку несправностей за методом веденого зонда для верифікації проектів описаних в структурному типі HDL.

2. Розробка програмно-апаратних засобів верифікації FPGA проекту за методологією веденого зонда.

3. Експериментальне дослідження алгоритмів і структур верифікації FPGA проектів за методологією веденого зонда.

Огляд досліджень і розробок з теми «Розробка і дослідження методу верифікації FPGA проектів за методологією веденого зонда на базі технології Boundary Scan»

Регіональний рівень:

Матеріали магістрів ДОННТУ

1. http://masters.donntu.ru/2002/fvti/miroshnikov/diss/index.htm

«Разработка алгоритмов тестирования FPGA-устройств по технологии переферийного сканирования»

Автор: Мирошников Александр Сергеевич

Научный руководитель: к.т.н., доцент каф. ЭВМ ДонНТУ Зинченко Ю.Е.

2. http://masters.donntu.ru/2008/fvti/svistunov/diss/index.html

«Исследование и разработка на FPGA SPP-архитектуры поста контроля цифровых устройств»

Автор: Cвистунов Сергей Николаевич

Научный руководитель: к.т.н., доцент каф. ЭВМ ДонНТУ Зинченко Ю.Е.

3. http://masters.donntu.ru/2006/fvti/bobrovskyy/diss/index.htm

«Разработка структуры поста контроля зондовой диагностики ТЭЗ на базе HDL- и FPGA-технологий»

Автор: Бобровский Константин Викторович

Научный руководитель: к.т.н., доцент каф. ЭВМ ДонНТУ Зинченко Ю.Е.

4. http://masters.donntu.ru/2006/fvti/myadelets/diss/index.htm

«Разработка и исследование метода синтеза тестов для типовых элементов замены (ТЭЗ)»

Автор: Мяделец Александр Александрович

Научный руководитель: к.т.н., доцент каф. ЭВМ ДонНТУ Зинченко Ю.Е.

5. http://masters.donntu.ru/2002/fvti/rytov/dissert.htm

«Разработка диагностической модели FPGA - устройств и синтез тестов на ее основе»

Автор: Рытов Александр Сергеевич

Научный руководитель: к.т.н., доцент каф. ЭВМ ДонНТУ Зинченко Ю.Е.

6. http://masters.donntu.ru/2005/fvti/mukha/diss/index.htm

«Исследование реализаций MPEG2 видеопроцессоров на FPGA и PRUS»

Автор: Муха Евгений Михайлович

Научный руководитель: к.т.н., доцент каф. ЭВМ ДонНТУ Зинченко Ю.Е.

7. http://masters.donntu.ru/2004/fvti/korchenko/diss/index.htm

«Розробка способів рішення HDL-задач і системи тестування знань на їх основі»

Автор: Корченко Александр Александрович

Научный руководитель: к.т.н., доцент каф. ЭВМ ДонНТУ Зинченко Ю.Е.

Національний рівень:

На цьому рівні роботи в області теми магістерської роботи представлені роботами мого наукового керівника. По цьому линку http://hardclub.donntu.ru/zinchenko/science.htm можна дізнатися про наукові розробки на даному етапі.

Глобальний рівень:

В світі даною проблемою займаються набагато інтенсивніше.

На сайті IEEE Xplore міститься велике количесвто наукових статей, у тому числі і з даної тематики. Проте у вільному доступі представлені лише короткі огляди і виводи статей а основний вміст доступний лише зареєстрованим користувачам.

У цій статті http://www.soccentral.com/PrintPage.asp?PassedEntryID=13186 структурно описані ідеї, у напрямі яких галузь розвивається сьогодні. Цей підхід є актуальним.

В даний час немає подібних програмних реалізацій даного методу діагностики, передбачуваного темою магістерської роботи або, принаймні, вони знаходяться в закритому доступі.

Основний зміст роботи

На рисунку 1 наведена анімація існуючих алгоритмів пошуку несправностей.

Рисунок 1 — Алгоритми пошуку несправностей (анімація, 17 кадрів, 3 цикли, 146 Кбайт).

Як бачимо, існує декілька алгоритмів ЗД, таких як алгоритм послідовного зондування (Scan) алгоритм половинного ділення (Galop) і комбінований алгоритм (Galop + Scan), заснований на поєднанні перших двох алгоритмів. Всі ці алгоритми можуть бути застосовані і в разі внутрішньосхемної верифікації.

Вона включає стандартні програмні засоби фірми Xilinx і спеціальне ПЗ зондового діагностування, що розробляється автором роботи. Стандартні засоби побудовані на ChipScope – підсистемі BS фірми Xilinx . Сюди входять наступні компоненты:

1. Core Generator — генератор IP ядер ICON, ILA і інших, які реалізують механізми BS – використовується для створення BSDL-надстройки проекту шляхом впровадження IP ядер у вихідний код проекту користувача перед етапом синтезу.

2. Core Inserter — компонувальник IP ядер – використовується для альтернативної побудови BSDL-надстройки проекту, яка упроваджується у вихідний проект користувача після його синтезу.

3. Core Analyzer — аналізатор IP ядер – використовується як допоміжний засіб для візуального аналізу тестових реакцій у внутрішніх контрольних точках проекту, зануреного до ПЛІС.

У роботі передбачається розробити і порівняти декілька структур програмного забезпечення системи верифікації об'єкту проектування, виявити сильні і слабкі стороникожного технічного рішення, зробити виводи про кращу структурудля її впровадження.

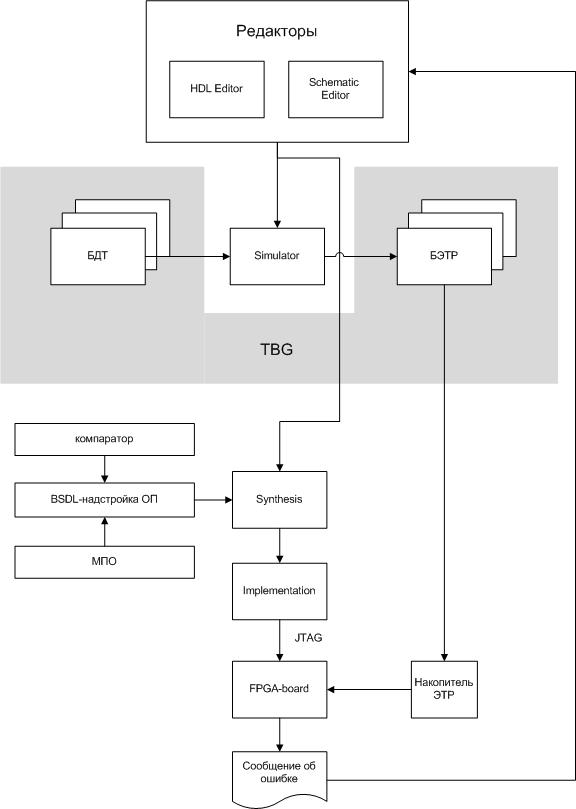

На рисунку 2 показана система верифікації FPGA-проектов з вбудованим алгоритмом зондування

Рисунок 2 — Система верифікації FPGA-проектов з вбудованим алгоритмом зондування

Опис структури:

Робота починається із створення проекту в редакторах:

1. HDL Editor — створення програмної коди в структурному HDL-стиле

2. Schematic Editor — створення схеми в графічному вигляді, використовуючи готову бібліотеку компонент

Після цього створений проект необхідно відладити, виключивши з нього прості логічні помилки. Для цього проект, створений в редакторах передається в блок Simulator, де проганяється через набір тестів, який забезпечує блок TBG - Test Bench Generator.

Цей блок TBG містить в своєму наборі базу даних тестів (БДТ), якими випробовується створений проект. А також базу еталонних тестових реакцій (БЕТР) - результати тестування проекту в блоці Simulator. Для створення бази даних тестів може бути використано ПЗ PRTG, розроблене в ДОННТУ на кафедрі ЕОМ. Набор тестів може бути створений уручну виходячи із специфікацій проекту.

Після відладки проект передається в блок Synthesis. На цьому етапі з проектом з'єднується BSDL-надстройка об'єкту проектування (BSDL - Boundary Scan Description Language), яка складається з:

1. компаратор — блок, що виконує порівняння достатку контрольних крапок (КТ) з базою еталонних тестів реакцій (БЕТР), яка отримана в блоці TBG.

2. МПО — модуль пошуку помилок, представлений у вигляді BSDL.

Обидва цих блоку у вигляді BSDL-надстройки з'єднуються з проектом на етапі Synthesis.

Далі проект проходить стадію Implementation, яка має на увазі стадію створення моделі. На виході блоку Implementation отримуємо bitstream, що полягає з вихідного проекту і BSDL-надстройки, що містить модуль пошуку помилок.

Використовуючи кабель JTAG, bitstream занурюється на налагоджувальну плату FPGA (FPGA-board) наприклад Altera DE2 board. До цієї плати через зовнішній роз'єм (наприклад USB) підключений накопичувач еталонних тестових реакцій (накопичувач ЕТР), інформація на якому записується на РС, використовуючи дані бази еталонних тестових реакцій (БЕТР).

Після початку роботи налагоджувальної FPGA-платы алгоритми пошуку помилок, реалізовані у вигляді модуля пошуку помилок BSDL-надстройки почнуть свою роботу.

Вони виконуватимуть зондування. Відповідно до алгоритму выбрается перша контрольна крапка (КТ), прочитується тестова реакція, порівнюється з еталоном який вибирається з бази еталонних тестових реакцій (БЕТР). Знаходиться момент першого неспівпадання. Залежно від цього приймається рішення: вірна реакція або неверная. Далі вибирається наступна контрольна крапка (КТ) або інша КТ.

Робота алгоритму продовжується до тих пір, поки не буде знайдена компонента, яка буде визнана помилковою. На монітор буде видано повідомлення з ідентифікацією цій компоненти, що послужить інформацією для проектувальника для виправлення своєї вихідної коди.

Достоїнствами описаної вище структури є:

1. Зменшення трафіку передаваної інформації об значення контрольних крапок (КТ) між ПЛІС і РС оскільки ця інформація обробляється в ПЛІС.

2. Швидкий доступ до контрольних крапок (КТ) без необхідності зовнішньої взаємодії.

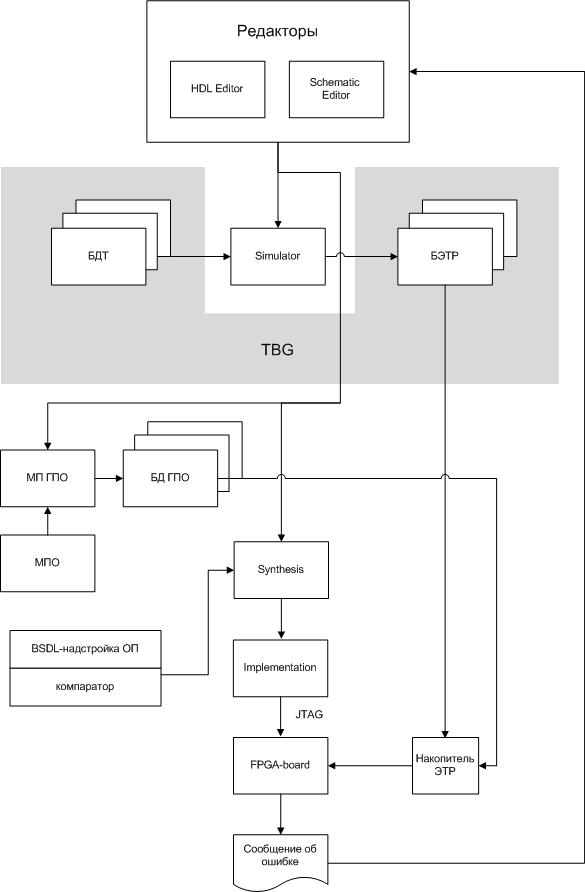

На рисунку 3 показана система верифікації FPGA-проектов на базі ГПО

Рисунок 3 — Система верифікації FPGA-проектов на базі ГПО

У цій структурі доданий блок модуля побудови графа пошуку помилок (МП ГПО). Даний блок отримує інформацію від блоку TBG і використовує модуль пошуку помилок (МПО) для того, щоб сформувати базу даних графів пошуку помилок (БД ГПО), яка потім записується на накопичувач ЕТР.

На попередньому етапі будується база даних графів пошуку помилок (БД ГПО).

Дана структура вигідно відрізняється тим, що в BSDL-надстройку не упроваджується модуль пошуку помилок (МПО) а упроваджений компаратор працює з БД ГПО, реалізованою за однотипним форматом, поза залежністю від алгоритму пошуку помилок.

Останні етапи аналогічні попередній структурі.

Достоїнствами даної структури є:

1. Для реалізації нового алгоритму пошуку помилок в даній системі ПЗ необхідно переписати лише блок модуля побудови графа пошуку помилок.

2. Зменшення трафіку передаваної інформації об значення контрольних крапок (КТ) між ПЛІС і РС, оскільки ця інформація обробляється в ПЛІС.

3. Швидкий доступ до контрольних крапок (КТ) без необхідності зовнішньої взаємодії.

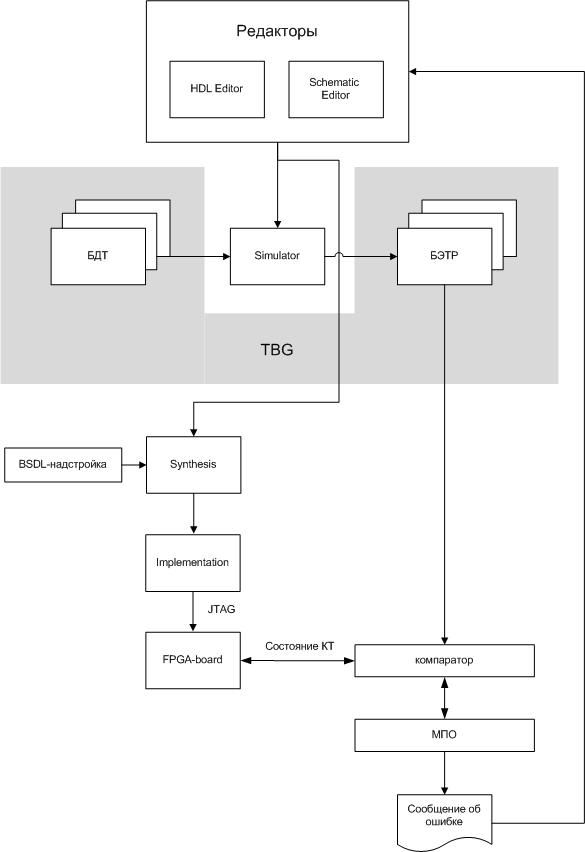

На рисунку 4 показана система верифікації FPGA-проектов із зовнішнім алгоритмом зондування

Рисунок 4 — Система верифікації FPGA-проектов із зовнішнім алгоритмом зондування

Метою цієї структури є граничне спрощення BSDL-надстройки, оскільки на неї покладаються лише функції вилучення контрольної крапки (КТ), вказаної ззовні. Всі останні функції реалізуються в РС: пошук помилок, компаратор.

Проте реалізація такого підходу вимагає збільшення трафіку між FPGA і РС, що критично для великих проектів, оскільки в процесі роботи модуля пошуку помилок проводяться запити достатку КТ.

Весь арсенал систем для зондової діагностики (ЗД) можна легко адаптувати для верифікації.

Достоїнствами даної структури є:

1. Багаточисельні, вже реалізовані алгоритми зондової діагностики, з адаптацією можуть бутизастосовані для пошуку помилок в проекті, зануреному на ПЛІС. Роль щупа виконує технологія Boundary Scan, що забезпечує доступ до внутрішніх точок проекту, підтримку забезпечує BSDL-надстройка.

2. Проста BSDL-надстройка

3. Традиційні алгоритми зондової діагностики можуть застосуються як для ТЕЗ, так і для верифікації помилок, тобто можна використовувати систему AutoProbe діагностики несправностей ТЕЗ, розроблену в ДОННТУдля верифікації помилок.

Недоліками даної структури є:

1. Інтенсивний трафік між FPGA-платой і інструментальною РС, що може зіграти істотно негативнуроль для великих проектів.

Виводи

У роботі отримані наступні основні результати:

1. Запропоновано три структури системи верифікації ПЗ на базі ідеї зондової діагностики (ЗД) несправностей та є виконаним їх порівняльний аналіз.

2. Вибрана оптимальна структура верифікації і поставлені завдання на розробку ПО.

Список використаної літератури

1. Барашко А.С., Скобцов Ю.А., Сперанский Д.В. Моделирование и тестирование дискретных устройств. — К., Наукова думка, 1992 — c. 28-32.

2. Беннетс Р. Проектирование тестопригодных логических схем. — Пер. с английского. — М.: Радио и связь, 1990 — 176 с.

3. Тарасенко А.Н. Методы оценки и показатели тестируемости дискретных устройств (обзор) // Зарубежная радиоэлектроника, 1989, выпуск 7 — с. 24-29.

4. Зинченко Ю.Е. T—модель дискретного устройства и решение диагностических задач на ее основе. — Электронная библиотека магистра Маркитанова В.Р.

http://www.masters.donntu.ru/2001/fvti/markitantov/diss/library/zinchenko1/index.html, Портал магистров, 2001.

5. Уильямс Т.У., Паркер К.И. Проектирование контролепригодных устройств // ТИИЭР, 1983 — с. 122-139.

6. Техническая диагностика цифровых и микропроцессорных структур: учебник // В.И. Хаханов.— K.: ИСИО, 1995 — 242с.

7. Горяшко А.П. Синтез диагностируемых схем вычислительных устройств. М.: Наука., 1987. – 288 с.

8. Agrawal V.D. Essentials of electronic testing for digital, memory and mixed-signal VLSI circuits. Kluwer Academic Publishers, 2000, — 690c.

9. Автоматизация диагностирования электронных устройств // Ю.В. Малышко, В.П. Чипулис, С.Г. Шаршунов. — М.: Энергоатомиздат, 1986. — 216 с.

10. Соловьев В.В. Проектирование цифровых схем на основе ПЛИС. — М.:Горячая линия-Телеком, 2001. 636с. ил.

11. Ярмолик В.Н. Контроль и диагностика цифровых узлов ЭВМ. — Мн.: Наука и техника. 1988, — 240 с.

12. Давыдов П.С. Техническая диагностика радиоэлектронных устройств и систем. — М.: Радио и связь, 1988. — 256 с.