Реферат по теме выпускной работы

При написании данного автореферата магистерская работа ещё не завершена. Окончательное завершение: декабрь 2014 г. Полный текст работы и материалы по теме могут быть получены у автора после указанной даты.

Содержание

- Введение

- 1. Актуальность темы

- 2. Цель и задачи исследования, планируемые результаты

- 3. Обзор исследований и разработок

- 3.1. Обзор международных источников

- 3.2. Обзор локальных источников

- 4. Моделирование кэша сетевого процессора

- 4.1. Основы моделирования

- 4.2. Моделирование кэша с помощью SimpleScalar

- Выводы

- Список источников

Введение

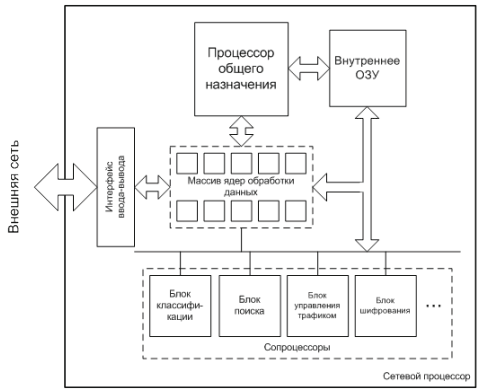

Пропускная способность маршрутизирующего оборудования является важной деталью. Требования, выдвигаемые к современным маршрутизаторам, заставили производителей оборудования использовать специальные сетевые процессоры вместо процессоров общего назначения. Сетевые процессоры выполняют важные функции при обработке сетевых пакетов, а именно: поиск по таблице маршрутизации, фрагментация пакетов обеспечение качества обслуживания и др. На рисунке 1 изображена обобщенная архитектура сетевого процессора.

Рисунок 1 – Обобщенная архитектура сетевого процессора

Для ускорения разработки аппаратного обеспечения, инженеры часто используют программные модели аппаратного обеспечения, которое они производят. Разрабатываются модели с помощью традиционного программирования или языков описания аппаратного обеспечения. На этих моделях можно выполнять программы для проверки производительности и правильности проектирования.

Программисты могут использовать программные модели для разработки и тестирования программного обеспечения еще до того, как аппаратные средства будут доступны. Хотя программные модели работают медленнее, чем их аппаратные аналоги, они позволяют быстро построить и проверить модель без необходимости создания реального оборудования. Такой механизм обеспечивает быструю разработку качественного оборудования.

Развитие программных моделей аппаратного обеспечения движут три основных принципа: производительность, гибкость, детализация. Производительность определяет нагрузку, под которой может работать модель, используя доступные для симуляции машинные ресурсы. Гибкость определяет, насколько хорошо спроектирована модель для дальнейшей модификации. Детализация определяется уровнем абстракции, используемым для реализации компонентов модели. Высокодетализированная модель с большей точностью с эмулирует все аспекты машинных операций.

На практике оптимизировать эти три характеристики не представляется возможным. Поэтому в большинстве программных моделей оптимизированы только одна или две из них. Это объясняет наличие множества симуляторов на сегодняшний день [1].

1. Актуальность темы

Производительность сетевых процессоров зависит от быстродействия алгоритмов анализа пакетов, поэтому поиск новых более эффективных алгоритмов является актуальной задачей. С другой стороны, разработка аппаратных прототипов требует существенных материальных, временных и интеллектуальных затрат. По этой причине важную роль играет имитационное и аналитическое моделирование, способное на ранних этапах разработки выявить узкие места в архитектуре.

2. Цель и задачи исследования

Магистерская работа посвящена исследованию методов построения и анализа многоядерных сетевых процессоров, а также доработке приложения для моделирования SimpleScalar и проведения экспериментов на данных моделях.

Целью работы является увеличение точности моделирования.

Задачами исследования являются:

- Разработка программной модификации SimpleScalar

- Проведение экспериментов с использованием SimpleScalar

- Анализ результатов моделирования

3. Обзор исследований и разработок

Исследуемая тема является популярной как в международном научном сообществе, так и в локальном. Об этом свидетельствует большое количество исследований и разработок.

3.1. Обзор международных источников и разработок

На международном пространстве можно обнаружить не только разнообразные научные статьи на тему моделирования, но и специализированное программное обеспечение для моделирования.

Одним из таких программных продуктов является симулятор SimpleScalar. Симулятор SimpleScalar воспроизводит операции компьютерных устройств всех программных инструкций с использованием интерпретатора. Этот набор инструментов поддерживает популярные наборы команд, включая Alpha, Power PC, x86 и ARM.

В [2] описывается фреймворк моделирования сетевых процессорных систем. В [3] описывается принцип работы набора для измерения производительности NetBench. NetBench содержит в общей сложности 9 приложений для сетевых процессоров.

В [4] предлагается другой симулятор NePSim. Этот симулятор содержит симулятор для типичного сетевого процессора, фреймворк для тестирования и валидации. С его помощью можно рассчитать потребление электроэнергии моделируемого процессора.

3.2. Обзор локальных источников

Исследованиями, связанными с моделированием сетевых процессоров, на территории Украины занимается только ДонНТУ.

В университете такими исследованиями занимается Грищенко В.И., Ладыженский Ю.В., Моатаз Юнис, а также магистры прошлых лет: Мельник Е.В., Моргайлов Д.Д. и Матвиенко М.В.

В.И. Грищенко, Ю.В. Ладыженский, Моатаз Юнис в своей статье [5] описали особенности функций сетевых процессоров, провели анализ современных СП, их технических характеристик и функциональных возможностей, а также предложили обобщенную структуру, отражающую перспективные тенденции в разработке сетевых процессоров.

Комплексная методика моделирования сетевых процессоров, а также недостатки методики и пути её развития приводятся в [6].

Особенности и функции сетевых процессоров, анализ современных СП, их технических характеристик и функциональных возможностей рассмотрены в [7].

В [8] рассматриваются подходы к моделированию сетевых процессоров пакетной обработки данных, предложена модель многоядерного сетевого процессора, в котором объем кэша команд вычислительных ядер достаточен для размещения всего кода выполняемых приложений, а также сравнивается производительность сетевых процессоров с различной организацией блоков памяти.

В [9] рассмотрены подходы к моделированию специализированных многоядерных сетевых процессоров пакетной обработки данных, а также предложена модель сетевого процессора с раздельной памятью для кода и данных.

4. Моделирование кэша сетевого процессора

4.1. Основы моделирования

Типичный подход к моделированию компьютерных систем использует модель простого приближения с хорошей производительностью моделирования и модульной структурой кода. Такой тип симуляторов подходит для исследований, потому что простая модель фокусируется на основных компонентах конструкции, не затрагивая подробно детали, которые могут отрицательно повлиять на производительность и гибкость модели.

С другой стороны, промышленность требует детализированные модели для минимизации конструкционных рисков. Детальное моделирование дает уверенность в том, что оборудование не будет содержать неисправные компоненты и узкие места.

Имитационное моделирование – это метод исследования, при котором изучаемая система заменяется моделью, с достаточной точностью описывающей реальную систему, с которой проводятся эксперименты с целью получения информации об этой системе [10].

Существующие имитационные модели позволяют детально рассмотреть все особенности работы исследуемого процессора и могут использоваться для анализа работы любых приложений и любых входных потоков. Недостатком имитационных моделей является сложность их разработки и узкая специализация. Обычно подобные модели разрабатываются только для одной или нескольких схожих структур, и их модернизация для поддержки других устройств оказывается чрезмерно трудоемкой. В силу этих причин, имитационные модели, в отличие от аналитических, сложно использовать для анализа большого числа структур. Но они позволяют более детально рассмотреть работу всех компонентов процессора, менее требовательны к форме описания входного потока данных и выполняемых приложений.

4.2. Моделирование кэша с помощью SimpleScalar

Кэш – промежуточный буфер с быстрым доступом, содержащий информацию, которая может быть запрошена с наибольшей вероятностью. Доступ к данным в кэше осуществляется быстрее, чем выборка исходных данных из более медленной памяти или удаленного источника, однако её объем существенно ограничен по сравнению с хранилищем исходных данных [11].

При выборе верной модели замещения кэша можно добиться существенного увеличения производительности за счет того, что нужные в данный момент данные будут уже находиться в кэше. На рисунке 2 представлена иерархия запроса на получене данных.

Рисунок 2 – Иерархия запроса на получене данных (анимация: 6 кадров, 10 циклов повторения, 79.1 КБ)

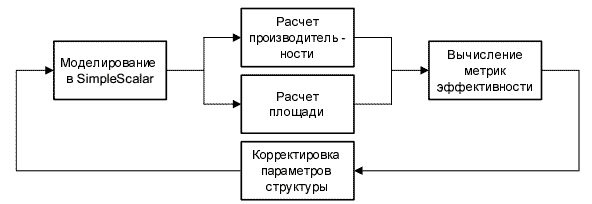

Моделирование начинается с выбора параметров сетевого процессора: число вычислительных ядер, размеры кэшей данных и команд, количество аппаратно поддерживаемых потоков, используемый технологический процесс (для вычисления площади кристалла), выбор тестового приложения. На втором этапе собирается статистика о работе тестового приложения в системе имитационного моделирования SimpleScalar. Система SimpleScalar широко используется в академических исследованиях для моделирования работы процессоров различной структуры и с разными наборами команд. Она позволяет гибко варьировать размеры кэшей, параметры АЛУ, блока предсказаний переходов, задержку доступа к памяти и другие характеристики процессора. На основе полученных данных вычисляется производительность сетевого процессора, они используются для определения степени эффективности моделируемой структуры. После чего корректируются параметры СП и весь цикл моделирования повторяется [12]. Структура моделирования сетевого процессора изображена на рисунке 3.

Рисунок 3 – Структура моделирования сетевого процессора

SimpleScalar содержит интерпретаторы инструкций для набора команд ARM, x86, PPC и Alpha. Интерпретаторы написаны на языке, который обеспечивает комплексный механизм для описания того, как команды изменяют содержание регистров и состояние памяти. Препроцессор использует эти машинные определения чтобы синтезировать интерпретаторы, анализаторы зависимостей и генераторы микрокода, которые необходимы для модели SimpleScalar. С небольшим количеством дополнительных надстроек модели могут поддерживать определенное множество наборов команд.

Модуль эмуляции ввода/вывода обеспечивает имитацию программ, имеющих доступ к устройствам ввода/вывода. SimpleScalar поддерживает несколько модулей эмуляции ввода/вывода, от эмуляции системных вызовов до моделирования системы в целом. Система эмулирует вызов путем перевода его в эквивалентный вызов операционной системы и направляя симулятору на обработку вызов от имени эмулируемой программы. Например, если моделируемая программа пытается открыть файл, модуль эмуляции ввода/вывода транслирует запрос на вызов open() и возвращает полученный дескриптор файла или код ошибки в регистр моделируемой программы.

Другие модули симуляции обеспечивают более детальное моделирование актуальных аппаратных устройств. Например, SimpleScalar/ARM версия включает эмулятор ввода/вывода для устройств Compaq IPaq. Этот эмулятор настолько детализирован, что позволяет загружать операционную систему ARM Linux. Эмуляция ввода/вывода на уровне устройств имеет преимущество для анализа роли операционной системы при выполнении приложения. Это показало себя эффективным в серверных приложениях, где сервисы работы с сетью и файловой системой зависят прежде всего от нагрузки во время выполнения.

В каждой модели код ядра симулятора определяет аппаратную организацию модели. Код симулятора определяет главный цикл, который выполняет одну итерацию для каждой инструкции в программе до окончания выполнения программы. Для синхронной модели главный цикл должен учитывать ход времени исполнения, измеренный в тактах для этой модели. Переменная cycle хранит время выполнения, записанное в количестве тактов, которое потребовалось для выполнения программы до текущей команды.

Модуль cache.c, поставляемый с дистрибутивом SimpleScalar, реализует кэш данных. Модуль кэширования использует хеш-таблицу для записи блоков кэша. Если адрес запроса соответствует записи в хеш-таблице, то такой запрос возвращает попадание в кэш. Если же адрес запроса не содержит записи в хеш-таблице, то запрос возвращает кэш-промах. При этом делается системный вызов обработчика кэш-промаха, который возвращает количество тактов, необходимое для обслуживания кэш-промаха. В модели определяется обработчик промаха, который может быть другим кэш-модулем или моделью DRAM-памяти. Кэш-модуль не возвращает значение, полученное по запросу в кэш, потому что это значение не влияет на латентность доступа кэша. Для конструкций, в которых значение кэша может повлиять на латентность, система может сконфигурировать кэш-модуль таким образом, что он будет возвращать значение по запросу.

В дополнение к стандартным компонентам, SimpleScalar предоставляет разнообразные вспомогательные модули, которые реализуют полезные функции, требуемые во многих моделях. Такие модели включают отладчик, загрузчик программ, процессор командной строки, пакет статистики.

Выводы

Исследование производительности сетевых процессоров является важной задачей, которая позволяет существенно снизить трудовые и временные затраты на разработку и улучшение сетевых процессоров.

Дальнейшая работа будет направлена на доработку программного продукта для моделирования SimpleScalar и проведение экспериментов на моделях многоядерных сетевых процессоров с целью увеличения точности моделирования.

Список источников

- Todd Austin, Eric Larson, Dan Ernst – SimpleScalar: An Infrastructure for Computer System Modeling [Электронный ресурс]. Режим доступа: https://web.eecs.umich.edu/~taustin/papers/IEEEcomp-simplescalar.pdf.

- Patrick Crowley, Jean-Loup Baer – A Modeling Framework for Network Processor Systems [Электронный ресурс]. Режим доступа: http://arl.wustl.edu/~pcrowley/np1.pdf.

- Gokhan Memik, William H. Mangione-Smith, Wendong Hu – NetBench: A Benchmarking Suite for Network Processors [Электронный ресурс]. Режим доступа: http://citeseerx.ist.psu.edu/viewdoc/download?doi=10.1.1.12.8449&rep=rep1&type=pdf.

- Yan Luo, Jun Yang, Laxmi N. Bhuyan, Li Zhao – NePSim: A network processor simulator with a power evaluation framework [Электронный ресурс]. Режим доступа: http://www.cs.ucr.edu/~bhuyan/papers/micro.pdf.

- Грищенко В.И., Ладыженский Ю.В., Моатаз Юнис Основные направления развития современных сетевых процессоров. В сб. Научные труды ДонНТУ. Серия

Информатика, кибернетика и вычислительная техника

. – 2011. – Вып. 14(188). – с. 123–127. - Грищенко В.И., Ладыженский Ю.В. Моделирование работы приложений на сетевых процессорах. // Моделирование и компьютерная графика : Материалы 2-й международной научно-технической конференции, г. Донецк, 10-12 октября 2007 г. — Донецк, ДонНТУ, Министерство образования и науки Украины, 2007. — с. 167-173.

- Грищенко В.И., Ладыженский Ю.В., Моатаз Юнис Перспективные архитектуры и тенденции развития современных сетевых процессоров. // Моделирование и компьютерная графика : Материалы 4-й международной научно-технической конференции, г. Донецк, 5-8 октября 2011 г. — Донецк, ДонНТУ, Министерство образования и науки Украины, 2011. — с. 93-97.

- Грищенко В.И., Ладыженский Ю.В., Моатаз Юнис Влияние выделенного кэша команд на производительность сетевогопроцессора. В сб. Научные труды ДонНТУ. Серия

Информатика, кибернетика и вычислительная техника

. – 2011. – Вып. 13(185). – с. 85-91. - Грищенко В.И., Ладыженский Ю.В. Исследование влияния раздельной памяти на производительность многоядерного сетевого процессора. В сб. Научные труды ДонНТУ. Серия

Проблемы моделирования, и автоматизации проектирования

(МАП-2011). Випуск: 9 (179) – Донецк: ДонНТУ – 2011. – 356 с. - Имитационное моделирование [Электронный ресурс]. Режим доступа: http://ru.wikipedia.org/wiki/Имитационное моделирование.

- Кэш [Электронный ресурс]. Режим доступа: https://ru.wikipedia.org/wiki/%D0%9A%D1%8D%D1%88.

- Грищенко В.И. Оптимизация методики моделирования кэша сетевых процессоров // Моделирование и компьютерная графика: Материалы 3-й международной научно-технической конференции, г. Донецк, 7-9 октября 2009 г. — Донецк: ДонНТУ, Министерство образования и науки Украины, 2009. — C. 249—254.