Реферат за темою випускної роботи

При написанні даного автореферату магістерська робота ще не завершена. Остаточне завершення: грудень 2014. Повний текст роботи та матеріали по темі можуть бути отримані у автора після зазначеної дати.

Зміст

- Вступ

- 1. Актуальність теми

- 2. Мета і завдання дослідження

- 3. Огляд досліджень і розробок

- 3.1. Огляд міжнародних джерел і розробок

- 3.2. Огляд локальних джерел

- 4. Моделювання кеша мережевого процесора

- 4.1. Основи моделювання

- 4.2. Моделювання кеша за допомогою SimpleScalar

- Висновки

- Список джерел

Вступ

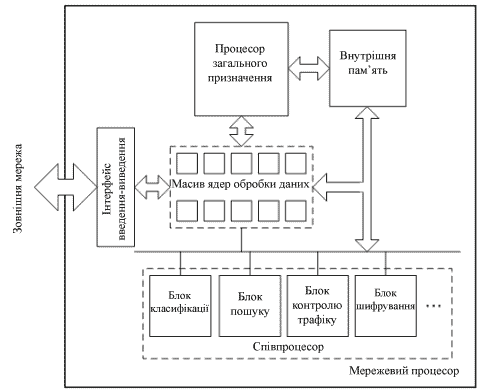

Пропускна здатність маршрутизуючого обладнання є важливою деталлю. Вимоги, що висуваються до сучасних маршрутизаторів, змусили виробників устаткування використовувати спеціальні мережеві процесори замість процесорів загального призначення. Мережеві процесори виконують важливі функції при обробці мережевих пакетів, а саме: пошук по таблиці маршрутизації, фрагментація пакетів забезпечення якості обслуговування та ін. На рисунку 1 зображена узагальнена архітектура мережевого процесора

Рисунок 1 – Узагальнена архітектура мережевого процесора

Для прискорення розробки апаратного забезпечення, інженери часто використовують програмні моделі апаратного забезпечення, яке вони виробляють. Розробляються моделі за допомогою традиційного програмування або мов опису апаратного забезпечення. На цих моделях можна виконувати програми для перевірки продуктивності та правильності проектування.

Програмісти можуть використовувати програмні моделі для розробки та тестування програмного забезпечення ще до того, як апаратні засоби будуть доступні. Хоча програмні моделі працюють повільніше, ніж їх апаратні аналоги, вони дозволяють швидко побудувати і перевірити модель без необхідності створення реального обладнання. Такий механізм забезпечує швидку розробку якісного обладнання.

Розвиток програмних моделей апаратного забезпечення рухають три основних принципи: продуктивність, гнучкість, деталізація. Продуктивність визначає навантаження, під якою може працювати модель, використовуючи доступні для симуляції машинні ресурси. Гнучкість визначає, наскільки добре спроектована модель для подальшої модифікації. Деталізація визначається рівнем абстракції, використовуваним для реалізації компонентів моделі. Високодеталізованими модель з більшою точністю з емулює всі аспекти машинних операцій.

На практиці оптимізувати ці три характеристики не представляється можливим. Тому в більшості програмних моделей оптимізовані тільки одна або дві з них. Це пояснює наявність безлічі симуляторів на сьогоднішній день [1].

1. Актуальність теми

Продуктивність мережевих процесорів залежить від швидкодії алгоритмів аналізу пакетів, тому пошук нових більш ефективних алгоритмів є актуальним завданням. З іншого боку, розробка апаратних прототипів вимагає істотних матеріальних, часових та інтелектуальних витрат. З цієї причини важливу роль відіграє імітаційне та аналітичне моделювання, здатне на ранніх етапах розробки виявити вузькі місця в архітектурі.

2. Мета і завдання дослідження

Магістерська робота присвячена дослідженню методів побудови та аналізу багатоядерних мережевих процесорів, а також доопрацювання програми для моделювання SimpleScalar та проведення експериментів на даних моделях.

Метою роботи є збільшення точності моделювання.

Завданнями дослідження є:

- Розробка програмної модифікації SimpleScalar

- Проведення експериментів з використанням SimpleScalar

- Аналіз результатів моделювання

3. Огляд досліджень і розробок

Досліджувана тема є популярною як в міжнародному науковому співтоваристві, так і в локальному. Про це свідчить велика кількість досліджень і розробок.

3.1. Огляд міжнародних джерел і розробок

На міжнародному просторі можна виявити не тільки різноманітні наукові статті на тему моделювання, а й спеціалізоване програмне забезпечення для моделювання.

Одним з таких програмних продуктів є симулятор SimpleScalar. Симулятор SimpleScalar відтворює операції комп'ютерних пристроїв всіх програмних інструкцій з використанням інтерпретатора. Цей набір інструментів підтримує популярні набори команд, включаючи Alpha, Power PC, x86 і ARM .

В [2] описується фреймворк моделювання мережних процесорних систем. В [3] описується принцип роботи набору для вимірювання продуктивності NetBench. NetBench містить в цілому 9 додатків для мережевих процесорів.

В [4] пропонується інший симулятор NePSim. Цей симулятор містить симулятор для типового мережевого процесора, фреймворк для тестування і валідації. З його допомогою можна розрахувати споживання електроенергії моделируемого процесора.

3.2. Огляд локальних джерел

Дослідженнями, пов'язаними з моделюванням мережевих процесорів, на території України займається тільки ДонНТУ.

В університеті такими дослідженнями займається Грищенко В.І., Ладиженський Ю.В., Моатаз Юніс, а також магістри минулих років: Мельник Е.В., Моргайлов Д.Д. і Матвієнко М.В.

В.І. Грищенко, Ю.В. Ладиженський, Моатаз Юніс у своїй статті [5] описали особливості функцій мережевих процесорів, провели аналіз сучасних СП, їх технічних характеристик і функціональних можливостей, а також запропонували узагальнену структуру, яка відображатиме перспективні тенденції в розробці мережевих процесорів.

Комплексна методика моделювання мережних процесорів, а також недоліки методики та шляхи її розвитку наводяться у [6].

Особливості та функції мережевих процесорів, аналіз сучасних СП, їх технічних характеристик і функціональних можливостей розглянуті в [7].

В [8] розглядаються підходи до моделювання мережевих процесорів пакетної обробки даних, запропонована модель многоядерного мережевого процесора, в якому обсяг кешу команд обчислювальних ядер достатній для розміщення всього коду виконуваних додатків, а також порівнюється продуктивність мережевих процесорів з різною організацією блоків пам'яті.

В [9] розглянуто підходи до моделювання спеціалізованих багатоядерних мережевих процесорів пакетної обробки даних, а також запропонована модель мережевого процесора з роздільною пам'яттю для коду та даних.

4. Моделювання кеша мережевого процесора

4.1. Основи моделювання

Типовий підхід до моделювання комп'ютерних систем використовує модель простого наближення з хорошою продуктивністю моделювання та модульної структурою коду. Такий тип симуляторів підходить для досліджень, тому що проста модель фокусується на основних компонентах конструкції, не чіпаючи детально деталі, які можуть негативно вплинути на продуктивність і гнучкість моделі.

З іншого боку, промисловість вимагає деталізовані моделі для мінімізації конструкційних ризиків. Детальне моделювання дає впевненість у тому, що обладнання не буде містити несправні компоненти і вузькі місця.

Імітаційне моделювання – це метод дослідження, при якому досліджувана система замінюється моделлю, з достатньою точністю описує реальну систему, з якою проводяться експерименти з метою отримання інформації про цю систему [10].

СІснуючі імітаційні моделі дозволяють детально розглянути всі особливості роботи досліджуваного процесора і можуть використовуватися для аналізу роботи будь-яких додатків і будь-яких вхідних потоків. Недоліком імітаційних моделей є складність їх розробки та вузька спеціалізація. Зазвичай подібні моделі розробляються тільки для однієї або декількох схожих структур, і їх модернізація для підтримки інших пристроїв виявляється надмірно трудомісткою. У силу цих причин, імітаційні моделі, на відміну від аналітичних, складно використовувати для аналізу великої кількості структур. Але вони дозволяють більш детально розглянути роботу всіх компонентів процесора, менш вимогливі до форми опису вхідного потоку даних і виконуваних додатків.

4.2. Моделювання кеша за допомогою SimpleScalar

Кеш – проміжний буфер з швидким доступом, що містить інформацію, яка може бути запрошена з найбільшою ймовірністю. Доступ до даних в кеші здійснюється швидше, ніж вибірка початковых даних з більш повільної пам'яті або віддаленого джерела, проте її обсяг істотно обмежений у порівнянні з сховищем вихідних даних [11].

При виборі вірної моделі заміщення кеша можна отримати істотне збільшення продуктивності за рахунок того, що потрібні в даний момент дані будуть вже знаходитися в кеші. На рисунки 2 представлена ієрархія запиту на отримання даних.

Рисунок 2 – Ієрархія запиту на отримання даних (анімація: 6 кадрів, 10 циклів повторення, 79.1 КБ)

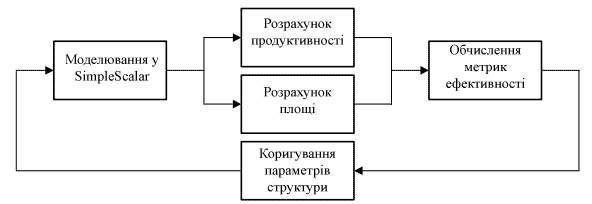

Моделювання починається з вибору параметрів мережного процесора: число обчислювальних ядер, розміри кешей даних і команд, кількість апаратно підтримуваних потоків, використовуваний технологічний процес (для обчислення площі кристала), вибір тестового додатку. На другому етапі збирається статистика про роботу тестового додатку в системі імітаційного моделювання SimpleScalar. Система SimpleScalar широко використовується в академічних дослідженнях для моделювання роботи процесорів різної структури і з різними наборами команд. Вона дозволяє гнучко варіювати розміри кешей, параметри АЛУ, блоку пророкувань переходів, затримку доступу до пам'яті та інші характеристики процесора. На основі отриманих даних обчислюється продуктивність і площа мережевого процесора, вони використовуються для визначення ступеня ефективності модельованої структури. Після чого коригуються параметри СП і весь цикл моделювання повторюється [12]. Структура моделювання мережаного процесора зображена на рисунку 3.

Рисунок 3 – Структура моделювання мережного процесора

SimpleScalar містить інтерпретатори інструкцій для набору команд ARM, x86, PPC і Alpha. Інтерпретатори написані на мові, який забезпечує комплексний механізм для опису того, як команди змінюють зміст регістрів і стан пам'яті. Препроцесор використовує ці машинні визначення щоб синтезувати інтерпретатори, аналізатори залежностей і генератори мі крокода, які необхідні для моделі SimpleScalar. З невеликою кількістю додаткових змін моделі можуть підтримувати певну кількість наборів команд.

Модуль емуляції введення/виведення забезпечує імітацію програм, що мають доступ до пристроїв введення/виводу. SimpleScalar підтримує кілька модулів емуляції введення/виводу, від емуляції системних викликів до моделювання системи в цілому. Система емулює виклик шляхом переведення його в еквівалентний виклик операційної системи і направляючи симулятору на обробку виклик від імені емуліруемой програми. Наприклад, якщо моделируемая програма намагається відкрити файл, модуль емуляції введення/виведення транслює запит на виклик open() і повертає отриманий дескриптор файлу або код помилки в регістр модельованої програми.

Інші модулі симуляції забезпечують більш детальне моделювання актуальних апаратних пристроїв. Наприклад, SimpleScalar/ARM версія включає емулятор введення/виводу для пристроїв Compaq IPaq. Цей емулятор настільки деталізований, що дозволяє завантажувати операційну систему ARM Linux. Емуляція введення/виводу на рівні пристроїв має перевагу для аналізу ролі операційної системи при виконанні програми. Це показало себе ефективним в серверних додатках, де сервіси роботи з мережею і файлової системою залежать насамперед від навантаження під час виконання.

У кожній моделі код ядра симулятора визначає апаратну організацію моделі. Код симулятора визначає головний цикл, який виконує одну ітерацію для кожної інструкції в програмі до закінчення виконання програми. Для синхронної моделі головний цикл повинен враховувати хід часу виконання, виміряний в тактах для цієї моделі. Змінна cycle зберігає час виконання, записане в кількості тактів, який було потрібно для виконання програми до поточної команди.

Модуль cache.c, що поставляється з дистрибутивом SimpleScalar, реалізує кеш даних. Модуль кешування використовує хеш-таблицю для запису блоків кеша. Якщо адреса запиту відповідає запису в хеш-таблиці, то такий запит повертає потрапляння в кеш. Якщо ж адреса запиту не містить записи в хеш-таблиці, то запит повертає кеш-промах. При цьому робиться системний виклик обробника кеш-промаху, який повертає кількість тактів, необхідне для обслуговування кеш-промаху. У моделі визначається обробник промаху, який може бути іншим кеш-модулем або моделлю DRAM-пам'яті. Кеш-модуль не вертає значення, отримане за запитом в кеш, тому що це значення не впливає на латентність доступу кеша. Для конструкцій, в яких значення кеша може вплинути на латентність, система може конфігурувати кеш-модуль таким чином, що він буде повертати значення за запитом.

До стандартних компонентів, SimpleScalar надає різноманітні допоміжні модулі, які реалізують корисні функції, необхідні в багатьох моделях. Такі моделі включають відладчик, завантажувач програм, процесор командного рядка, пакет статистики.

Висновки

Дослідження ефективності мережевих процесорів є важливим завданням, яка дозволяє істотно знизити трудові і тимчасові витрати на розробку і поліпшення мережевих процесорів.

Подальша робота буде спрямована на доробку програмного продукту для моделювання SimpleScalar та проведення експериментів на моделях багатоядерних мережевих процесорів з метою збільшення точності моделювання.

Список джерел

- Todd Austin, Eric Larson, Dan Ernst – SimpleScalar: An Infrastructure for Computer System Modeling [Електронний ресурс]. Режим доступу: https://web.eecs.umich.edu/~taustin/papers/IEEEcomp-simplescalar.pdf.

- Patrick Crowley, Jean-Loup Baer – A Modeling Framework for Network Processor Systems [Електронний ресурс]. Режим доступу: http://arl.wustl.edu/~pcrowley/np1.pdf.

- Gokhan Memik, William H. Mangione-Smith, Wendong Hu – NetBench: A Benchmarking Suite for Network Processors [Електронний ресурс]. Режим доступу: http://citeseerx.ist.psu.edu/viewdoc/download?doi=10.1.1.12.8449&rep=rep1&type=pdf.

- Yan Luo, Jun Yang, Laxmi N. Bhuyan, Li Zhao – NePSim: A network processor simulator with a power evaluation framework [Електронний ресурс]. Режим доступу: http://www.cs.ucr.edu/~bhuyan/papers/micro.pdf.

- Грищенко В.И., Ладыженский Ю.В., Моатаз Юнис Основные направления развития современных сетевых процессоров. В сб. Научные труды ДонНТУ. Серия

Информатика, кибернетика и вычислительная техника

. – 2011. – Вып. 14(188). – с. 123–127. - Грищенко В.И., Ладыженский Ю.В. Моделирование работы приложений на сетевых процессорах. // Моделирование и компьютерная графика : Материалы 2-й международной научно-технической конференции, г. Донецк, 10-12 октября 2007 г. — Донецк, ДонНТУ, Министерство образования и науки Украины, 2007. — с. 167-173.

- Грищенко В.И., Ладыженский Ю.В., Моатаз Юнис Перспективные архитектуры и тенденции развития современных сетевых процессоров. // Моделирование и компьютерная графика : Материалы 4-й международной научно-технической конференции, г. Донецк, 5-8 октября 2011 г. — Донецк, ДонНТУ, Министерство образования и науки Украины, 2011. — с. 93-97.

- Грищенко В.И., Ладыженский Ю.В., Моатаз Юнис Влияние выделенного кэша команд на производительность сетевогопроцессора. В сб. Научные труды ДонНТУ. Серия

Информатика, кибернетика и вычислительная техника

. – 2011. – Вып. 13(185). – с. 85-91. - Грищенко В.И., Ладыженский Ю.В. Исследование влияния раздельной памяти на производительность многоядерного сетевого процессора. В сб. Научные труды ДонНТУ. Серия

Проблемы моделирования, и автоматизации проектирования

(МАП-2011). Випуск: 9 (179) – Донецк: ДонНТУ – 2011. – 356 с. - Имитационное моделирование [Електронний ресурс]. Режим доступу: http://ru.wikipedia.org/wiki/Имитационное моделирование.

- Кэш [Електронний ресурс]. Режим доступу: https://ru.wikipedia.org/wiki/%D0%9A%D1%8D%D1%88.

- Грищенко В.И. Оптимизация методики моделирования кэша сетевых процессоров // Моделирование и компьютерная графика: Материалы 3-й международной научно-технической конференции, г. Донецк, 7-9 октября 2009 г. — Донецк: ДонНТУ, Министерство образования и науки Украины, 2009. — C. 249—254.