|

|

|

Русский

|

English

|

|

|

|

Портал магістрів

|

Сайт ДонНТУ

|

|

Шерекін Олександр Олександрович

|

|

Реферат з теми випускної роботи магістра

Верифікація систем на кристалі на базі технології Boundary Scan |

|

| Зміст | |

|

|

|

| Актуальність роботи | |

|

Процес розробки систем на кристалі (СнК) є тривалим і складним. Він вимагає зусиль великої кількості людей, які проектують як апаратну, так і програмну частину СнК. Через те, що до цього процесу залученно значну кількість проектувальників, поява помилок має досить високу ймовірність. Але найважливішою характеристикою будь-якого продукту є його надійність. Пристрій повинен працювати відповідно до очікувань користувача. Тому одним з етапів процесу розробки СнК є етап верифікації проекту і виявлення помилок. Верифікація і тестування займає в сумі близько 60% від усього часу проектування, що доводить їх важливість [1]. Сучасні темпи розвитку технологій вимагають аналогічного розвитку методів верифікації та тестування. Одним з найбільш поширених способів верифікації був метод зонда, що керується, коли який-небудь аналізатор — зонд — переставляється з однієї частини схеми на іншу і аналізує значення в тій чи іншій частині схеми, роблячи висновок про наявність чи відсутність несправності та правильність роботи схеми.Такий спосіб можна було легко застосовувати для малих та середніх інтегральних схем. Зі збільшенням щільності елементів у схемах, отримати безпосередній доступ до всіх необхідних для аналізу точкам схеми не було можливо, що призвело до необхідності пошуку кардинально нового способу верифікації. І він був знайдений — в 1990 році був прийнятий стандарт IEEE 1149.1-1990 Boundary Scan (BS) [2]. Основною функцією BS було тестування між’єднань інтегральних схем, а також логічних блоків всередині цих схем. Але крім цього даний стандарт виявився придатним для виконання верифікації, відлагодження і тестування, тому що надавав можливості виводити назовні і спостерігати за внутрішніми сигналами схеми. |

|

| Аналіз проблеми | |

|

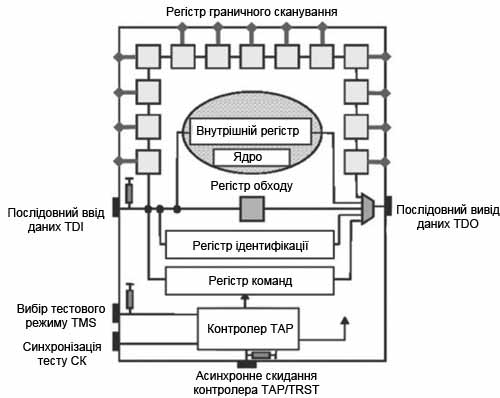

Які ж особливості внесла технологія BS в сферу верифікації та тестування? Яким чином робиться доступним спостереження за внутрішніми сигналами схеми, що тестується? Основою технології BS є додаткова надбудова, яка впроваджується в проект. Функціональний склад цієї надбудови складається з наступних елементів [3]:

Також стандарт BS включає п'ять сигналів для управління протоколом::

Рисунок 1 — Узагальнена схема ІС, яка містить структуру BS Ще одним нововведенням технології BS стала мова опису структур граничного сканування (BSDL — Boundary Scan Description Language). Дана мова використовується для комп'ютерно-орієнтованого опису структури BS обраної ІС та особливостей застосування даної конкретної структури. Файли, написані на цій мові, використовуються в системах автоматичної генерації тестів [4]. BSDL-надбудова може бути автоматично додана до проекту на різних етапах його існування: до виконання процесу синтезу або після нього. Розглядаючи продукти і засоби для верифікації за допомогою BS, що надаються фірмою Xilinx, слід звернути увагу, перш за все, на систему Chip Scope Pro, яка включає:

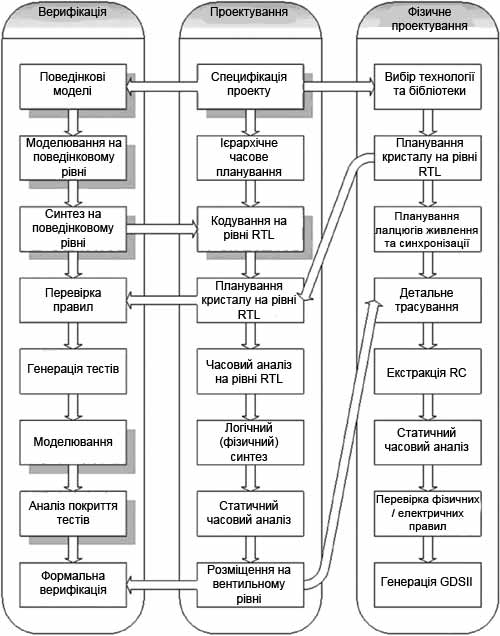

Найбільш важливими IP-ядрами, що входять до складу BSDL-надбудови, є ICON,ILA та VIO. ICON забезпечує інтерфейс між BS-компонентами на ПЛІС і системою Chip Scope Pro. ICON дозволяє підключати такі IP-ядра, як ILA, VIO, в кількості не більше 15 а забезпечує зв'язок TAP-контролера BS з цими ядрами [5]. ILA — логічний аналізатор, що може налаштовуватися. Він використовується для спостереження за станом внутрішніх сигналів схеми, що верифікується. ILA має 16 тригерних портів, кожен з яких складається максимум з 256 сигналів (кількість налаштовується). Процес отримання та збереження даних від підключеної схеми відбувається автоматично при запуску ядра. Але сам момент запуску може бути налаштований необхідним чином. Умовою запуску ядра може бути будь-яка логічна функція, складена з підключених до ядра сигналів. Як тільки зазначена функція буде мати значення істини, всі сигнали з аналізованої схеми будуть записані у внутрішню RAM ILA і передані через ICON та порт JTAG на комп'ютер, де можуть бути відображені в системі Chip Scope. Рисунок 2 показує підключення ILA та ICON [6]. Рисунок 2 — Підключення IP-ядер ILA и ICON VIO дозволяє спостерігати і керувати внутрішніми сигналами схеми, що тестується. VIO має 2 види вхідних і вихідних сигналів — синхронні та асинхронні. У кожній групі може бути від 1 до 256 сигналів. На відміну від ILA, VIO не використовує пам'ять для збереження значень в точках схеми, за якими ведеться спостереження. Група синхронних сигналів використовує внутрішню синхронізацію схеми, група асинхронних синхронізується сигналом від порту JTAG. Вхідні сигнали передаються в аналізатор і відображаються у вигляді діаграми. Вихідні сигнали задаються користувачем і передаються всередину схеми. Рисунок 3 показує підключення VIO та ICON [7]. Рисунок 3 — Підключення IP-ядер VIO и ICON Після розгляду інструментарію, який використовується для верифікації і тестування проектів на базі ПЛІС від Xilinx, слід також визначити місце верифікації в загальному процесі проектування (рис. 4). На початку для реалізації будь-якого проекту, знаючи вимоги, що пред'являються до нього, необхідно розробити еталонну модель, відповідно до якої буде перевірятися остаточний пристрій. Тому на першому етапі створюється поведінкова модель, виходячи із специфікації проекту. Вона моделюється, перевіряється правильність її роботи. Після цього виконується синтез — еталонна модель готова. Окремо від цього виконується створення нової моделі, але вже не в поведінковому, а в структурному, або регістровому (RTL — Register Transfer Level), стилі. На наступному кроці виконується порівняння двох моделей, поведінкової та регістрової. У разі якщо моделі працюють неоднаково, виконується додаткове налагодження регістрової моделі до тих пір, поки робота обох моделей не буде ідентичною. Після цього виконується генерація тестів, які покриють максимальну кількість різноманітних помилок. На даному етапі необхідно зробити вибір на користь того чи іншого алгоритму верифікації і способу генерації тестів. Після закінчення формування тестових впливів і моделювання роботи еталона при подачі їх на схему виконується аналіз покриття тестів. Якщо він не задовольняє вимогам, що пред'являються до проекту, тоді або вибирається інший метод верифікації, або збільшується кількість тестів. Коли цей процес завершиться, виконується занурення синтезованої моделі в ПЛІС, прогонка отриманих тестів і перевірка, чи відповідають результати роботи реальної схеми еталону. |

|

| Цілі і завдання | |

|

Метою даної роботи є розробка методу верифікації систем на кристалі на базі Field Programmable Gate Array (FPGA). Розроблена схема повинна відповідати описаній вище структурі проектування, але більш конкретно розкривати сутність кожного етапу і оптимізувати та полегшити процес тестування та верифікації проектів. Схема, що розробляється, повинна брати до уваги особливості використовуваної технології Boundary Scan і засобів верифікації від Xilinx, ефективно використовувати всі їхні переваги. За допомогою розробленої структури показати весь процес верифікації на прикладі конкретного пристрою. |

|

| Огляд досліджень і розробок з теми | |

|

Матеріали магістрів ДонНТУ

Національний рівень

На сайті мого наукового керівника (Hard Club) можна дізнатися про наукові роботи в галузях, близьких до теми магістерської роботи.

Глобальний рівень

Тематика, визначена в назві магістерської роботи, є, з одного боку, актуальною в світі, але з іншого боку, основна маса робіт по темі не надаються у відкритому доступі. Доступ надається лише до коротких оглядів статей. З невеликої кількості доступних матеріалів варто звернути увагу на публікації [8] та [9]. У першій з цих публікацій описується вдосконалена структура BS-регістрів, яка дозволяє економити місце на кристалі за рахунок зменшення кількості внутрішніх регістрів, що використовуються, а також прискорити роботу BS, за рахунок розпаралелювання процесу обміну даними. У другій публікації описується новий метод для виявлення несправностей в PLD (Programmable Logic Device) і FPGA, використовуючи технологію BS. З російськомовних джерел слід виділити статтю [10]. У зазначеній статті описуються сучасні засоби функціональної верифікації. |

|

| Результати, отримані на момент написання реферату | |

|

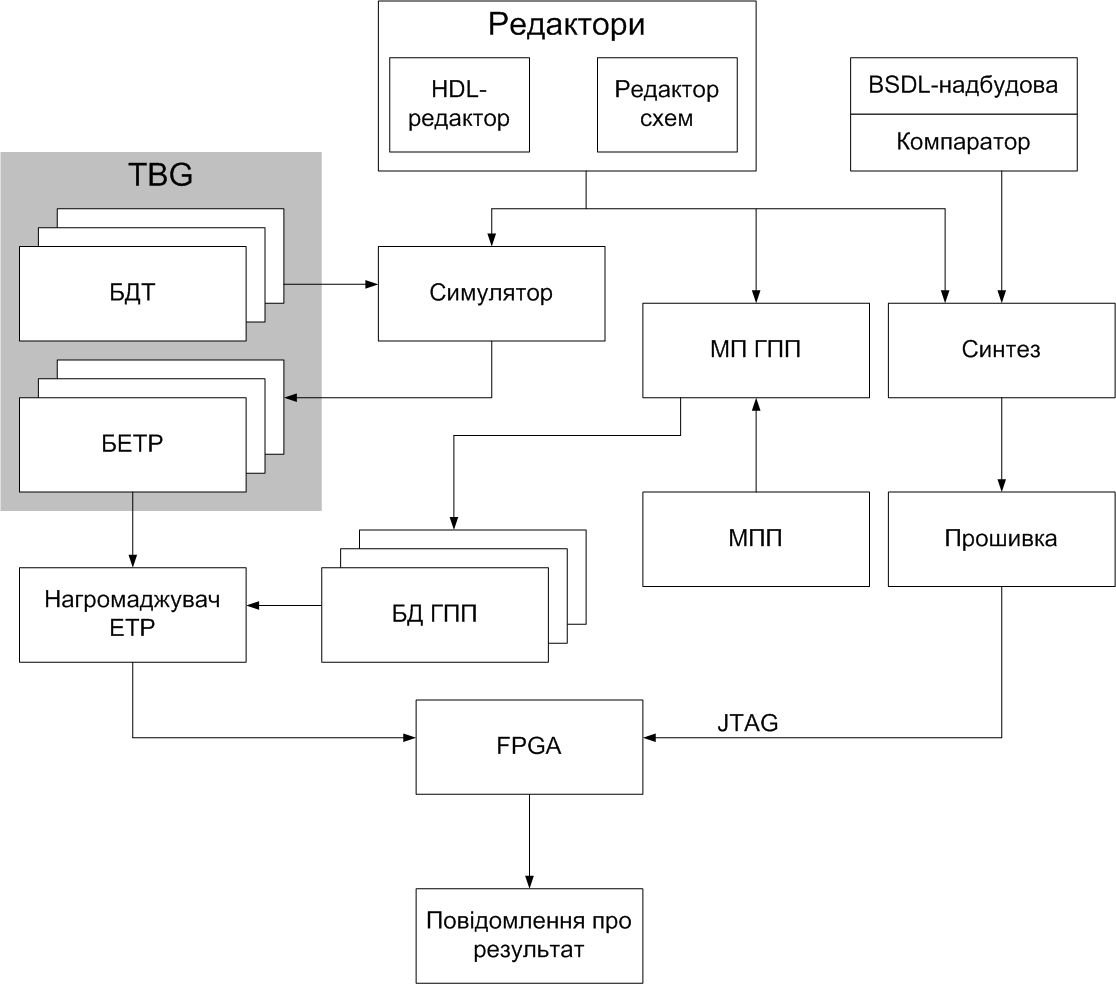

На даний момент була розроблена структура, згідно з якою буде виконуватися подальша верифікація проекту. Структура розробленої схеми наведена на рисунку 5.

Рисунок 5 — Схема верифікації систем на кристалі на базі FPGA Наведену структуру можна розділити на кілька основних частин / етапів виконання перевірки:

Перевагами такого підходу є невеликий об'єм трафіку, що передається між FPGA і персональним комп'ютером через те, що аналіз контрольних точок буде виконуватися всередині ПЛІС, і швидкий доступ до контрольних точок. До недоліків можна віднести неможливість легкої заміни алгоритму пошуку помилок, тому що він жорстко зашитий в ПЛІС і для його заміни необхідно перепрошити ПЛІС. Але з іншого боку, перепрошивка не є складним процесом, що дозволяє говорити про цю структуру як про рекомендовану до використання. |

|

| Література | |

|

|

|

|

|

| При написанні даного реферату магістерська робота ще не завершена. Остаточне завершення: грудень 2012. Повний текст роботи та матеріали з теми можуть бути отримані у автора або його керівника після зазначеної дати. | |