|

|

|

Українська

|

English

|

|

|

|

Портал магистров

|

Сайт ДонНТУ

|

|

Шерекин Александр Александрович

|

|

Реферат по теме выпускной работы магистра

Верификация систем на кристалле на базе технологии Boundary Scan |

|

| Содержание | |

|

|

|

| Актуальность работы | |

|

Процесс разработки систем на кристалле (СнК) является длительным и сложным. Он требует усилий большого количества людей, проектирующих как аппаратную, так и программную часть СнК. Из-за привлечения в этот процесс значительного количества проектировщиков появление ошибок имеет достаточно высокую вероятность. Но ведь самой важной характеристикой любого продукта является его надежность. Устройство должно работать в соответствии с ожиданиями пользователя. Поэтому одним из этапов процесса разработки СнК является этап верификации проекта и обнаружения ошибок. Верификация и тестирование занимает в сумме около 60% от всего времени проектирования, что доказывает их важность [1]. Современные темпы развития технологий требуют аналогичного развития и методов верификации и тестирования. Одним из наиболее распространенных способов верификации являлся метод ведомого зонда, когда некий анализатор — зонд — переставлялся из одной части схемы на другую и анализировал значения в той или иной части схемы, делая вывод о наличии либо отсутствии неисправности и правильности работы схемы. Такой способ можно легко было применять для малых и средних интегральных схем. С увеличением плотности элементов, получить непосредственный доступ ко всем необходимым для анализа точкам схемы не представлялось возможным, что привело к необходимости поиска кардинально нового способа верификации. И он был найден — в 1990 году был принят стандарт IEEE 1149.1-1990 Boundary Scan (BS) [2]. Основной функцией BS являлось тестирование межсоединений интегральных схем, а также логических блоков внутри этих схем. Но кроме этого данный стандарт оказался пригодным для выполнения верификации, отладки и тестирования, потому что предоставлял возможности выводить наружу и наблюдать за внутренними сигналами схемы. |

|

| Анализ проблемы | |

|

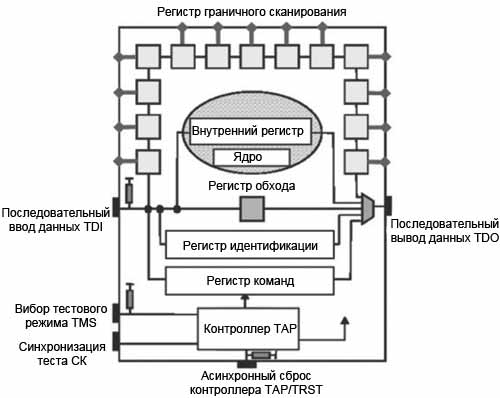

Какие же особенности привнесла технология BS в сферу верификации и тестирования? Каким образом делается доступным наблюдение за внутренними сигналами тестируемой схемы? Основой технологии BS является дополнительная надстройка, которая внедряется в проект. Функциональный состав этой надстройки состоит из следующих элементов [3]:

Также стандарт BS подразумевает наличие пяти сигналов для управления протоколом:

Рисунок 1 — Обобщенная схема ИС, содержащей структуру BS

Рисунок 2 — Принцип работы технологии BS (анимация, 17 кадров, 102 кБ, интервал между кадрами 1 с) Еще одним нововведением технологии BS стал язык описания структур граничного сканирования (BSDL — Boundary Scan Description Language). Данный язык используется для компьютерно-ориентированного описания структуры BS выбранной ИС и особенностей применения данной конкретной структуры. Файлы, написанные на этом языке, используются в системах автоматической генерации тестов [4]. BSDL-надстройка может быть автоматически добавлена к проекту на различных этапах его существования: до выполнения процесса синтеза либо после. Рассматривая продукты и средства для верификации посредством BS, предоставляемые фирмой Xilinx, следует отметить, прежде всего, систему Chip Scope Pro, которая включает:

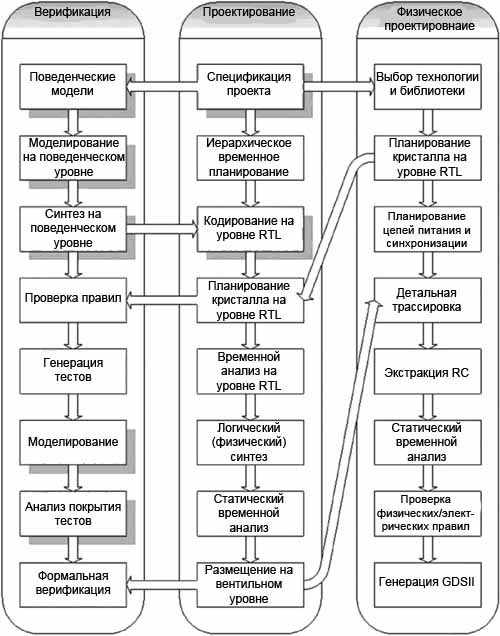

Наиболее важными IP-ядрами, входящими в состав BSDL-надстройки, являются ICON, ILA и VIO. ICON обеспечивает интерфейс между BS-компонентами на ПЛИС и системой Chip Scope Pro. ICON позволяет подключать такие IP-ядра, как ILA, VIO, в количестве не более 15 и обеспечивает связь TAP-контроллера BS с этими ядрами [5]. ILA — настраиваемый логический анализатор, который используется для наблюдения за состоянием внутренних сигналов верифицируемой схемы. ILA имеет 16 триггерных портов, каждый из которых состоит максимум из 256 сигналов (количество настраиваемо). Процесс получения и сохранения данных от подключенной схемы происходит автоматически при запуске ядра. Но сам момент запуска может быть настроен необходимым образом. Условием запуска ядра может быть любая логическая функция, составленная из подключенных к ядру сигналов. Как только указанная функция будет иметь значение истины, все сигналы из анализируемой схемы будут записаны во внутреннюю RAM ILA и переданы через ICON и порт JTAG на компьютер, где могут быть отображены в системе Chip Scope. Рисунок 3 показывает подключение ILA и ICON [6]. Рисунок 3 — Подключение IP-ядер ILA и ICON VIO позволяет наблюдать и управлять внутренними сигналами тестируемой схемы. VIO имеет 2 вида входных и выходных сигналов — синхронные и асинхронные. В каждой группе может быть от 1 до 256 сигналов. В отличие от ILA, VIO не использует память для сохранения значений в наблюдаемых точках схемы. Группа синхронных сигналов использует внутреннюю синхронизацию схемы, группа асинхронных синхронизируется сигналом от порта JTAG. Входные сигналы передаются в анализатор и отображаются в виде диаграммы. Выходные сигналы задаются пользователем и передаются внутрь схемы. Рисунок 4 показывает подключение VIO и ICON [7]. Рисунок 4 — Подключение IP-ядер VIO и ICON Рассмотрев инструментарий, используемый для верификации и тестирования проектов с использованием ПЛИС от Xilinx, следует также определить место верификации в общем процессе проектирования (рис. 5). В начале для реализации какого-либо проекта, зная требования, предъявляемые к нему, необходимо разработать эталонную модель, в соответствии с которой будет проверяться окончательное устройство. Поэтому на первом этапе создается поведенческая модель, исходя из спецификации проекта. Она моделируется, проверяется правильность ее работы. После этого выполняется синтез — эталонная модель готова. Отдельно от этого выполняется создание новой модели, но уже не в поведенческом, а в структурном, или регистровом (RTL — Register Transfer Level), стиле. На следующем шаге выполняется сравнение двух моделей, поведенческой и регистровой. В случае если модели работают неодинаково, выполняется дополнительная отладка регистровой модели до тех пор, пока работа обоих моделей не будет идентичной. После этого выполняется генерация тестов, которые покроют максимальное количество всевозможных ошибок. На данном этапе необходимо сделать выбор в пользу того или иного алгоритма верификации и способа генерации тестов. По окончании формирования тестовых воздействий и моделирования работы эталона при подаче их на схему выполняется анализ покрытия тестов. Если он не удовлетворяет требованиям, предъявляемым к проекту, то либо выбирается другой метод верификации, либо увеличивается количество тестов. Когда этот процесс завершится, выполняется погружение синтезированной модели в ПЛИС, прогонка полученных тестов и проверка, соответствуют ли результаты работы реальной схемы эталону. |

|

| Цели и задачи | |

|

Целью данной работы является разработка метода верификации систем на кристалле на базе Field Programmable Gate Array (FPGA). Разработанная схема должна соответствовать описанной выше структуре проектирования, но более конкретно раскрывать суть каждого этапа и оптимизировать и облегчить процесс тестирования и верификации проектов. Разрабатываемая схема должна принимать во внимание особенности используемой технологии Boundary Scan и средств верификации от Xilinx, эффективно использовать все их достоинства. С помощью разработанной структуры показать весь процесс верификации на примере конкретного устройства. |

|

| Обзор исследований и разработок по теме | |

|

Материалы магистров ДонНТУ

Национальный уровень

На сайте моего научного руководителя (Hard Club) можно узнать о научных работах в областях, близких к теме магистерской работы.

Глобальный уровень

Тематика, определенная в названии магистерской работы, является, с одной стороны, актуальной в мире, но с другой стороны, основная масса работ по теме не предоставляются в открытом доступе. Доступ предоставляется только к кратким обзорам статей. Из небольшого количества доступных материалов стоит обратить внимание на публикации [8] и [9]. В первой из этих публикаций описывается усовершенствованная структура BS-регистров, которая позволяет экономить место на кристалле за счет уменьшения количества используемых внутренних регистров, а также ускорить работу BS, за счет распараллеливания процесса обмена данными. Во второй публикации описывается новый метод для обнаружения неисправностей в PLD (Programmable Logic Device) и FPGA, используя технологию BS. Из русскоязычных источников следует выделить статью [10]. В указанной статье описываются современные средства функциональной верификации. |

|

| Результаты, полученные на момент написания реферата | |

|

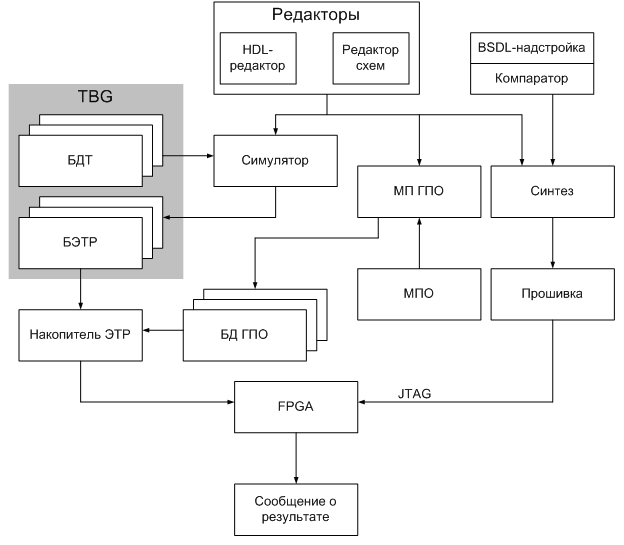

На данный момент была разработана структура, согласно которой будет выполняться дальнейшая верификация проекта. Структура разработанной схемы приведена на рисунке 6.

Рисунок 6 — Схема верификации систем на кристалле на базе FPGA Приведенную структуру можно разделить на несколько основных частей / этапов выполнения проверки:

Достоинствами данного подхода является небольшой объем трафика, передаваемый между FPGA и персональным компьютером по причине того, что анализ контрольных точек будет выполняться внутри ПЛИС, и быстрый доступ к контрольным точкам К недостаткам же можно отнести невозможность легкой замены алгоритма поиска ошибок, потому что он жестко зашит в ПЛИС и для его замены необходимо перепрошить ПЛИС. Но с другой стороны, перепрошивка не является сложным процессом, что позволяет говорить о данной структуре как о рекомендуемой к использованию |

|

| Литература | |

|

|

|

|

|

| При написании данного реферата магистерская работа еще не завершена. Окончательное завершение: декабрь 2012. Полный текст работы и материалы по теме могут быть получены у автора или его руководителя после указанной даты. | |