Астахов Евгений Александрович

Факультет вычислительной техники и информатики

Кафедра электронных вычислительных машин

Специальность: Системное программирование

Тема выпускной работы:

Разработка и исследование метода верификации FPGA проектов по методологии ведомого зонда на базе технологии Boundary Scan

Научный руководитель: Зинченко Юрий Евгеньевич

Введение

Как известно, процесс проектирования вычислительных устройств сопровождается отладкой (верификацией) на всех этапах проектирования. Верификация современных сложных устройств по статистике занимает 75-80% от общего времени проектирования с тенденцией к ухудшению этого параметра. Особенно остро проблема верификации стоит на аппаратном уровне (внутрисхемная верификация), т.е. когда проект опускается в целевое устройство (БИС, СБИС), поэтому тема работы направленная на разработку методов и средств верификации проектов, погруженных в программируемо-логическую интегральную схему (ПЛИС, FPGA), является актуальной.

Фундаментальной технологической основой для предлагаемого способа верификации является технология «граничного сканирования» (Boundary Scan — BS). Разработанная изначально с целью контролепригодного проектирования и диагностики БИС, эта технология нашла также применение при программировании и верификации современных ПЛИС. В целом технология BS обеспечивает доступ к внутренним точкам БИС через специально организованный порт JTAG (Joint Test Advanced Group), однако она не дает ответа на то, как тестировать микросхему или верифицировать проект, находящийся в ней. Для ответа на этот вопрос в данной работе предлагается использовать методологию зондовой диагностики, применяемую для традиционных цифровых устройств. Совместное использование технологии BS и методологии зондовой диагностики (ЗД) цифровых устройств (ЦУ) позволяет обеспечить доступ с целью анализа к внутренним контрольным точкам проекта в целевой микросхеме, определяемых алгоритмом зондирования.

Зондовая диагностика была очень популярна в 80-х годах. В 90-е годы, с ростом популярности ПЛИС на основе микросхем в корпусах типа BGA, резко ограничился доступ к контактам микросхем, ввиду того, что контакты микросхем расположены на недоступной стороне микросхемы, что делает затруднительным применение традиционного метода зондовой диагностики с помощью щупа. Поэтому зондовая диагностика стремительно теряла свои позиции. В настоящие время проекты опустились в ПЛИС, а технология Boundary Scan обеспечивает доступ к внутренним точкам схемы, что позволяет вернуться к идеям зондовой диагностики на качественно новом внутрисхемном уровне.

Данная работа направлена на разработку алгоритмов верификации путем адаптации и совершенствования алгоритмов и подходов зондовой диагностики.

Предметом исследования являются алгоритмы верификации проектов погруженных в ПЛИС на основе адаптации методов, идей и подходов зондовой диагностики.

Цель и задачи исследования. Целью работы является разработка эффективных алгоритмов верификации проектов, обеспечивающих быстрый способ поиска возможных ошибок проектирования с максимально возможной степенью локализации.

Для достижения поставленной цели в работе решаются следующие задачи:

1. Адаптация базового алгоритма SCAN поиска неисправностей по методу ведомого зонда для верификации проектов, описанных в структурном HDL-стиле.

2. Разработка программно-аппаратных средств верификации FPGA проекта по методологии ведомого зонда.

3. Экспериментальное исследование алгоритмов и структур верификации FPGA-проектов по методологии ведомого зонда.

Обзор исследований и разработок по теме «Разработка и исследование метода верификации FPGA проектов по методологии ведомого зонда на базе технологии Boundary Scan»

Региональный уровень:

Материалы магистров ДонНТУ

1. http://masters.donntu.ru/2002/fvti/miroshnikov/diss/index.htm

«Разработка алгоритмов тестирования FPGA-устройств по технологии переферийного сканирования»

Автор: Мирошников Александр Сергеевич

Научный руководитель: к.т.н., доцент каф. ЭВМ ДонНТУ Зинченко Ю.Е.

2. http://masters.donntu.ru/2008/fvti/svistunov/diss/index.html

«Исследование и разработка на FPGA SPP-архитектуры поста контроля цифровых устройств»

Автор: Cвистунов Сергей Николаевич

Научный руководитель: к.т.н., доцент каф. ЭВМ ДонНТУ Зинченко Ю.Е.

3. http://masters.donntu.ru/2006/fvti/bobrovskyy/diss/index.htm

«Разработка структуры поста контроля зондовой диагностики ТЭЗ на базе HDL- и FPGA-технологий»

Автор: Бобровский Константин Викторович

Научный руководитель: к.т.н., доцент каф. ЭВМ ДонНТУ Зинченко Ю.Е.

4. http://masters.donntu.ru/2006/fvti/myadelets/diss/index.htm

«Разработка и исследование метода синтеза тестов для типовых элементов замены (ТЭЗ)»

Автор: Мяделец Александр Александрович

Научный руководитель: к.т.н., доцент каф. ЭВМ ДонНТУ Зинченко Ю.Е.

5. http://masters.donntu.ru/2002/fvti/rytov/dissert.htm

«Разработка диагностической модели FPGA - устройств и синтез тестов на ее основе»

Автор: Рытов Александр Сергеевич

Научный руководитель: к.т.н., доцент каф. ЭВМ ДонНТУ Зинченко Ю.Е.

6. http://masters.donntu.ru/2005/fvti/mukha/diss/index.htm

«Исследование реализаций MPEG2 видеопроцессоров на FPGA и PRUS»

Автор: Муха Евгений Михайлович

Научный руководитель: к.т.н., доцент каф. ЭВМ ДонНТУ Зинченко Ю.Е.

7. http://masters.donntu.ru/2004/fvti/korchenko/diss/index.htm

«Розробка способів рішення HDL-задач і системи тестування знань на їх основі»

Автор: Корченко Александр Александрович

Научный руководитель: к.т.н., доцент каф. ЭВМ ДонНТУ Зинченко Ю.Е.

Национальный уровень:

На этом уровне работы в области темы магистерской работы представлены работами моего научного руководителя. По этому линку http://hardclub.donntu.ru/zinchenko/science.htm можно узнать о научных разработках на данном этапе.

Глобальный уровень:

В мире данной проблемой занимаются намного интенсивнее.

На сайте IEEE Xplore содержится большое количесвто научных статей, в том числе и по данной тематике. Однако в свободном доступе представлены лишь краткие обзоры и выводы статей, а основное содержание доступно только зарегистрированным пользователям.

В этой статье http://www.soccentral.com/PrintPage.asp?PassedEntryID=13186 структурно описаны идеи в направлении которых отрасль развивается сегодня. Этот подход актуален.

В настоящее время не имеется подобных программных реализаций данного метода диагностики, предполагаемого темой магистерской работы или, по крайней мере, они находятся в закрытом доступе.

Основное содержание работы

На рисунке 1 приведена анимация существующих алгоритмов поиска неисправностей.

Рисунок 1 — Алгоритмы поиска неисправностей (анимация, 17 кадров, 3 цикла, 146 Кбайт).

Как известно, существует несколько алгоритмов ЗД, таких как алгоритм последовательного зондирования (Scan), алгоритм половинного деления (Galop) и комбинированный алгоритм (Galop + Scan), основанный на сочетании первых двух алгоритмов. Все эти алгоритмы могут быть применены и в случае внутрисхемной верификации.

Она включает стандартные программные средства фирмы Xilinx и специальное ПО зондового диагностирования, разрабатываемая автором работы. Стандартные средства построены на ChipScope – подсистеме BS фирмы Xilinx . Сюда входят следующие компоненты:

1. Core Generator — генератор IP ядер ICON, ILA и других, которые реализуют механизмы BS – используется для создания BSDL-надстройки проекта путем внедрения IP ядер в исходный код проекта пользователя перед этапом синтеза.

2. Core Inserter — компоновщик IP ядер – используется для альтернативного построения BSDL-надстройки проекта, которая внедряется в исходный проект пользователя после его синтеза.

3. Core Analyzer — анализатор IP ядер – используется как вспомогательное средство для визуального анализа тестовых реакций во внутренних контрольных точках проекта, погруженного в ПЛИС.

В работе предусматривается разработать и сравнить несколько структур программного обеспечения системы верификации объекта проектирования, выявить сильные и слабые стороны каждого технического решения, сделать выводы о лучшей структуре для её внедрения.

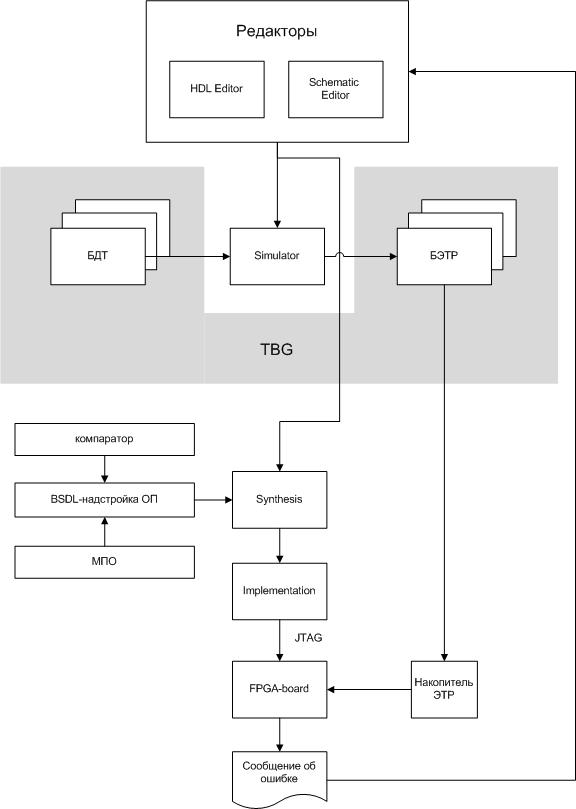

На рисунке 2 показана система верификации FPGA-проектов со встроенным алгоритмом зондирования

Рисунок 2 — Система верификации FPGA-проектов со встроенным алгоритмом зондирования

Описание структуры:

Работа начинается с создания проекта в редакторах:

1. HDL Editor — создание программного кода в структурном HDL-стиле

2. Schematic Editor — создание схемы в графическом виде, используя готовую библиотеку компонент

После этого созданный проект необходимо отладить, исключив из него простые логические ошибки. Для этого проект, созданный в редакторах передается в блок Simulator, где прогоняется через набор тестов, который обеспечивает блок TBG - Test Bench Generator.

Этот блок TBG содержит в своем наборе базу данных тестов (БДТ), которыми испытывается созданный проект. А также базу эталонных тестовых реакций (БЭТР) - результаты тестирования проекта в блоке Simulator. Для создания базы данных тестов может быть использовано ПО PRTG, разработанное в ДонНТУ на кафедре ЭВМ. Набор тестов может быть создан вручную исходя из спецификаций проекта.

После отладки проект передается в блок Synthesis. На этом этапе с проектом соединяется BSDL-надстройка объекта проектирования (BSDL - Boundary Scan Description Language), которая состоит из:

1. компаратор — блок, выполняющий сравнение состояния контрольных точек (КТ) с базой эталонных тестов реакций (БЭТР), которая получена в блоке TBG.

2. МПО — модуль поиска ошибок, представленный в виде BSDL.

Оба этих блока в виде BSDL-надстройки соединяются с проектом на этапе Synthesis.

Далее проект проходит стадию Implementation, которая подразумевает стадию создания модели. На выходе блока Implementation получаем bitstream, состоящий из исходного проекта и BSDL-надстройки, содержащей модуль поиска ошибок.

Используя кабель JTAG, bitstream погружается на отладочную плату FPGA (FPGA-board), например Altera DE2 board. К этой плате через внешний разъем (к примеру USB) подключен накопитель эталонных тестовых реакций (накопитель ЭТР), информация на котором записывается на PC, используя данные базы эталонных тестовых реакций (БЭТР).

После начала работы отладочной FPGA-платы, алгоритмы поиска ошибок, реализованные в виде модуля поиска ошибок BSDL-надстройки начнут свою работу.

Они будут выполнять зондирование. В соответствии с алгоритмом выбрается первая контрольная точка (КТ), считывается тестовая реакция, сравнивается с эталоном, который выбирается из базы эталонных тестовых реакций (БЭТР). Находится момент первого несовпадения. В зависимости от этого принимается решение: верная реакция или неверная. Далее выбирается следующая контрольная точка (КТ) или другая КТ.

Работа алгоритма продолжается до тех пор, пока не будет найдена компонента, которая будет признана ошибочной. На монитор будет выдано сообщение с идентификацией этой компоненты, что послужит информацией для проектировщика для исправления своего исходного кода.

Достоинствами описанной выше структуры являются:

1. Уменьшение траффика передаваемой информации о значения контрольных точек (КТ) между ПЛИС и PC, т.к. эта информация обрабатывается в ПЛИС.

2. Быстрый доступ к контрольным точкам (КТ) без необходимости внешнего взаимодействия.

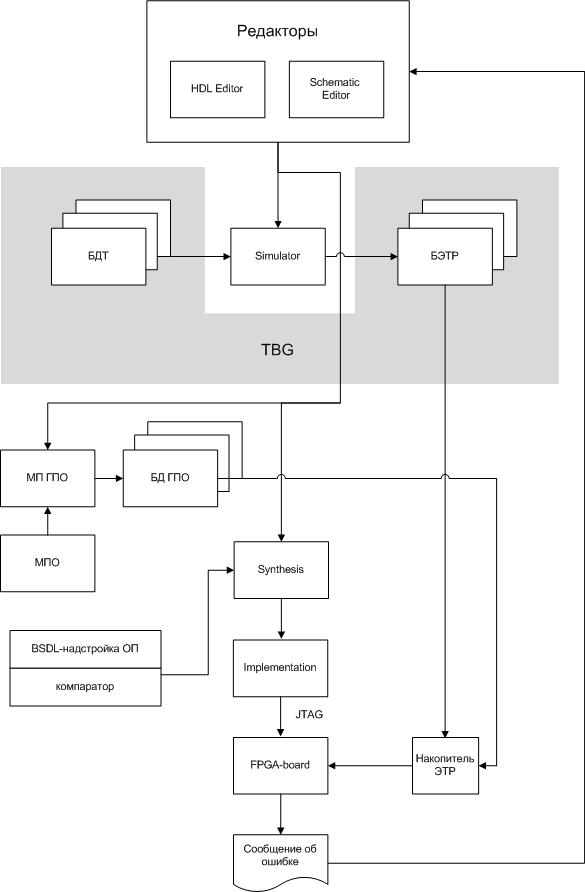

На рисунке 3 показана система верификации FPGA-проектов на базе ГПО

Рисунок 3 — Система верификации FPGA-проектов на базе ГПО

В этой структуре добавлен блок модуля построения графа поиска ошибок (МП ГПО). Данный блок получает информацию от блока TBG и использует модуль поиска ошибок (МПО) для того чтобы сформировать базу данных графов поиска ошибок (БД ГПО), которая затем записывается на накопитель ЭТР.

На предварительном этапе строится база данных графов поиска ошибок (БД ГПО).

Данная структура выгодно отличается тем, что в BSDL-надстройку не внедряется модуль поиска ошибок (МПО), а внедренный компаратор работает с БД ГПО, реализованной по однотипному формату, вне зависимости от алгоритма поиска ошибок.

Остальные этапы аналогичны предыдущей структуре.

Достоинствами данной структуры являются:

1. Для реализации нового алгоритма поиска ошибок в данной системе ПО, необходимо переписать только блок модуля построения графа поиска ошибок.

2. Уменьшение траффика передаваемой информации о значения контрольных точек (КТ) между ПЛИС и PC, т.к. эта информация обрабатывается в ПЛИС.

3. Быстрый доступ к контрольным точкам (КТ) без необходимости внешнего взаимодействия.

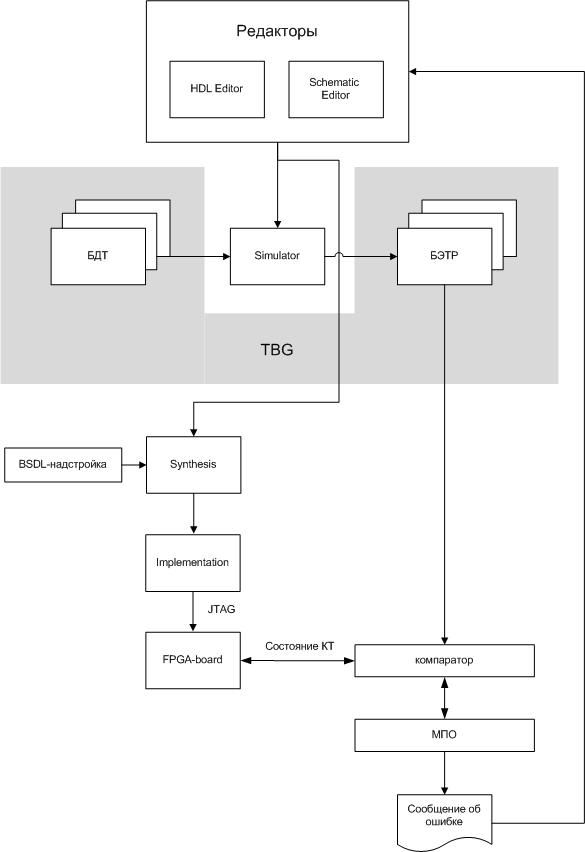

На рисунке 4 показана система верификации FPGA-проектов с внешним алгоритмом зондирования

Рисунок 4 — Система верификации FPGA-проектов с внешним алгоритмом зондирования

Целью этой структуры является предельное упрощение BSDL-надстройки, т.к. на нее возлагаются только функции изъятия контрольной точки (КТ), указанные извне. Все остальные функции реализуются в PС: поиск ошибок, компаратор.

Однако реализация такого подхода требует увеличение траффика между FPGA и PC, что критично для больших проектов, т.к. в процессе работы модуля поиска ошибок производятся запросы состояния КТ.

Весь арсенал систем для зондовой диагностики (ЗД) можно легко адаптировать для верификации.

Достоинствами данной структуры являются:

1. Многочисленные, уже реализованные алгоритмы зондовой диагностики, с адаптацией могут быть применены для поиска ошибок в проекте, погруженном на ПЛИС. Роль щупа выполняет технология Boundary Scan, обеспечивающая доступ к внутренним точкам проекта, поддержку обеспечивает BSDL-надстройка.

2. Простая BSDL-надстройка

3. Традиционные алгоритмы зондовой диагностики могут применятся как для ТЭЗ, так и для верификации ошибок, т.е. можно использовать систему AutoProbe диагностики неисправностей ТЭЗ, разработанную в ДонНТУ, для верификации ошибок.

Недостатками данной структуры являются:

1. Интенсивный траффик между FPGA-платой и инструментальной PC, что может сыграть существенно негативную роль для больших проектов.

Выводы

В работе получены следующие основные результаты:

1. Предложены три структуры системы верификации ПО на базе идеи зондовой диагностики (ЗД) неисправностей и выполнен их сравнительный анализ.

2. Выбрана оптимальная структура верификации и поставлены задачи на разработку ПО.

Список использованной литературы

1. Барашко А.С., Скобцов Ю.А., Сперанский Д.В. Моделирование и тестирование дискретных устройств. — К., Наукова думка, 1992 — c. 28-32.

2. Беннетс Р. Проектирование тестопригодных логических схем. — Пер. с английского. — М.: Радио и связь, 1990 — 176 с.

3. Тарасенко А.Н. Методы оценки и показатели тестируемости дискретных устройств (обзор) // Зарубежная радиоэлектроника, 1989, выпуск 7 — с. 24-29.

4. Зинченко Ю.Е. T—модель дискретного устройства и решение диагностических задач на ее основе. — Электронная библиотека магистра Маркитанова В.Р.

http://www.masters.donntu.ru/2001/fvti/markitantov/diss/library/zinchenko1/index.html, Портал магистров, 2001.

5. Уильямс Т.У., Паркер К.И. Проектирование контролепригодных устройств // ТИИЭР, 1983 — с. 122-139.

6. Техническая диагностика цифровых и микропроцессорных структур: учебник // В.И. Хаханов.— K.: ИСИО, 1995 — 242 с.

7. Горяшко А.П. Синтез диагностируемых схем вычислительных устройств. М.: Наука., 1987. – 288 с.

8. Agrawal V.D. Essentials of electronic testing for digital, memory and mixed-signal VLSI circuits. Kluwer Academic Publishers, 2000, — 690 c.

9. Автоматизация диагностирования электронных устройств // Ю.В. Малышко, В.П. Чипулис, С.Г. Шаршунов. — М.: Энергоатомиздат, 1986. — 216 с.

10. Соловьев В.В. Проектирование цифровых схем на основе ПЛИС. — М.:Горячая линия-Телеком, 2001. 636 с. ил.

11. Ярмолик В.Н. Контроль и диагностика цифровых узлов ЭВМ. — Мн.: Наука и техника. 1988, — 240 с.

12. Давыдов П.С. Техническая диагностика радиоэлектронных устройств и систем. — М.: Радио и связь, 1988. — 256 с.