Перевод части тематической статьи «Functional Verification of 622-Mbps–6.375-Gbps Transceiver IP in an FPGA» с английского языка.

Источник: http://www.altera.com/literature/cp/cp-trnscvr.pdf

Автор: Ning Xue

Перевод: Астахов Е.А.

DesignCon 2006

Функциональная Проверка IP Приемопередатчика 622-Mbps-6.375-Gbps в FPGA

Ning Xue, Корпорация Altera [nxue@altera.com]

(Ramanand Venkata, Arch Zaliznyak, Divya

Vijayaraghavan, Steve Park, Chong Lee, Rakesh Patel)

(Корпорация Altera)

CP-TRNSCVR-1.0

Резюме

Процесс подтверждения IP с перестраиваемой конфигурацией является более сложным и отнимающим много времени чем дизайн IP. Эта работа рассматривает функциональную методологию проверки "разделяй-и-властвуй" для IP мультигигабитного приемопередатчика с перестраиваемой конфигурацией, используемой в FPGA. Методы проверки, повторное использование, аппаратная эмуляция и проверка правильности смешанного сигнала раскрыты, чтобы показать, как эффективно IP проверяется перед запуском на конвеер. Преимущества представленной методики включают всестороннее тестовое покрытие, повторное использование тестов в моделированиях чипа, аппаратная эмуляция и использование в лаборатории, улучшенная эффективность проверки.

Биография Автора

Ning Xue в настоящее время является старшим членом технического персонала в Корпорации Altera, специализирующейся в разработке последовательных интерфейсов ввода-вывода. Ning имеет более чем 10-летний опыт в проектировании кристаллов и проверке, включая урочную работу LSI Logic и Ciena прежде, чем прийти в Altera. Он получил свою степень магистра наук электротехнике и проектировании ЭВМ от Университета Иллинойс в Urbana-Champaign, и свою степень бакалавра в электротехнике и информатике от Университета Калифорнии в Беркли. Ning имеет шесть предоставленных патентов и дополнительные патенты, находящиеся на рассмотрении, опубликованные технические работы.

Введение

Поскольку технологические планы спускаются к крайнему глубокому уровню сабмикрона - процессу на 90 нм и меньше - экспоненциальное увеличение стоимости маски сильно влияет на стоимость непериодической разработки. Чтобы уменьшить разовые затраты и снизить риск разработки дизайна, все больше клиентов предпочитает решения на основе ПЛИС. Растущий потребительский также «разжигался» потребностью во внедренном высокоскоростном последовательном решении на чипах ПЛИС. Учитывая естественную программируемость чипов ПЛИС, эти ядра высокоскоростного последовательного интерфейса должны поддерживать множественные протоколы и работать на скоростях в пределах от 622 Мбит до 6.375 Гбит.

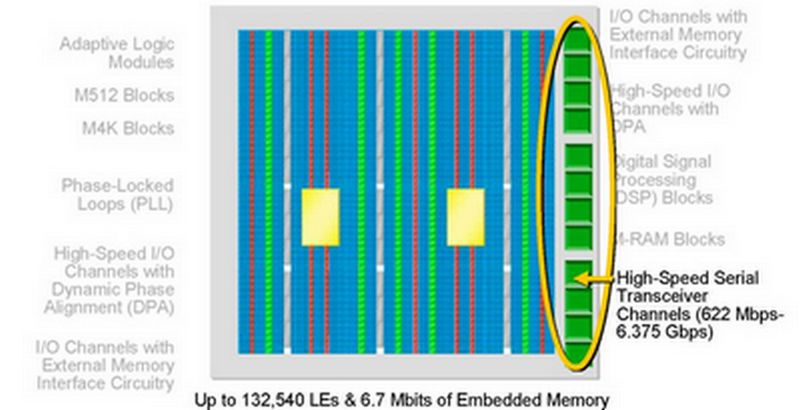

Рисунок 1 — Архитектура Stratix II GX FPGA

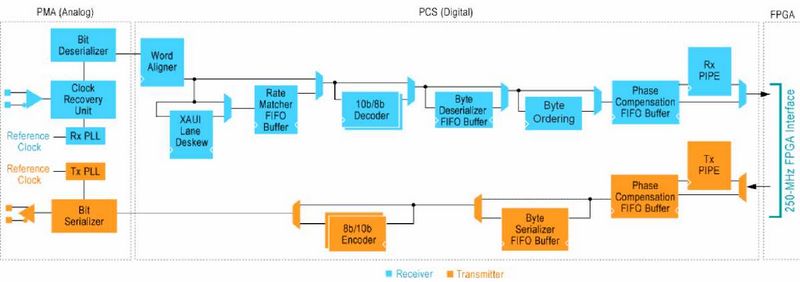

Каждый канал высокоскоростного последовательного интерфейса работает на скоростях от 622 Мбит до 6.375 Гбит. Stratix II GX FPGA поддерживает широкий диапазон стандартов и протоколов, таких как PCI Express, CEI 6G, 10G Ethernet XAUI, Gigabit Ethernet, SONET/SDH, serialLite II и заказные частные протоколы. Блок-схема одного канала высокоскоростного последовательного интерфейса показана на рисунке 2.

Рисунок 2 — Блок канала высокоскоростного последовательного интерфейса

Есть два основных конкурирующих подхода к комплексной проверке реконфигурируемого IP. Во-первых, есть много поддерживаемых протоколов. Канал высокоскоростного последовательного интерфейса должен быть испытан, чтобы быть совместимым с каждым из них. Во-вторых, ПЛИС за его гибкость, дающую возможность пользователям настроить их дизайны. В дополнение к соответствию требованиям клиента IP высокоскоростного последовательного интерфейса должен предоставить параметры настройки клиентам, чтобы разрешить разногласия между спецификациями. Вопрос того, как проверить правильность всех поддерживаемых протоколов и большой набор комбинаций выбираемых возможностей с перестраиваемой конфигурацией представляет соревнование в планировании ресурсов и соответствии времени вывода изделия на рынок.

Эта работа представляет методологию проверки, чтобы балансировать сложность проверки, охват и эффективность. Процесс проверки сосредотачивается на IP приемопередатчика. Проверка строения ПЛИС не покрыта в этой статье. Для удобства термин "уровень чипа" использован в следующих разделах. Он представляет иерархию, где аналоговые и цифровые блоки IP приемопередатчика объединены.

Традиционная Методология Проверки

Традиционный метод проверки IP - ориентированный на моделирование, восходящий подход. Аналоговые и цифровые блоки проверяются в отдельных потоках.

Проверка цифровых блоков запускает на уровне модуля RTL. Испытательные стенды для тестирования модуля прежде всего создаются для исчерпывающего тестирования всех особенностей этого модуля. После того, как все тесты модуля закончены, модули объединяются к уровню кристалла, и проверка также продвигается до уровня кристалла. Снова, испытательные стенды создаются для исчерпывающей проверки особенностей в чипе. После синтеза и «размещение элементов и трассировки соединений», тесты уровня логического вентиля постсхемы размещения запускаются вторично с синхронизацией на уровне кристалла, снабженная комментариями. В пределах аналоговой области SPICE или SPICE-подобное моделирование выполняются перед и после схемы размещения. Как только аналоговые и цифровые блоки совмещены, несколько тестов выполнены на верхнем уровне.

Традиционный процесс проверки налагает много ограничений.

Во-первых, тесты и на уровне модуля и на уровне чипа часто составляются под давлением времени вывода нового изделия на рынок. Возможные дефекты кристалла остаются необнаруженными до постановки изделия на конвейер.

Во-вторых, IP высокоскоростного последовательного интерфейса имеет сотни программируемых пользователем особенностей, приводящих к огромной комбинации конфигураций на уровне кристалла. Чтобы проверить эти особенности на уровне кристалла, испытательные стенды были бы очень сложны и проверочные устройства необычно интеллектуальны. Поддержание качества такой сложной испытательной среды занимает время и может урезать время, затрачиваемое непосредственно на дизайн.

В-третьих, в среде моделирования RTL метастабильность не продумывается. Дрожание фазы тактового генератора не включается легко в испытательную среду даже при том, что модель высокого уровня может быть создана, чтобы подражать дрожанию фазы на испытательном вводе [1].

Наконец, время выполнения моделирования - проблема, особенно в SPICE моделированиях, тестах PRBS и тестах связанных с тактовой частотой.

Традиционная методология проверки также изолирует проверку правильности аналоговых и цифровых блоков системы смешанного сигнала друг от друга. Аналоговый дизайн и цифровой дизайн сопровождаются различными дизайнами и потоками схем размещения, они проверяются отдельно и затем совмещаются в один кристалл. Аналоговый дизайн проверяется в SPICE-подобных моделированиях, в то время как цифровой дизайн моделируется в RTL. На уровне кристалла традиционная методология моделирования смешанного сигнала требует преобразований цифровых блоков в список соединений SPICE и моделирует аналоговый и цифровой блоки в SPICE. Время выполнения очень долгое. Поэтому, традиционно только некоторые аналоговые и цифровые совмещенные тесты могут быть закончены перед выводом изделия на конвейер.

Очевидно, что традиционная методология проверки не является подходящей для проверки этого IP высокоскоростного последовательного интерфейса.

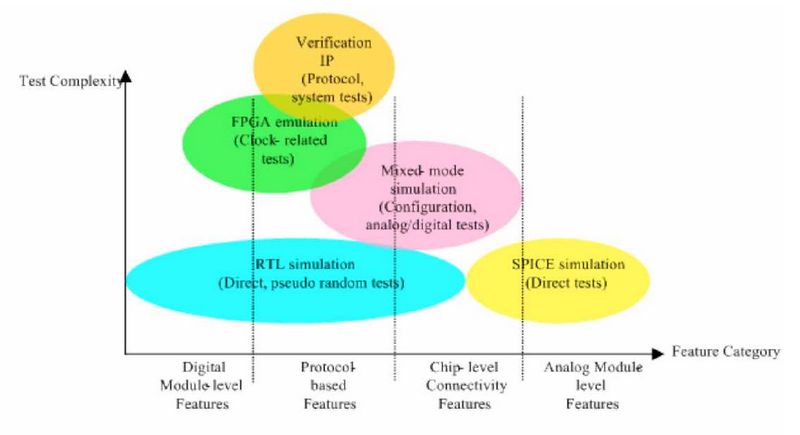

Рисунок 3 — Подход функциональной проверки "Разделяй-и-Властвуй". Стоимость, чтобы проверить этот мультигигабитный приемопередатчик с перестраиваемой конфигурацией состоит из заданных порядком величины стоимостей дизайнов.

Рисунок 3 отображает подход "Разделяй-и-Властвуй". Перемещаясь по горизонтальной оси, модули приобретают увеличенное аналоговое информационное наполнение и следовательно средняя часть горизонтальной оси есть смешанный сигнал с равными долями аналоговой и цифровой части. Сложность тестов по вертикальной оси увеличивается как область видимости расширяется, чтобы включать системные особенности уровня и взаимодействия.

Прямые тесты применены в блочном уровне – где они являются или блоками RTL или принципиальной электрической схемой. Эмуляция ПЛИС покрывает системный уровень включения питания и сброса, а также проверку наложения зон тактовых частот, в дополнение к основной функциональным операциям. Проверки IP добавляет последний уровень проверки и уверенности, проверяя взаимодействие IP в фактической среде системного уровня.

Следующие разделы описывают подход более подробно:

A. Режимы Конфигурации

Этот первый раздел имеет дело с уникальными особенностями конфигураций ПЛИС с внедренными аппаратными ядрами IP.

Б. Проверка Протокола

В разделе описана проверка аппаратных ядер IP в среде системного уровня.

В. Эмуляция Для Проверки

Стратегии эмуляции, которые работают и описаны

Г. Тесты объединенных в одно целое аналоговых и цифровых частей.

Побуждения для усилий по моделированию смешанного сигнала - ключевой компонент проверки IP приемопередатчика - выделены.